- •Классическая арх-ра эвм. Принципы фон Неймана.

- •Магистрально-модульный принцип организации эвм. Принцип открытой арх.

- •Микропроцессоры, алгоритм р-ты микропроц-ра (м/п), стр-ра и основные ф-ции.

- •Жесткий диск.

- •Компакт диски cd.

- •Устр-ва вывода инф-ии.

- •Логические эл-ты эвм.

- •Одноразрядный полусумматор и полный сумматор, триггер.

Логические эл-ты эвм.

В алгебре логики символы обозначаются высказываниями. Высказывание- это любое замечание, утверждение о реально существующем мире. Высказывание может совпадать или не совпадать с действительностью, т.е. быть истинным или ложным. Высказывания являются двоичными ф-ми, к-ые наз-т ЛОГИЧЕСКИМИ (булевыми). Для задания качества высказывания используют символы: 0-Л, 1-И.

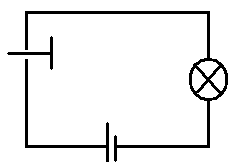

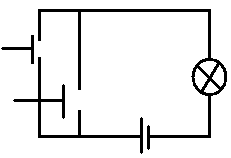

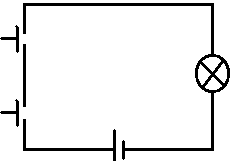

Логический эл-т – это электронное устр-во, реализует логическую операцию. Проиллюстрирует работу логич эл-та на простых электрич схемах. Эл сеть состоит из: ист-ка тока, лампочки, выключателя кнопки.

![]()

Основные логические функции -их наз-ют основными, т.к. они составляют функционально полную схему, с помощью которой можно выразить любую другую ф-ю:

1

Логическое отрицание «НЕ» B=![]()

|

А |

|

|

0 |

1 |

|

1 |

0 |

2 Логическое умножение (конъюнкция, «И») –ф-я имеет значение Ист., тогда и только тогда, когда оба аргумента истинны, во всех остальных случаях –Л.

|

А |

В |

А*В |

|

0 |

0 |

0 |

|

1 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

1 |

1 |

3Логическое сложение (дизъюнкция, «ИЛИ») –ф-я имеет значение Л тогда и только тогда, когда оба аргумента ложны, во всех случаях ее значение И.

|

А |

В |

А*В |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

1 |

1 |

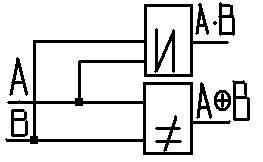

Используя

основные ф-ии можно строить другие

логические ф-ии: «Исключающее ИЛИ» - эта

ф-я И тогда и тглько тогда, когда значения

аргументов равны друг другу.

![]()

|

А |

В |

|

|

Z1 |

Z2 |

C |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

Одноразрядный полусумматор и полный сумматор, триггер.

Сумматор. Посмотрим как сложить 2 одноразрядных 2-чных числа.

|

А |

0 |

0 |

1 |

1 |

|

|

+ |

+ |

+ |

+ |

|

В |

0 |

1 |

0 |

1 |

|

|

00 |

01 |

01 |

10 |

|

|

РС |

РС |

РС |

РС |

С – сумма

Р – перенос в старший разряд

|

А |

В |

С |

Р |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

С=А+В

Полусумматор.

Здесь

не учтён перенос в текущий разряд,

поэтому называют полусумматором. Из

2-х полусумматоров м/о получить полный

сумматор. Получили одноразрядный полный

сумматор. Из него м/о построить сумматор

на любое кол-во разрядов. Сумматор –

это узел арифметико-логического устр-ва.

Здесь

не учтён перенос в текущий разряд,

поэтому называют полусумматором. Из

2-х полусумматоров м/о получить полный

сумматор. Получили одноразрядный полный

сумматор. Из него м/о построить сумматор

на любое кол-во разрядов. Сумматор –

это узел арифметико-логического устр-ва.

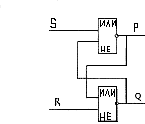

Триггер – это электронная схема для запоминания одного бита инф-ции. Регистры процессора состоят из триггера.

|

А |

В |

Или-не |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

1)подаём на выходы S=1 R=0 (не зависимо от Q)=>P=0=>на выходах нижнего R=0, P=0=>Q=1. 2)перестали подавать сигнал S=0, R=0. На входах верхнего эл-та будет S=0, Q=1=>P=1. На входе нижнего P=0, R=0=>Q=1. Установленное ранее состояние сохраняется. 3)подача сигнала S=0, R=1=>Q=0,P=1 значение сохр-ся при снятии сигнала Q- это значение заполненного бита.

|

S |

R |

действие |

Q |

|

1 |

0 |

Запоминание1 |

1 |

|

0 |

1 |

Запоминание2 |

0 |

|

0 |

0 |

хранение |

Заполн бит |