3. Преобразование функциональной схемы

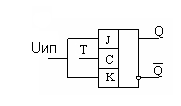

В задании необходимо построить счетчик на D-C(D-V) триггерах. Так как счетчики обычно реализуют на T-триггерах, необходимо сделать некоторые преобразования. Предположим, что нам был дан D-триггер на J-K-триггере, то есть его вход K был присоединен ко входу J с помощью инвертора.

![]()

У берем

инвертор, и подсоединим входы J

и K к питанию, а на вход C

будем подавать импульс T.

Тогда получим асинхронный T-триггер.

берем

инвертор, и подсоединим входы J

и K к питанию, а на вход C

будем подавать импульс T.

Тогда получим асинхронный T-триггер.

![]()

Так как по заданию схема должна быть спроектирована на триггерах с динамическим управлением по заднему фронту синхросигнала, построим ее на двухступенчатых триггерах, реализованных на базе и-не.

4. Анализ работы триггера.

4.1 Параметры логических элементов

Из предыдущего КП возьмем значения размеров транзисторов для логических элементов:

|

Логический элемент |

Ln=Lp |

Wn |

Wp |

|

|

Инвертор |

2 |

4 |

16 |

0.4нс |

|

2 и-не |

2 |

8 |

16 |

0.4нс |

|

2 или-не |

2 |

4 |

32 |

0.2нс |

|

3 и-не |

2 |

12 |

16 |

0.3нс |

В данной схеме на триггер сигнал поступает только после переключения предыдущего (за исключением первого триггера). Тогда максимальная задержка каждого триггера будет примерно

tзд=T/6 tзд =10нс/6=1.6(6)

tф =tср 1нс

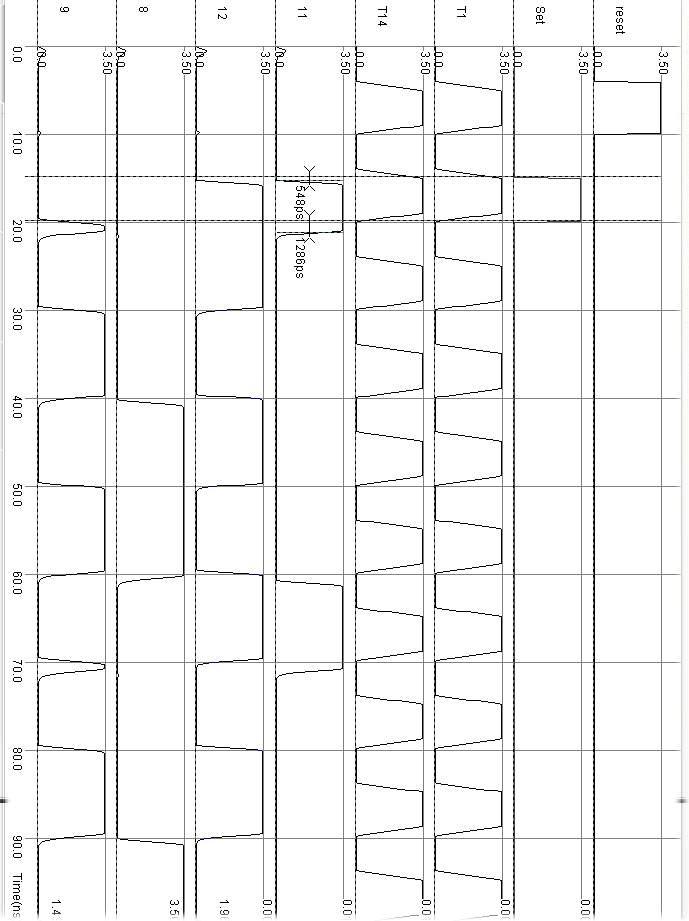

Результаты работы схемы триггера, разработанной в программе Orcad :

tзд01=1.6 нс tзд10=1.7 нс tзд ср =1.65 нс tф =0.7 нс tср=0.8 нс

Эти результаты не удовлетворяют требованиям, поэтому увеличим шины транзисторов:

|

Логический элемент |

Ln=Lp |

Wn |

Wp |

|

Инвертор |

2 |

6 |

23 |

|

2 и-не |

2 |

12 |

23 |

|

2 или-не |

2 |

6 |

46 |

|

3 и-не |

2 |

18 |

23 |

Получаем следующие времена задержек:

tзд01=1.6 нс tзд10=1.1 нс tзд ср =1.35 нс tф =0.5 нс tср=0.5 нс

На рисунках далее изображены схема триггера, смоделированная в программе Orcad и результаты ее работы.

5. Результаты работы устройства (без учета паразитных емкостей и сопротивлений)

tзд01=3.3с tзд10=3.2нс tзд ср =3.25 нс tф =0.78 нс tср=0.91 нс

Все параметры устройства полностью удовлетворяют начальным условиям.

tф = tср 1 нс tзд < 10 нс

На рисунках далее изображены результирующая схема устройства, смоделированная в программе Orcad и результаты ее работы.

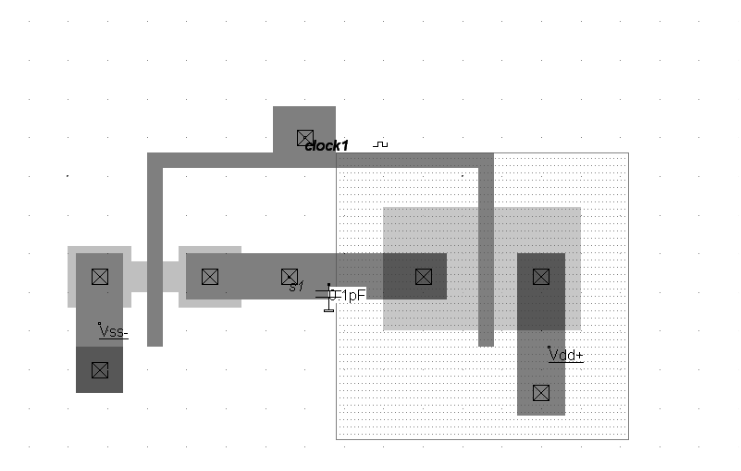

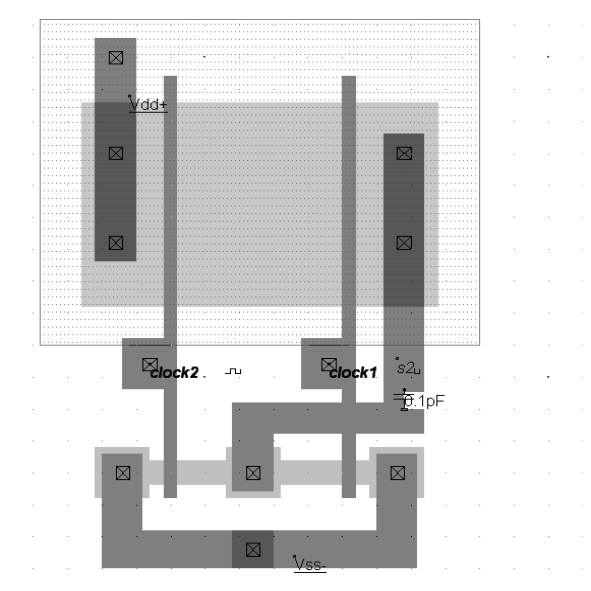

6.Топологическое проектирование

6.1 Топология элементов

И нвертор 2и-не

нвертор 2и-не

2или-не 3или-не

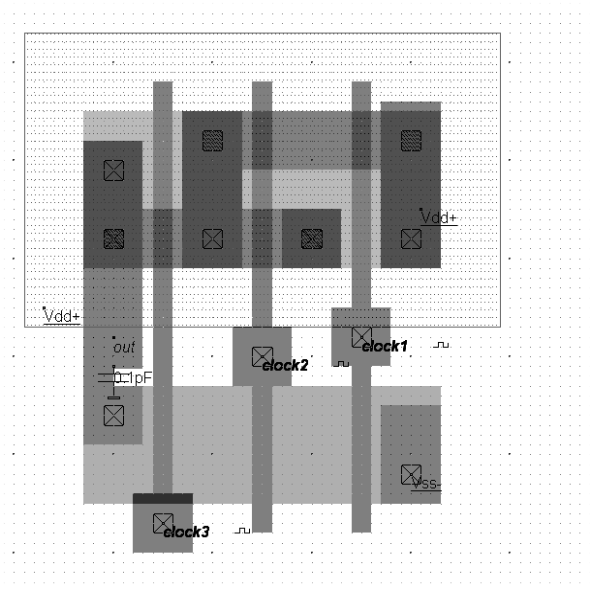

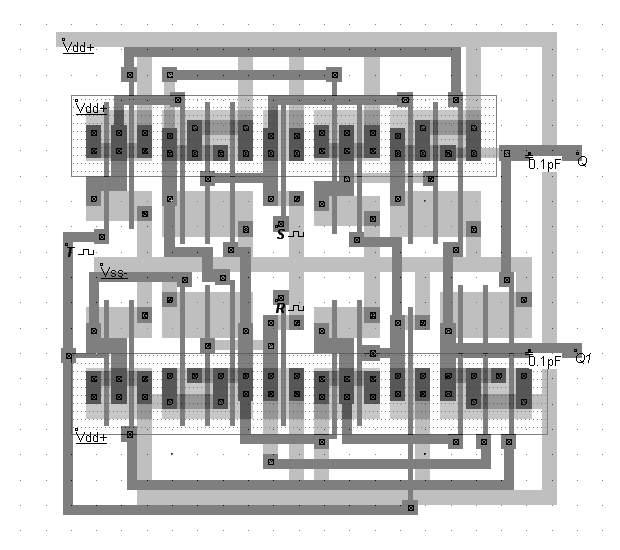

6.2 Топология триггера

6.2.1 Результат работы триггера в программе Microwind

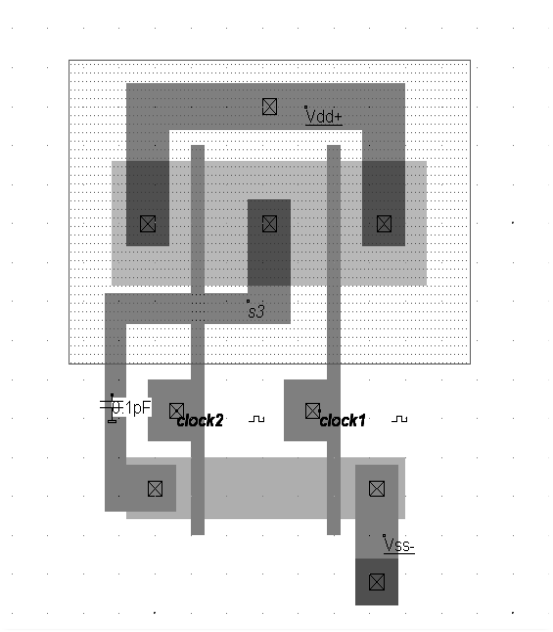

6 .3

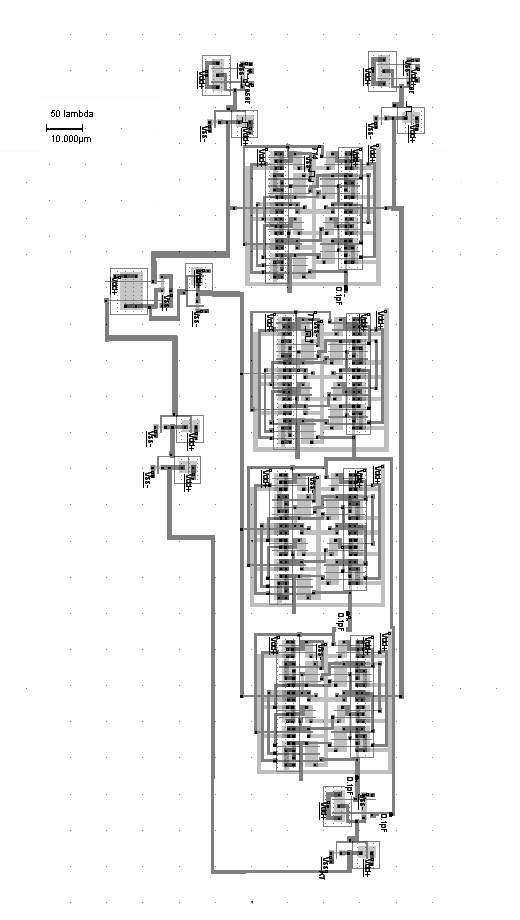

Топология устройства

.3

Топология устройства

6.3.1 Результаты работы схемы в программе Microwind