Курсовые / Курсовые (ЭКТ) / все(from Trix)

.docМосковскии институт электронной техники

Курсовая работа по

Интегральной схемотехнике

Выполнил

Студент гр. ЭКТ-32

Муханюк Н.Н

Задание на кусовую работу.

Сформировать цифровую схему на основе биполярных транзисторах, изгатовленных по технологии L=0.10 .

Заданте на транзисторы L (длина канала)=0.10

W (ширина канала)=0.5

1)В среде microwind получаем нетлист с n и p канальнрыми транзистороми ,используя high speed модели

пример модели :

MODEL N NMOS

+LEVEL=3

+VTO=0.25

+U0=0.060

+TOX= 3.0E-9

+LD =0.008U

+THETA=0.300

+GAMMA=0.400

+PHI=0.150

+KAPPA=0.200

+VMAX=130.00K

+CGSO=100.0p

+CGDO=100.0p

+CGBO= 60.0p

+CJSW=240.0p

+ W= 0.50U

+L= 0.10U

* high speed

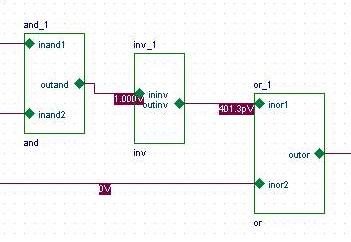

2)В среде Orcad выполняем сборку логических элементов:

или-не , и-не , инвертор и общую схему ,используя ранее полученные модели .

3)По максилальному пути получаем максимальную задержку переключения и максилальную рабочую частоту .Сначало без нагрузки ,затем в качестве нагрузочных элементов используем 1,2,4

параллельно включенных инверторов .

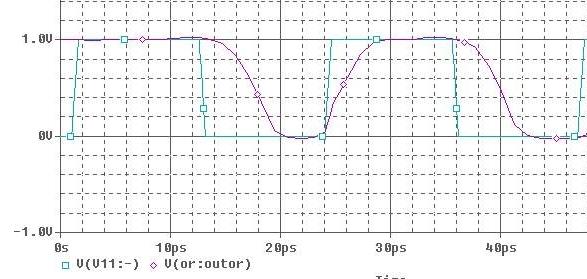

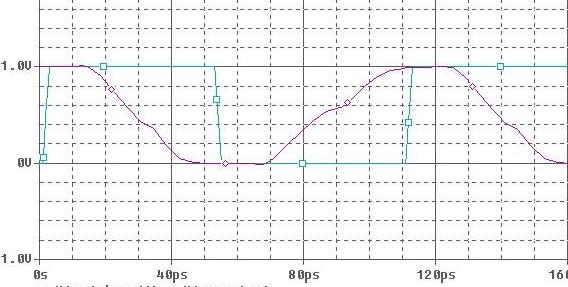

Для случая ненагреженной схемы получаем

З адержка

переключения из 0-1 T(01)=17ps

адержка

переключения из 0-1 T(01)=17ps

Задержка переключения из 1-0 T(10)=13ps

Средняя задержка T=15 ps

Pабочая частота при этом Y=43.48Ггц

Для случая одного инвертора

Задержка переключения из 0-1 T(01)=19ps

Задержка переключения из 1-0 T(10)=19ps

Средняя задержка T=19 ps

Pабочая частота при этом Y=26.32Ггц

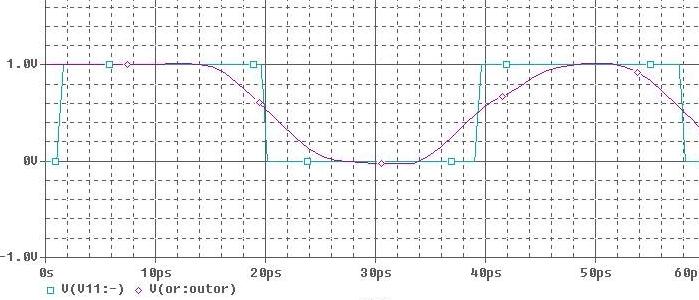

Для случая двух инверторов

Задержка переключения из 0-1 T(01)=23ps

Задержка переключения из 1-0 T(10)=30ps

Средняя задержка T=26.5 ps

Pабочая частота при этом Y=16.13Ггц

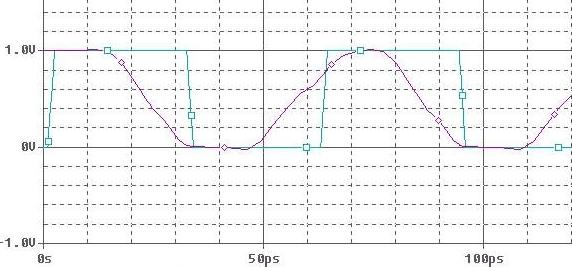

Для случая четырех инверторов

Задержка переключения из 0-1 T(01)=28ps

Задержка переключения из 1-0 T(10)=32ps

Средняя задержка T=30ps

Pабочая частота при этом Y=9.09Ггц

Вывод:

При увеличении числа нагрузочных инверторов увеличиваютсь задержки перключения и уменьшается максимальная частота переклюсения

3)Строим в среде microwind полную топологию схемы .

Транзистор представляет собой две области n или p диффузии (сток ,исток ) между которыми находится слой поликремния выполняющий роль затвора .

Подложку для правилього функционипования транзистора следует подключить к нулевому потенциалу ,а корманы в которых выполняются p канальные транзисторы к наибольшему потенциалу .

Для уменьшения размеров элементов разумно использывать принцип функциональной интеграции.Области одного вида диффузии ,находящиеся под одним потенциалом совмещаются .Совмещаем стоковые и истоковые области и области поликремния ,служашие затворами одной комплиментарной пары.

Для соединения областей одного элемента друг с другом и с соседними областями желательно испоьзывать несколько слоев метализации .Это тоже позволит уменьшить занимаемые элементом обьем а следовательно повысить быстродействие.

Получаем нетлист с учетом паразитных емкостей.

В среде Pspice моделируем полученый нетлист.

Затем , моделируем как и в предыдущем случае с нагрузочные элементы

Этот нетлист для случая одного инвертора.

VDD 1 0 DC 1.00

Vin1 21 0 PULSE(0.00 1.00 0.0N 0.005N 0.005N 0.027N 0.065N)

* MOS devices

MN1 15 21 0 0 N1 W= 0.50U L= 0.10U

MN2 5 1 15 0 N1 W= 0.50U L= 0.10U

MN3 8 5 0 0 N1 W= 0.50U L= 0.10U

MN4 0 8 11 0 N1 W= 0.50U L= 0.10U

MN5 11 0 0 0 N1 W= 0.50U L= 0.10U

MN6 13 11 0 0 N1 W= 0.50U L= 0.10U

MP1 1 21 5 1 P1 W= 0.50U L= 0.10U

MP2 5 1 1 1 P1 W= 0.50U L= 0.10U

MP3 8 5 1 1 P1 W= 0.50U L= 0.10U

MP4 10 8 1 1 P1 W= 0.50U L= 0.10U

MP5 11 0 10 1 P1 W= 0.50U L= 0.10U

MP6 13 11 1 1 P1 W= 0.50U L= 0.10U

*

C2 1 0 1.898fF\

C3 1 0 1.524fF\

C5 5 0 1.034fF\

C6 1 0 0.203fF\

C7 1 0 0.209fF\

C8 8 0 0.712fF\

C9 1 0 0.209fF\

C10 10 0 0.150fF\

C11 11 0 0.978fF\

C12 1 0 0.209fF\

C13 13 0 0.545fF\

C15 15 0 0.160fF\

C20 1 0 0.077fF\

C21 21 0 0.077fF\

*

* n-MOS Model 3 :

.MODEL N1 NMOS LEVEL=3 VTO=0.35 U0=0.050 TOX= 3.0E-9

+LD =0.008U THETA=0.300 GAMMA=0.400

+PHI=0.150 KAPPA=0.200 VMAX=130.00K

+CGSO=100.0p CGDO=100.0p

+CGBO= 60.0p CJSW=240.0p

.MODEL P1 PMOS LEVEL=3 VTO=-0.35 U0=0.020 TOX= 3.0E-9

+LD =0.008U THETA=0.300 GAMMA=0.400

+PHI=0.150 KAPPA=0.150 VMAX=100.00K

+CGSO=100.0p CGDO=100.0p

+CGBO= 60.0p CJSW=240.0p

.TEMP 27.0

.TRAN 0.01PS 0.10N

.PROBE

.END

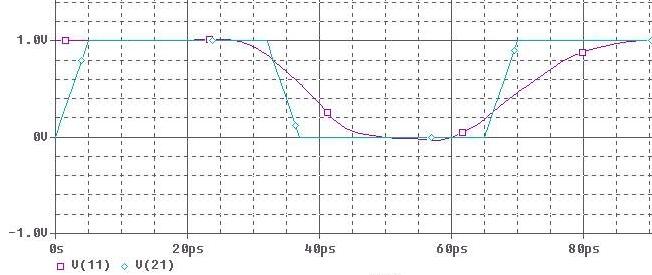

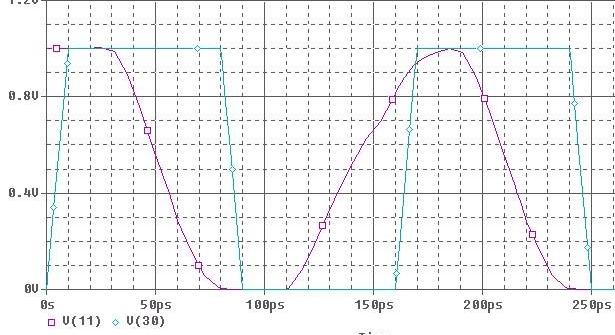

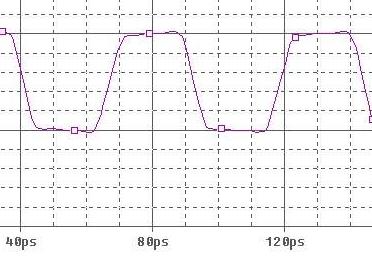

Для ненагруженнои схемы

Задержка

переключения из 0-1 T(01)=33ps

Задержка

переключения из 0-1 T(01)=33ps

Задержка переключения из 1-0 T(10)=40ps

Средняя задержка T=36.5ps

Pабочая частота при этом Y=21.74Ггц

Д ля

одного инвертора

ля

одного инвертора

Задержка переключения из 0-1 T(01)=35ps

Задержка переключения из 1-0 T(10)=36ps

Средняя задержка T=35.5ps

Pабочая частота при этом Y=15.38Ггц

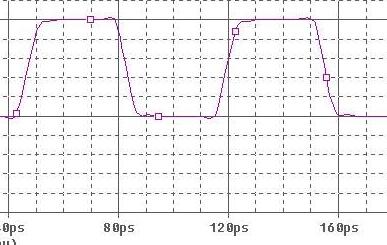

Для двух инвертовов

Задержка переключения из 0-1 T(01)=40ps

Задержка переключения из 1-0 T(10)=41ps

Средняя задержка T=35.5ps

Pабочая частота при этом Y=9.09Ггц

Для четырех инверторов

Задержка переключения из 0-1 T(01)=47ps

Задержка переключения из 1-0 T(10)=54ps

Средняя задержка T=50.5ps

Pабочая частота при этом Y=6.25Ггц

Вывод

Задержки и максимальная рабочая частота уменьшились .Это обьясняется тем ,что в нетлисте полученным на основе топологии присудствуют паразитные элементы задержки ,конденсаторы ,возникающие между метализацией , подложкой , затвороми и областями диффузи .

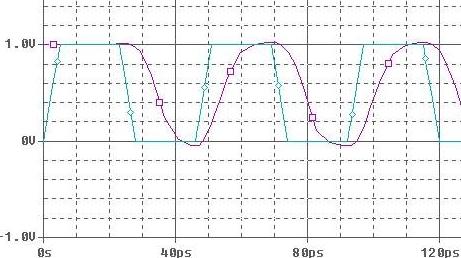

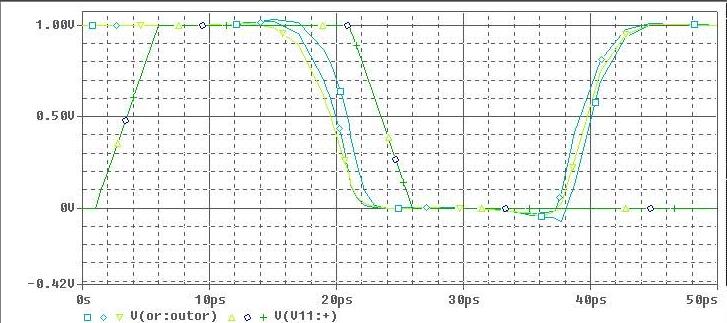

4)Исследуем зависимость быстродействия от температуры

Строим графики зависимости напряжения навыходе от времени при нескольких значениях температуры 0 27 60 С.

Как видно из графика отличие задержек составляет от 0 до 27 примерно 0.4 ps , а от 27 до 60 примерно 1 ps

Это не большое отличие по сравнению с общей задержкой переключения .При более высокой температупе 80С и выше происходит разрушение структуры транзистора .Это можно обяснить тем что при увеличиваетсь число основных носителей заряда и увеличением области оьемного заряда .

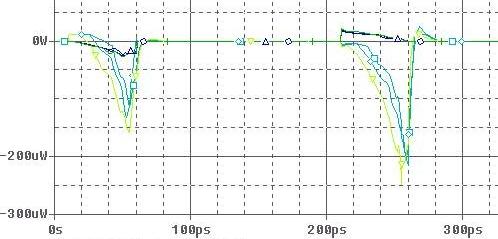

5)Исследуем зависимость потребляемой мощности от темперетуры .

С троим

графики зависимости при различных

значениях температуры .

троим

графики зависимости при различных

значениях температуры .

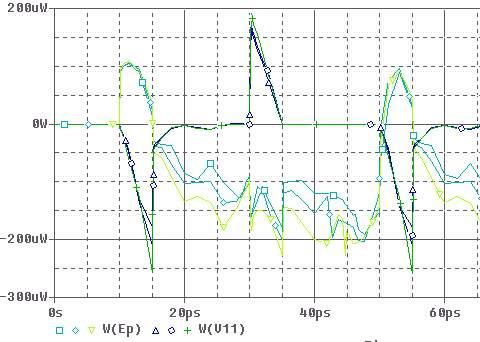

На этом графике представленны мощьности от двух источников от Ep и от преключаемого источника.

Энергия потребляется только в моменты переключеня схемы.

При повышении темпиратуры энергия переключения увеличивается а следовательно и потребляемая от источника мощность

Н екоторое

отличие потребляемой мощности от 0 после

переключения 0-1 можно обьяснить тем

что в структуре присудствуют токи утечек

.

екоторое

отличие потребляемой мощности от 0 после

переключения 0-1 можно обьяснить тем

что в структуре присудствуют токи утечек

.

Мною так же был рассмотрен еще и случай потребляемой мощности при максималльной частоте

Видно что потребляемаяемая мощность увеличисась и полность отсудствует участок с нулевой мощность. Это произошло из-за того что схема находиться в стационарном состоянии молое время .

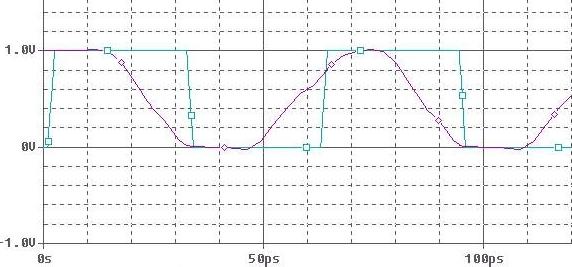

6)Для определения задержек схем используют также метод кольцевого генератора.

Суть его состоит в последовательном соединении нечетного числа инверторов .

Тогда сигнал входяший в первый из них ,пройдя всю цепочку вернется в инверсном вида и.т.д.Тоесть на отдельном взятом инверторе будет происходить постоянное чередование сигналов ,при этом период чередовония будет зависеть от числа инверторов и от их собственной задержки.

Средняя задержка одного определяется как Тср=Т/2N где T период генератора.

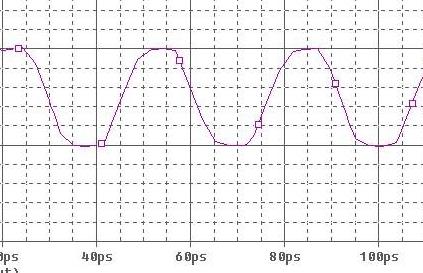

Мы строим генераторы соответственно с 3 5 7 звеньями

Периоды генераторов соответственно 30 53 72 ps

Средние задержки соответственно Tcp 5 5.3 5.14ps

Строиг график зависимости Tcp от числа звеньев