Л.Ю.ШИШИНА

ЛАБОРАТОРНЫЙ ПРАКТИКУМ ПО КУРСУ

“ПРОЕКТИРОВАНИЕ ПОЛУЗАКАЗНЫХ ИС”

МОСКВА 1998

В В Е Д Е Н И Е

Способы проектированиЯ полузаказных и заказных

специализированных ИС.

Для создания высокопроизводительных вычислительных систем с предельными характеристиками по быстродействию и потребляемой мощности требуется разработка большого количества типономиналов специализированных БИС (до нескольких сотен). Оперативность и качество проектирования специализированных БИС тем лучше, чем выше уровень автоматизации этого процесса. Проектирование сложной закàзной специализированной СБИС требует очень больших капиталовложений (миллионы долларов) и занимает много времени (порядка года). Изготовление спроектированной схемы требует гораздо меньших затрат средств и времени (тысячи долларов и 2-3 месяцев соответственно). Результатом проектирования является топология СБИС или более точный современный термин - лэйаут (layout). После долгого и дорогогопроектирования даже одна ошибка схемотехнического, топологического или технологического характера может привести к негодности кристалла, а иногда может и устареть идея проекта к моменту его завершения.

Снизить стоимость проектирования СБИС, увеличить скорость проектирования и повысить уровень автоматизации этого процесса можно, используя следующие методы.

Метод вентильных матриц. Кристалл является матрицей не соединенных между собой одинаковых вентилей (“море вентилей”) или логических заготовок (полуфабрикатов). На исходном базовом матричном кристалле (БМК) формируются электрические связи в соответствии с назначением схемы. Процесс создания лэйаута заключается в соединении матричных элементов 2-я, 3-я или более слоями межсоединений, причем трассировка может быть осуществлена автоматически.

Метод программируемых логических матриц (ПЛМ). Способ проектирования СБИС на ПЛМ аналогичен БМК- проектированию, только есть возможность использования исходного кристалла для электрического перепрограммирования межсоединений. Можно реализовать репрограммируемую схему.

Метод стандартных ячеек (узлов). На кристалле БИС выполняется библиотека стандартных схемных элементов, выполняющих наиболее используемые логические функции. В качестве стандартных элементов могут быть выполнены, например, основные триггеры. На окончательном этапе проектирования СБИС решаются сложные оптимизационные задачи размещения и трассировки. Этот этап может быть автоматизирован при наличии соответствующего программного обеспечения.

Метод кремниевой компиляции. Здесь осуществляется полностью автоматизированный процесс проектирования от задания спецификаций СБИС с учетом электрических и технологических ограничений до получения лэйаута без вмешательства человека. Система проектирования подразумевает полностью автоматическое преобразование с языков высокого уровня в машинные языки. Например, компилятор выполняет проверку корректности и имитационное моделирование исходного описания, преобразует это описание в оптимизированную дизъюнктивную форму, переводит ее в совокупность тактируемых ПЛМ, выполняет размещение и трассировку этих структур на уровне лэйаута, а также производит логическое моделирование (расчет временных характеристик) будущей СБИС. Затраты на кремниевый компилятор компенсируются возможностью проектирования широчайшего класса схем с учетом перспектив развития технологии.

Рассмотрим подробнее, пожалуй, самый распространенный метод проектирования ИС на БМК, для изучения которого имеются определенные программные средства.

ВОСХОДЯЩЕЕ ПРОЕКТИРОВАНИЕ. Пусть требуется разработать БИС на БМК, которая должна быть аналогом некоторого цифрового устройства, ранее разработанного на ИС малой и средней степени интеграции. Иными словами, задана некоторая логическая схема, элементами которой являются корпусные ИС, и на ее основе необходимо разработать логический проект БИС. Задан также БМК конкретного типа. При такой постановке задачи имеем большой объем исходной информации, так как известен в деталях не только алгоритм функционирования проектируемой БИС, но и ее отработанная логическая схема, построенная, правда, на другом элементном базисе. Разработку проекта целесообразно проводить согласно стратегии «снизу вверх», которая достаточно проста в реализации.

Прежде всего нужно создать на ячейках БМК библиотеку функциональных узлов - аналогов корпусных ИС, в затем разработать и отладить логическую схему БИС на основе этой библиотеки. Здесь максимально используется накопленный ранее опыт схемных и функциональных решений, сокращаются сроки и стоимость создания проекта БИС на БМК.

НИСХОДЯЩЕЕ ПРОЕКТИРОВАНИЕ. Стратегия создания логического проекта «сверху вниз» более сложна и трудоемка в реализации, чем разработка по стратегии «снизу вверх», в силу большой неопределенности исходной информации. Применение нисходящего проектирования целесообразно в случае, когда известны только алгоритм функционирования БИС и ее желаемые технические характеристики, а информация о логической структуре отсутствует. Для разработки логической схемы предварительно проводится архитектурное и функциональное проектирование.

Алгоритм нисходящего проектирования включает в себя следующие основные этапы:

разрабатывается архитектура БИС как совокупность функциональных блоков;

каждый блок описывается алгоритмической моделью и проводится моделирование схемы на регистровом уровне. По результатом моделирования уточняются и конкретизируются технические требования для БИС, формирующие требования к блокам, уточняется алгоритм функционирования БИС в целом;

на основе библиотечных ячеек БМК разрабатывается функциональная схема и затем логическая схема БИС. Стратегия нисходящего проектирования предполагает иерархию не только алгоритмических и структурных моделей БИС, но и иерархию тестов для проверки работоспособности ячеек БМК, функциональных узлов, блоков и БИС в целом.

Обе стратегии разработки логического проекта удачно согласуется с блочно-иерархическим подходом, согласно которому структура проектируемой БИС должна разбиваться по функциональному признаку на определенные фрагменты (функциональные блоки и узлы). Проектирование различных по сложности фрагментов можно проводить независимо друг от друга. Таким образом, функционально-логическое проектирование позволяет решить проблему функциональной сложности БИС в целом.

При разработке логического проекта БИС большой объем работ выпадает на его верификацию, которая выполняется с помощью программ функционально-логического моделирования на регистровом и логическом уровнях. Например, с помощью программ функционально-логического моделирования матричных БИС решаются следующие задачи:

Верификация ячеек БМК, типовых функциональных узлов.

Уточнение алгоритма функционирования БИС, ее структуры и спецификаций элементов структуры.

Отладка логической схемы отдельных элементов структуры и БИС в целом.

Отладка функциональных тестов и таблиц логической проверки работоспособности (сокращенно : таблиц проверки работоспособности - ТПР).

Анализ влияния топологии на правильность работы логической схемы.

Оценка устойчивости проекта БИС к воздействию внешних факторов, например, изменению температуры, напряжения источников питания, разбросу технологических параметров.

Повышение адекватности моделирования обычно связано с увеличением затрат машинного времени и необходимого большого объема оперативной памяти, поэтому необходимый и достаточный уровень адекватности моделирования зависит от класса разрабатываемых схем, вида решаемых задач, имеющихся в распоряжении вычислительных ресурсов, возможностей САПР и т.д.

Эффективное решение проблем повышения точности и быстродействия функционально-логического моделирования возможно при использовании программ с регулируемой адекватностью моделирования. В общем случае адекватность и точность моделирования зависит от выбранного метода и алгоритма, используемых моделей сигналов, состава параметров моделей логических элементов, способов учета временных соотношений между сигналами.

Известны различные методы и алгоритмы логического моделирования: синхронные и асинхронные, сквозные и событийные.

По алгоритмам синхронного моделирования осуществляется моделирование логических схем с нулевыми или единичными задержками логических элементов (ЛЭ). Эти алгоритмы обладают высоким быстродействием, но не позволяют получать временные диаграммы работы логических элементов схемы и решать другие задачи, связанные с учетом временных соотношений между сигналами.

Алгоритмы асинхронного моделирования реализуют моделирование с учетом задержек ЛЭ.

В основе событийного моделирования, в отличие от сквозного, лежит обработка процессов только для элементов с изменившимися входными значениями сигналов. Анализ работы цифровых схем показывает, что одновременно в активном состоянии находятся лишь 1 - 10 % всех логических элементов, поэтому событийное моделирование обладает более высоким быстродействием по сравнению со сквозным.

Наибольшее распространение получил алгоритм асинхронного событийного моделирования, соединяющий положительные стороны асинхронного и событийного моделирования.

Л А Б О Р А Т О Р Н А Я Р А Б О Т А № 1.

ПРОЕКТИРОВАНИЕ ЭЛЕМЕНТОВ ИС НА БИПОЛЯРНЫХ БМК ЭСЛ-ТИПА

Цель работы: изучение принципов проектирования фрагментов ИС полузаказного типа на примере БМК многоярусной ЭСЛ - элементной базы.

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

БИПОЛЯРНЫЕ БМК ЭСЛ - ТИПА

На биполярных ЭСЛ БМК можно строить БИС с очень высоким быстродействием: 100-200 пс на вентиль при степени интеграции (10-12)х103 вентилей на кристалле. Потребляемая мощность этих ИС составляет 15-20 Вт . В таблице 1 приведены характеристики некоторых зарубежных ЭСЛ БМК , которые в целом можно охарактеризовать следующими данными:

технологии изготовления используют принципы самосовмещения различных областей структуры, что обеспечивает минимизацию размеров и получения расстояний, например, между базовыми и эмиттерным контактом, меньше топологической нормы ;

уменьшение топологических размеров ( = 1,5 - 1 мкм);

применение щелевой изоляции для активных элементов, при которой шаг размещения транзисторов составляет 5 - 8 мкм;

применение 3 - 4 слоев металлизации, что дает увеличение плотности упаковки вентилей и уменьшение площади кристалла;

использование архитектуры типа «море вентилей» для повышения коэффициента использования вентилей и плотности их упаковки. Отсюда следует снижение задержек сигала в проводниках и рост быстродействия;

использование полимида в качестве межслойного диэлектрика для планаризации поверхности кристалла;

повышение степени интеграции БМК до 10 - 40 тысяч вентилей на кристалле;

уменьшение времени задержки распространения сигнала, измеряемой в режиме кольцевого генератора, до 80 - 150 пс/вентиль;

снижение тока переключения во внутренних ключах до 0,1 - 0,4 мА;

возрастание общей мощности БИС, реализуемых на БМК, до 15 - 20 Вт;

использование в качестве схемотехнического базиса для логических схем 2-х, 3-х ярусных ЭСЛ- схем;

подключение резисторов выходных эмиттерных повторителей внутренних элементов к низковольтному источнику напряжения (например, -2,0 В) с целью экономии мощности;

снижение напряжения основного источника питания для уменьшения потребляемой мощности;

обеспечение совместимости по напряжениям логических уровней со стандартными сериями микросхем (ТТЛ, ЭСЛ, КМДП);

наличие на БМК с большой степенью интеграции входных и выходных буферных схем для согласования логических уровней со стандартными микросхемами;

увеличение числа контактных площадок на кристалле до 300 - 320;

наличие схем диагностики на БМК с большой степенью интеграции.

БМК, как правило, сопровождаются индивидуальными, адаптированными под данный кристалл САПР для разработки схем от схемотехнического и функционального модели-рования до размещения на кристалле и трассировки, генерации контрольных тестов и т.д.

ОПИСАНИЕ ЭСЛ БМК

Для выполнения лабораторной работы рассмотрим пример конкретного ЭСЛ БМК. Матрица рассматриваемого БМК содержит 8 х 9 = 72 типовых ячейки, топологический рисунок которых без металлизации показан на рис .1

На

показанной базовой ячейке реализуется

электрическая схема классического

двухъярусного ЭСЛ- элемента с тремя

входными переменными Х1, Х2, Х3 (рис.2).

Схема формирования опорных напряжений

U1, U2 и

U3

показана на рис.3.

На

показанной базовой ячейке реализуется

электрическая схема классического

двухъярусного ЭСЛ- элемента с тремя

входными переменными Х1, Х2, Х3 (рис.2).

Схема формирования опорных напряжений

U1, U2 и

U3

показана на рис.3.

Двухъярусная

ЭСЛ- схема позволяет реализовать

логические функции сложения 1 , умножения

&

, инверсии и исключающего «ИЛИ» =1 , на

которых можно выполнить схемы высокой

сложности,

например, многоразрядный

сумматор, мультиплексор, дешифратор

кодов операций, регистры хранения

информации, признаков, кодов и другие

регистры, т.е. все составные части

арифметико-логического устройства

(АЛУ). Для реализации этих устройств

необходимо выполнение обязательных

логических функций вида: (R

+

S),

(R

&

S),

(R

S),

(R

+

S

+1),

(R

+

S

+

CI)

è т.д. с учетом всех

переборов сочетаний прямых и инверсных

значений переменных.

Двухъярусная

ЭСЛ- схема позволяет реализовать

логические функции сложения 1 , умножения

&

, инверсии и исключающего «ИЛИ» =1 , на

которых можно выполнить схемы высокой

сложности,

например, многоразрядный

сумматор, мультиплексор, дешифратор

кодов операций, регистры хранения

информации, признаков, кодов и другие

регистры, т.е. все составные части

арифметико-логического устройства

(АЛУ). Для реализации этих устройств

необходимо выполнение обязательных

логических функций вида: (R

+

S),

(R

&

S),

(R

S),

(R

+

S

+1),

(R

+

S

+

CI)

è т.д. с учетом всех

переборов сочетаний прямых и инверсных

значений переменных.

Для примера на рис.4 представлена схема 4- разрядного сумматора с ускоренным переносом в рассматриваемой элементной базе.

Транзисторная структура, используемая в данном БМК показана на рис.5. Перечислим вкратце основные технологические операции для изготовления данной структуры.

Технологический процесс Изопланар-II использует для изоляции компонентов структуры толстый слой окисла кремния SiO2. Применение нитрида кремния Si3N4 позволяет обеспечить самосовмещение при фотолитографии. Уменьшение размеров транзисторов достигается в результате непосредственного примыкания к боковым стенкам изолирующего окисла эмиттерной и базовой областей. Низкое качество изолирующего окисла предполагает небольшую величину напряжения пробоя.

ОСНОВНЫЕ ЭТАПЫ ТЕХНОЛОГИЧЕСКОГО МАРШРУТА

на исходной пластине КДБ-10 (V = 10 Омсм) формируется n+- скрытый слой диффузией сурьмы;

формирование р+- скрытого слоя диффузией бора;

эпитаксия, отжиг, нанесение Si3N4 , глубокое окисление,

создание р+- области контакта к подложке диффузией бора;

формирование n+- ñëîÿ коллекторного контакта диффузией фосфора;

ионное легирование бором р+- базы под маской фоторезиста;

ионное легирование бором пассивной базы и одновременно резисторов активной базы n-p-n-транзисторов;

фотолитография эмиттера и контактных окон к коллектору, отжиг базы;

ионное легирование фосфором эмиттера, отжиг эмиттера,

нанесение Al, фотолитография Ме1;

нанесение межслойного SiO2, фотолитография контактных окон к Ме1;

нанесение Al, фотолитография Ме2.

Таблица 2

Параметры структуры к рис.5.

-

Обозначение

области

Сопротивле-

ние

Размер

Н1 - подложка КДБ

10 Ом см

Н2- n+- скрытый слой

25 Ом/

h = 3.5 мкм

Н3-эпитаксиальная пленка

1,0 Ом см

h = 1.75 мкм

Н4 - р+- скрытый слой

Н5 - изопланар, SiO2

Н6 - n+- коллектор

70 Ом/

xj = 2.2 мкм

Н7 - р+- база

100 Ом/

xj = 0.8 мкм

Н8 - р- база

270 Ом/

xj = 0.85 мкм

Н9 - активная база

xj = 0.8 мкм

Н10 - n+- эмиттер

10-15 Ом/

xj = 0.5 мкм

Н11 - металл 1

0,07 Ом/

xj = 0.6 мкм

Н -контакт к подложке

Толщина окисла межслойной изоляции dок = 0,5 мкм.

Малые размеры транзисторов и тонкие слои структуры позволяют получать в ЭСЛ-схемах на их основе очень высокое быстродействие: fраб n 1 ГГц, времена фронтов и задержки сигналов составляют примерно 1,1 - 0,8 нс при потребляемой мощности Р = 20 МВт.

Введение в электрическую схему двухъярусного ЭСЛ- элемента резистора R12 (рис.5) позволяет понизить величину уровня логической «1» до величины -0,923 В, округляя, в данной работе будем считать:

уровень логической «1» -1 В,

уровень логического «0» - 1,8 В,

величина логического перепада 0,8 В.

Запас помехоустойчивости для таких схем составляет 350 - 450 мВ.

ДОМАШНЕЕ ЗАДАНИЕ

Изучить описание ЭСЛ - БМК.

Определить вариант индивидуального задания (табл.3).

Подготовить варианты электрических схем, эскиз топологии межсоединений, файл входной информации для расчета переходных процессов в схеме.

ЗАДАНИЕ НА ЛАБОРАТОРНУЮ РАБОТУ №1

Для указанного варианта составить электрическую схему на 2-х-ярусных ЭСЛ- элементах, реализующую заданную функцию.

Разработать топологический вариант соединения элементов схемы.

Рассчитать номиналы источников опорных напряжений, используя их при моделировании как внешние источники напряжения.

Рассчитать номиналы резисторов в схеме, зная, что для их изготовления используется область базы с максимальным сопротивлением (см. табл.2), площадь соответствующего резистора определить при помощи раздаточного материала чертежа топологии базовой ячейки (рис.1).

Рассчитать величины паразитных емкостей и сопротивлений шин межсоединений для полученного топологического эскиза схемы. Расчет вести для самых длинных шин, если величины Спар будут меньше 50 фФ, а Rпар - меньше 20 Ом, т.е.

<0,1

пс, то вкладом задержек в шинах разводки

в быстродействие схемы можно пренебрегать.

В ином случае, соответствующие емкости

и сопротивления должны быть включены

в электрическую схему для проведения

моделирования переходных процессов в

проектируемой схеме.

<0,1

пс, то вкладом задержек в шинах разводки

в быстродействие схемы можно пренебрегать.

В ином случае, соответствующие емкости

и сопротивления должны быть включены

в электрическую схему для проведения

моделирования переходных процессов в

проектируемой схеме.При помощи PSPICE рассчитать переходный процесс в полученной схеме, определить время задержки сигнала (или рабочую частоту в схеме).

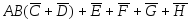

Таблица 3

Варианты индивидуальных заданий

-

№

вари-

анта

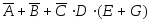

Функция

№

вари-

анта

Функция

1

13

2

14

R S

3

15

4

16

5

R S

17

6

18

7

19

8

20

9

21

10

R+S

22

R+S+C

11

23

12

24

ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ.

Разработать электрическую схему, реализующую заданную в варианте функцию.

На топологическом чертеже базовой ячейки БМК провести карандашом соединения для реализации электрической схемы.

Рассчитать величины сопротивлений в схеме, номиналы источников опорного напряжения.

Рассчитать величины паразитных сопротивлений и емкостей шин полученной топологии. Толщина 1-го слоя металла - 0,6 мкм, 2-го - 1 мкм, толщина межслойной изоляции - 0,5 мкм. Минимальный топологический размер = 1 мкм, минимальная ширина Al- шины - 3. (См. подробнее порядок выполнения работы №3).

Провести расчет переходных процессов в схеме при помощи PSPICE с учетом паразитных сопротивлений и емкостей.

Исходные данные для расчета: UИП = -5.2 В, Up-n = 0.8 В. Параметры моделей транзисторов можно взять из таблиц №3 или №4 во вводном разделе в лабораторном практикуме по схемотехнике аналоговых и цифровых ИС под редакцией В.И.Суэтинова (М., МИЭТ, 1994).

Оформить расчет.

ТРЕБОВАНИЯ К ОТЧЕТУ

Отчет должен содержать:

Название работы.

Краткие сведения об ЭСЛ БМК.

Вариант задания, логическую функцию, электрическую схему, реализующую заданную функцию.

Распечатку файла входной информации для PSPICE.

Распечатку переходного процесса в схеме с расчетом времени задержки сигнала.

КОНТРОЛЬНЫЕ ВОПРОСЫ

Каковы преимущества использования БМК?

В чем суть восходящего и нисходящего способа проектирования?

В чем достоинства и недостатки схем на ЭСЛ БМК?

Какие логические функции можно реализовать на основной базовой ячейке БМК, описанной в данной работе?

Каковы основные требования к топологии электрических соединений в БМК?

Какой способ проектирования проведен в данной лабораторной работе: синхронный или асинхронный, сквозной или событийный?

РЕКОМЕНДУЕМАЯ ЛИТЕРАТУРА

Пономарев М.Ф., Коноплев Б.Г. Базовые матричные кристаллы и программируемые логические матрицы. М., Высшая школа, 1987 г.

Петренко А.И., Лошаков В.Н. Автоматизированное проектирование СБИС на базовых кристаллах.

Мурога С.Г. Системное проектирование СБИС., ч.1, 2. М.: Мир, 1985 г.

Таблица 1

Примеры зарубежных ЭСЛ БМК

|

|

Обозначе-ния |

Число венти-лей |

Задержка, нс/вент. |

Часто та, МГц |

Топо-лог. нормы , мкм |

Число уров- ней ме-талла |

Число контактн. площадок

вх. вых. |

Мощ-ность БМК, Вт |

|

Motoro-la (США) |

MCA10000 ECL MCA7000ECL |

10000

7000 |

0.15

0.15 |

600

1200 |

1.5 |

3

3 |

224 200 |

10-30

10-15 |

|

Fujitsu (Япо-ния) |

ET3000 ET7000H ET4500 ET750 |

3000 10456 4480 1296 |

0.55 0.35 0.55 0.22 |

800 1100 800 800 |

1 |

3 |

120 72 - 120 120 84 48 80 |

6-7

8-10 |

|

NEC (Япо-ния) |

MPI36311 ECL-3 MPB6340 ECL-3A |

1200

4000 |

1

0.7 |

200

300 |

2 |

2 |

88 48

156 72 |

- |

|

AMCC+ Piessev (США) |

Q20166 |

16000 |

0.1 |

1400 |

0.6 |

3 |

- - |

16 |

Л А Б О Р А Т О Р Н Ы Е Р А Б О Т Ы № 2-3

ПРОЕКТИРОВАНИЕ ИС НА БМК КМДП-ТИПА.

Цель работ:изучение распространенных типов МДП-БМК и проектирование с их помощью цифровых логических схем.

Теоретические сведения

БМК представляют собой матрицы однородных или неоднородных ячеек. Однородные ячейки чаще всего используют для схем со степенью интеграции около 1000 вентилей на кристалле (рис.1,а), а неоднородные - для построения БИС с числом вентилей более 10000 и для аналогово-цифровых устройств (рис 1,б).

Элементы интерфейса располагаются на периферии кристалла, правда в последнем случае элементы для формирования аналоговых сигналов могут располагаться и внутри матрицы функциональных элементов.

однородные

ячейки

однородные

ячейки

для функциональных

элементов

строки входных буфе-

ров

ров

столбцы

выходных

столбцы

выходных

буферов

периферийные области с элементами интерфейса

а) б)

Рис.1. Организация матриц БМК с однородными (а) и неоднородными (б) ячейками

По всему полю матрицы БМК могут быть расположены внутренние ячейки интерфейса, которые нужны для повышения нагрузочной способности логических элементов, для связи с внешними устройствами и для контроля работоспособности устройства с помощью тестов.

Для тестирования цифровых БИС требуется большое число контактных площадок: до 200 штук, поскольку это весьма затруднительно при заданных технологических ограничениях, часть элементов интерфейса приходится располагать на поле основной матрицы. С помощью внутренних элементов интерфейса можно решать также задачи приближения буферов к элементам информации, уменьшив тем самым длину соединительных шин и ее паразитную емкость, оказывающую значительное влияние на быстродействие маломощных логических элементов.

Базовый матричный кристалл представляет собой матрицу из n строк и m столбцов. Эти числа могут быть по величине от 5 до 103-4.

Наибольшее распространение при создании библиотечных ячеек (узлов) в БМК получили два варианта:

На основе элемента матрицы формируется один логический элемент: инвертор, одновходовой или двухвходовой вентиль И-НЕ(2И-НЕ) или ИЛИ-НЕ(2ИЛИ-НЕ). Для реализации сложных логических функций используются математические (булевские) преобразования и несколько ячеек матрицы.

На основе элементов матрицы формируется любой законченный функциональный узел, из них составляется некоторый библиотечный набор.

Первый способ позволяет получить более высокий коэффициент использования ячеек и площади базового кристалла, таким образом повышается степень интеграции БИС. Однако, для размещения узлов и трассировки коммутационных проводников требуется мощная система автоматизированного проектирования (САПР), процесс проектирования упрощается, если используется библиотека функциональных элементов.

Второй способ построения ячеек базового кристалла позволяет упростить САПР, однако, если в проектируемой БИС много простых функциональных элементов с низким коэффициентом использования площади кристалла, то снижается и степень интеграции всего устройства. Этот метод проектирования применяется при разработке нерегулярных ИС средней степени интеграции и стандартных БИС: ОЗУ, АЛУ, ПЗУ, ПЛМ и т.д.

Конструкции БМК и расположение структур ячеек должны быть выполнены с учетом необходимости прокладки трасс межсоединений и шин питания. В простейших случаях между ячейками матрицы выделяется свободная площадь, в пределах которой реализуются соединительные проводники. Пропускная способность полосы может составлять от 5 до 15 шин. В пределах таких полос располагаются элементы «подныривания» для реализации пересечений ортогональных проводников.

Особенности БМК накладывают ограничения на проектирование функциональных узлов (макроэлементов)

однотипность транзисторов по топологическим размерам,

ограничения по трассировке между элементами,

необходимость топологической привязки элементов к соответствующему типу каналов транзисторов,

разводка элементов должна учитывать особенности топологического размещения (стыковка по размерам) как не связанных между собой по функциональному назначению блоков, так и единых в некотором законченном устройстве (например, дешифраторы и накопители в ПЗУ),

степень интеграции БМК и перечень макроэлементов.

Библиотечные наборы функциональных элементов.

В микроэлектронике существует рад широко используемых логических схем различной сложности. Прежде всего, это простейшие инверторы, двух-, трех- входовые схемы логического сложения и умножения, схемы комбинированных логических операций, например, И-ИЛИ-НЕ типа, -типа, а также большое число стандартных триггеров (R-S, D-, T-, J-K, D-C, T-V и т.д.). На базе таких логических элементов можно легко построить более сложные триггеры, регистры, счетчики, делители, полусумматоры, мультиплексоры, щифраторы и дешифраторы, усилители и т.д. Любые виды перечисленных схем могут составить библиотечные наборы заданной конфигурации.

Топологический чертеж каждого фрагмента библиотеки (узла) разрабатывается на основе структуры одной или нескольких библиотечных ячеек с учетом заданных координат входов и выходов, возможных последующих соединений данного узла с соседними элементами, а также с шинами питания.

Библиотечные элементы (узлы) имеют, как правило, прямоугольную форму, удобную для систем автоматизированного проектирования. Достигается более высокая плотность компоновки библиотечных элементов, если один или оба размера прямоугольников выполняются одинаковыми.

Каждый библиотечный узел характеризуются следующими параметрами: среднее время задержки, потребляемая мощность, абсолютная или относительная помехоустойчивость, величины логических уровней и их перепад, коэффициенты разветвления по выходу и объединению по входу, количество источников питания и требования к их стабильности, возможность реализации логической функции от большего числа переменных. Обобщенным параметром элементной базы БМК служит т.н. фактор качества - произведение потребляемой мощности на среднее время задержки. Величина потребляемой элементом мощности ограничивает степень интеграции быстродействующих БИС.

Составляется аттестационная таблица, в которой перечисляются библиотечные узлы, их индексация и площадь, занимаемая данным элементом (табл.1).

Все библиотечные узлы классифицируются по величине занимаемой площади или пл числу занимаемых ячеек:

L - меньшая часть БЯ,

F - большая часть БЯ,

E - базовая ячейка полностью.

Таким образом, индекс элемента может быть вида 2E1L2, где первая цифра обозначает количество ячеек данного типа, Е1 - тип библиотечного узла, L2 -номер модификации сочетания ячеек данного типа. За единицу измерения площади библиотечного узла принимается площадь базовой ячейки (например, для БМК 1515ХМ1 - S = 180х192 = 34560 мкм2 0,035 мм2).

Таблица 1

Аттестационная таблица логических элементов на БМК серии 1515

-

№

Обозначение

логического

элемента

Вид библиотечного элемента

(узла)

Площадь,

занимаемая

библиотечным элементом

1

L1

Si*-шины через ячейку (2 шт.)

1/3 S

2

L2

2х НЕ

- « -

3

L3

Усилитель (2инвертора)

- « -

4

L4

2-ИЛИ-НЕ

- « -

5

L5

2-И-НЕ

- « -

6

L6

2 последовательно соединенные НЕ

- « -

7

L7

Связка двух ключей

- « -

8

F1

Si-шины через ячейку (4 шт)

2/3 S

9

F2

2 усилителя (по 2 инвертора)

- « -

10

F3

НЕ и усилитель (3 инвертора)

- « -

11

F4

Усилитель (4 инвертора)

- « -

12

F5

2хНЕ и усилитель (2 инвертора)

- « -

13

F6

2х2-ИЛИ-НЕ

- « -

14

F7

2-ИЛИ-НЕ и усилитель (2 инвертора)

- « -

15

F8

2-И-НЕ и 2-ИЛИ-НЕ

- « -

16

F9

2х2-И-НЕ

- « -

17

F10

2-И-НЕ и усилитель (2 инвертора)

- « -

18

F11

3-И-НЕ и НЕ

- « -

19

F12

3-ИЛИ-НЕ и НЕ

- « -

20

F13

НЕ и 3-И-ИЛИ-НЕ

- « -

21

F14

НЕ и 3-ИЛИ-И-НЕ

- « -

22

F15

R, S- триггер

- « -

23

F16

R-S-триггер

- « -

24

E1

4-ИЛИ

S

25

E2

4-И

- « -

26

E3

2х3-И-НЕ

- « -

27

E4

2х3-ИЛИ-НЕ

- « -

28

E5

3-ИЛИ-НЕ и 3-И-НЕ

- « -

29

E6

5-И-ИЛИ

- « -

30

E7

5-ИЛИ-И

- « -

31

1E1L1

D-триггер «защелка» с установкой

4/3 S

32

1E1L2

D-триггер «защелка» с уст. и сбросом

- « -

33

2E1L1

D-триггер с установкой и сбросом

7/3 S

34

3E1L1

JK-триггер с установкой и сбросом

10/3 S

Широкое распространение получили БМК на КМДП-транзисторах с одним слоем алюминия (серия 1515) и с двумя слоями алюминиевой разводки (серия 1537). Рассмотрим подробнее эти два типа БМК.

КРАТКОЕ ОПИСАНИЕ БМК 1515ХМ1.

Матрица данного БМК представляет собой прямоугольник размером 5,7х5,72 мм2. Число базовых ячеек - 299. Общая площадь кристалла составляет 5,8х5,82=33,756 мм2.

Соединения в матрице выполнены при помощи слоев поликремния и алюминия. Первый уровень (Si*) - постоянный, т.е. топологически неизменен. Второй слой (Al) содержит постоянную часть (шины земли, питания, контактные площадки) и переменную для разводки шин межсоединений. Преимущественное расположение поликремниевых шин - горизонтальное, а алюминиевых - вертикальное.

В центральной части матрицы расположены 13 столбцов по 23 базовые ячейки в каждом. Между ячейками расположены горизонтальные Si*-шины для соединения между собой. Между столбцами ячеек можно разместить до 8 вертикальных Аl-шин для соединений во втором уровне.

Базовая ячейка размером 180х192 мкм2 образована 12 транзисторами с индуцированным каналом n- и p-типа, затворы которых объединены попарно, так что в каждой ячейке можно реализовать 6 простейших КМДП-инверторов (рис.2). Ячейка состоит из двух неравных частей: в меньшей - 4 транзистора (по 2 n- и p-типа), а в большей - 8 транзисторов (по 4 n- и p- типа).

Для упрощения выполнения соединений в каждой области истока (стока) транзистора сделано по 2 контактных окна, причем контакт, расположенный ближе к центру ячейки используется для создания библиотечных элементов, а другой контакт - служит, в основном, для соединения библиотечных элементов между собой.

Затворы транзисторов выполнены из поликремния, для удобства контакт к затвору выполнен между сток-истоковыми областями n- и p- канальных транзисторов, а для обеспечения коммутации библиотечных элементов между собой, контакты к объединенному затвору сделаны с обеих сторон базовой ячейки.

В

конструкцию БЯ заложены 2 поликремниевые

шины шириной по 4![]() ,

через БЯ проходятAl-шины

земли и питания шириной по 6

,

через БЯ проходятAl-шины

земли и питания шириной по 6![]() ,

ширина остальных металлических шин

межсоединений - 2

,

ширина остальных металлических шин

межсоединений - 2![]() .

.

КРАТКОЕ ОПИСАНИЕ БМК 1537ХМ2

Данная

БМК содержит 6000 эквивалентных вентилей.

Данный БМК использует в качестве разводки

один слой поликремния и два слоя алюминия.

Для снижения общей высоты барьера

толщина первого слоя алюминия равна

0,6 мкм, а второго слоя - 1 мкм. Минимальный

топологический размер (![]() )

- 1 мкм.

)

- 1 мкм.

Библиотечная ячейка представляет собой 4 нескоммутированных транзистора (рис. 3 ).

ДОМАШНЕЕ ЗАДАНИЕ

Ознакомиться с теоретическими сведениями по проектированию ИС на БМК.

Определить номер варианта индивидуального задания и ознакомиться с его содержанием.

ЗАДАНИЕ НА ЛАБОРАТОРНУЮ РАБОТУ №2

По предложенной в варианте логической функции, используя правила преобразования логических выражений Де-Моргана:

а) реализовать функцию на элементах 2И-НЕ;

б) реализовать функцию на элементах 2ИЛИ-НЕ;

в) реализовать функцию в смешанном базисе И-ИЛИ-НЕ.

Нарисовать структурные схемы полученных трех вариантов реализации функции.

5

5

3

5

1

3

5

1

6

8

9 7

6

8

9 7

2 4

Рис.2. БМК 1515ХМ1. 1- области истока (стока) р-канальных транзисторов, 2 - область р- кармана, 3 - области истока(стока) n-канальных транзисторов, 4 - поликремниевые затворы, 5 - поликремниевые шины, проходящие через ячейку, 6 - шины «земли», 7 - шины положительного питания, 8 - контакты под шиной «земли» к р-карману, 9 - контакты под шиной питания к подложке.

1

1

1

1

3

5

3

5

2

2

2

2

4

4

Рис. 3. Схематичная структура базовой ячейки БМК 1537ХМ2.

контактные области к затворам транзисторов р- типа, 2 - контактные области к затворам транзисторов n- типа, 3 - контактные области к истокам и стокам р- канальных транзисторов, 4 -контактные области к истокам и стокам n- канальных транзисторов, 5 - поликремниевые затворы.

Сравнить аппаратные затраты в полученных вариантах схем: рассчитать число транзисторов в КМДП-базисе.

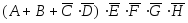

Рассчитать суммарное максимальное время задержки в схемах, если известны времена задержки для каждого элемента:

![]()

Результат расчетов может выглядеть следующим образом:

![]()

Рассмотреть наличие функциональных статических или динамических состязаний для любых двух наборов логических переменных, например:

f = AB+BC+DEFG

A B C D E F G f

0 0 0 0 0 0 0 0 P1

1 0 1 0 0 0 0 0 P2

Статические функциональные состязания при переключении f(P1) f(P2):

f(P1)

f(P2)

f(P1)

f(P2)

f(P1)

f(P2)

.

f(P1)

f(P2)

.

Динамические функциональные состязания, соответственно:

f(P1)

f(P2)

f(P1)

f(P2)

f(P2)

f(P1)

f(P2)

f(P1)

ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

Провести преобразования заданной логической функции.

Провести соответствующие расчеты и внести их в таблицу вида табл.2.

Исследовать возможность возникновения статических или динамических состязаний при определенных наборах логических переменных.

Оформить отчет.

ТРЕБОВАНИЯ К ОТЧЕТУ.

Отчет должен содержать:

Название работы.

Краткий конспект теоретической части.

Рисунки структурных схем 3-х вариантов реализации функции.

Заполненную таблицу вида табл.2. Выделить выбранный лучший вариант.

Таблица 2.

РЕЗУЛЬТАТЫ ВЫПОЛНЕНИЯ РАБОТЫ №2

|

№ вари- анта |

Вид базиса |

Количество транзисторов |

Время задержки

|

Время задержки при

|

|

1 |

2И-НЕ |

|

|

|

|

2 |

2ИЛИ-НЕ |

|

|

|

|

3 |

И-ИЛИ-НЕ |

|

|

|

ВАРИАНТЫ ИНДИВИДУАЛЬНЫХ ЗАДАНИЙ

F = AB + BC + DEFG

ABC + CDE

A (BC + DE) + FG

ABCD + EFGH

ABCDE

A + B + C + D

(A + B + C) D

AB + CD(E + F)

(A + B) (CD + EF)

ЗАДАНИЕ НА ЛАБОРАТОРНУЮ РАБОТУ № 3

Задание выполняется при помощи топологического чертежа КМДП БМК серии 1537 (рис.4).

Провести топологическое проектирование схемы, реализующей заданную в работе №2 логическую функцию с минимальными аппаратными затратами и максимальным быстродействием. Оценить площадь, занимаемую схемой, число используемых базовых ячеек.

Рассчитать величины паразитных емкостей и сопротивлений шин межсоединений для полученного топологического эскиза схемы. Расчет вести для самых длинных шин, если величины Спар. меньше 20 фФ, а Rпар. - меньше 250 Ом (т.е.

),

то вкладом задержек в шинах разводки

в быстродействие схемы можно пренебречь.

В ином случае, соответствующие емкости

и сопротивления должны быть включены

в электрическую схему для проведения

моделирования переходных процессов в

проектируемой схеме.

),

то вкладом задержек в шинах разводки

в быстродействие схемы можно пренебречь.

В ином случае, соответствующие емкости

и сопротивления должны быть включены

в электрическую схему для проведения

моделирования переходных процессов в

проектируемой схеме.

3. Провести расчет при помощи PSPICE переходных процессов в схеме с учетом паразитных RC- составляющих для окончательного топологического варианта схемы.

ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

На топологическом чертеже БМК карандашом провести соединения для реализации электрической схемы. В данном БМК разрешены два слоя металлизации (см. Описание соответствующего БМК). Используемые контактные окна отмечаются, например, крестиком.

Рассчитать емкость и сопротивление наиболее длинной шины, пользуясь следующими данными:

= 1 мкм, минимальная ширина Al- шины - 3,

средняя толщина межслойного изолирующего окисла dок.изол = 0,5 мкм, толщина

слоя поликремния dSi* = 0.5 мкм, толщина 1-го слоя алюминия dAl 0.5 мкм,

а второго (преимущественно для шин питания) - 1 мкм,

поверхностное

сопротивление

![]()

,

,

![]()

.

.

сопротивление шины легко рассчитать, вычислив число квадратов в шине n:

R

= n![]() ,

а емкость - зная полную площадь шины А

= L x W, C = C0 A,

,

а емкость - зная полную площадь шины А

= L x W, C = C0 A,

![]() ,

ок

= 3.9, 0

= 8,8510-14

ф/см.

,

ок

= 3.9, 0

= 8,8510-14

ф/см.

Провести расчет переходных процессов в схеме при помощи PSPICE, подсоединив в соответствующие узлы паразитные R-C-элементы. Исходные данные для расчета:

UИП

=

5 В,

Uпор.n

= 1.2![]() 0.3

В,

Uпор.р

= -(1.3

0.3

В,

Uпор.р

= -(1.3![]() 0.3)

В ,

0.3)

В ,

размеры каналов транзисторов W = 30 мкм , L = 2мкм,

толщина подзатворного SiO2 d.SiO2подзатв = 50 нм.

Входные импульсы логических сигналов могут быть идеальными, с нулевыми фронтами.

Наборы логических значений входных переменных подобрать таким образом, чтобы продемонстрировать наличие функциональных состязаний. Для симметричных схем с одинаковыми длинами цепей прохождения сигналов, состязания можно продемонстрировать при помощи несинхронной подачи входных переменных.

ТРЕБОВАНИЯ К ОТЧЕТУ.

Отчет по данной работе должен содержать:

Топологический чертеж логической схемы.

Результаты расчета паразитных емкостей и сопротивлений. Число использованных базовых ячеек и величину площади схемы (можно в единицах : A = (a х b).

Распечатку файла входной информации для PSPICE.

Распечатку переходного процесса в схеме с расчетом времен фронтов и задержек сигналов.

КОНТРОЛЬНЫЕ ВОПРОСЫ

Что такое «базовая ячейка», «библиотечная ячейка», «библиотечный узел» в БМК, для каких методов проектирования их чаще применяют?

Что такое восходящий и нисходящий способы проектирования ИС на БМК?

Как заполняется аттестационная таблица для БМК определенной серии?

Что такое функциональные состязания статического и динамического типа?

Как учитывать или избегать состязаний сигналов в схемах?

Как спроектировать схему с минимальными аппаратными затратами?

--«---«---»---»-- с максимальным быстродействием?

–«---«---»---»-- с минимальной площадью?

Какой способ моделирования схемы проведен в лабораторной работе:

синхронный или асинхронный, сквозной или событийный?

РЕКОМЕНДУЕМАЯ ЛИТЕРАТУРА

Пономарев М.Ф., Коноплев Б.Г. Базовые матричные кристаллы и программируемые логические матрицы. М., Высшая школа, 1987г.