- •Арифметическо-логическое устройство (алу).

- •Структура алу

- •Организация внутрисекционного переноса в алу

- •Примеры использования алу

- •Классификация имс

- •Обобщённая структура микропроцессора

- •Классификация мп

- •Регистровая алу – базовая структура мп

- •Однокристальное ралу

- •Взаимодействие элементов в ралу

- •Наращивание разрядности обрабатываемых слов

- •Уу на жёсткой логике

- •Построение быстродействующих контроллеров на основе бму

- •Структурные методы повышения быстродействия микропроцессора Временные диаграммы взаимодействия основных узлов микроЭвм

- •Многоуровневая конвейерная обработка

- •Технические средства организации прерываний

- •Структура микроЭвм с блоками прерываний

- •Блок приоритетных прерываний (бпп)

- •Синхронный обмен

- •Реализация обмена информацией с ву, доступными по чтению.

- •Реализация обмена информацией с ву, доступными для записи

- •Реализация обмена с ву по чтению и записи

- •Асинхронный обмен информацией с ву.

- •Структура микропрограммы реализации синхронного обмена

- •Структура микроЭвм с узлом обмена информацией

- •Структурная схема асинхронного обмена со стороны ву

- •Архитектура фон-Неймана

- •Командный цикл микросистемы

- •Структура магистрали

- •Типы структур

- •Конвейерные вс Каноническая структура конвейерного процессора

- •Системы из векторных процессоров (вп)

- •Анализ конвейерных вычислительных систем (квс)

- •Каноническая структура (мп) матричного процессора

- •Анализ мвс

- •Каноническая структура мс

- •Анализ мс

- •Вс с программируемой структурой

- •Транспьютерные вс

- •Вызов процедур

- •Оптимальное использование регистров rg

- •Аппаратный подход к построению рон

- •Программный подход распределения регистрового файла

- •Характерные особенности архитектуры с снк.

- •Конвейерная обработка информации в вычислителях с снк

- •Операции и флаги

- •Структура шины

- •Микропроцессорный комплект к-580

- •Шестнадцатиразрядные процессоры

Регистровая алу – базовая структура мп

Структура автоматически получается из следующего соотношения:

![]()

![]() ,

где

,

где![]() - любая операция

- любая операция

![]() А

иB– операнды.

А

иB– операнды.

![]() Необходимо

выполнить следующие действия:

Необходимо

выполнить следующие действия:

![]() 1.

Поместить операнды А иBна входы АЛУ.

1.

Поместить операнды А иBна входы АЛУ.

![]() 2.

Выполнить операцию в АЛУ.

2.

Выполнить операцию в АЛУ.

![]() 3.

Записать результат операции в элемент

памяти (регистр С).

3.

Записать результат операции в элемент

памяти (регистр С).

Указанные далее элементарные предельные операции называются микрооперациями (МО). Для того, чтобы структура МП была бы работоспособна необходимо дополнительно решить 2 задачи: задачу синхронизации и задачу управления.

Задача синхронизации – фиксация в памяти достоверного результата.

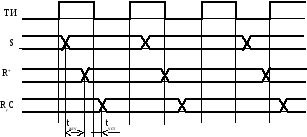

В минимальном объёме задача управления заключается в следующем: формирование управляющего слова, задающего тип операции в АЛУ, формирование сигналов, определяющих режим работы регистров (хранение или запись). Задача синхронизации заключается в том чтобы выработать тактовые импульсы, обеспечивающие фиксацию результатов в регистры в тот момент времени, когда на их входах присутствует достоверная информация. Условимся, что формирование управляющего слова будем осуществлять по переднему фронту тактового импульса, а фиксацию – по заднему фронту ТИ.

Для того чтобы использовать данную структуру в качестве МП, необходимо выполнить следующие требования:

Обеспечить приём, хранение и использование результатов промежуточных операций для организации последовательности вычислений.

Обеспечить приём информации от внешних устройств.

Обеспечить выдачу информации на внешние устройства.

Этим требованиям удовлетворяет следующие структуры

Б)

А) Для сопроцессора

Б) Для видеопроцессора

Сравнение проводится по:

а) аппаратные затраты

б) временные характеристики выполнения требуемой операции.

По а) оба варианта приблизительно одинаковы. Различие заключается в том, что в варианте а) более сложное устройство дешифрации адреса регистров общего назначения (РОН).

По б)

Следовательно в таком типе время на совершение операции и записи требуется один такт Т.

В случае выполнения операции с размещением результата в РОМ более предпочтительным является вариант А, т.к. из-за наличия регистра С в варианте В времени требуется в 2 раза больше.

Приём информации от внешних устройств в обоих вариантах аналогичен, т.о. временные диаграммы не строим.

Передача информации на внешние устройства. ВУ – это длинная линия с ёмкостной, индуктивной и … нагрузками и поэтому используется 2 такта для передачи в ВУ (А). В случае В можно хранить в регистре С информацию и одновременно принимать информацию в регистры А и В.

При обмене информацией с ВУ более приоритетным является вариант В, т.к. в варианте А необходимо сохранять информацию в регистрах А и В в течение двух тактов из-за того, что для получения достоверной информации на входах внешних устройств длительности одного такта как правило недостаточно из-за длинной линии связи между МП и ВУ. В варианте В благодаря регистру С информация в регистрах А и В хранится только 1 такт, а во втором такте мы можем принимать новую информацию.

РгС АЛУ РгВ РгА РгС

РгХ К

ВУ С S С С

а) б)

Эта структура лишена недостатков вышеуказанных структур, но она имеет свои недостатки: большие аппаратные затраты за счёт введения дополнительного регистра полностью идентичного регистру С. Для того чтобы использовать данную структуру должна быть сформирована инструкция, которая содержит:

тип операции;

источники операндов;

приёмники результата;

способ определения следующей инструкции (прямая и косвенная адресация).

Инструкция, включающая в себя все вышеуказанные микрооперации называется микрокомандой.

Регистровая АЛУ разрядно-модульного типа.

Секционированный МП.

Условимся, что все элементы этой структуры – четырёхразрядные

Рг2 – сдвиговый регистр

ISR – сдвиг вправо

ISL – сдвиг влево

OSL – выход информации при сдвиге влево

OSR – выход информации при сдвиге вправо

MS обеспечивает приём информации в Рг1 либо от внешнего устройства, либо от внутрисистемной шины.

Информационные сигналы:

входные – от ВУ, Р0, ISL, ISR

выходные к ВУ, Р4, F11, D11, OSR, OSL

Сигналы управления:

Цель синхронизации (С) – зафиксировать достоверный результат в памяти.

Для дальнейшего использования этой структуры необходимо решить 2 задачи:

определить способ наращивания разрядности обрабатываемых слов;

определить набор операций, реализуемых РАЛУ.

РОН, АС, R1 увеличивают свою разрядность пропорционально количеству секций, спользуемого при построении ВУ.

R2, АЛУ – требуются для увеличения разрядности определённых связей связей по сдвину и переносу. Управляющие сигналы на все секции процессор поступают параллельно, а информационные – последовательно.

Формирование набора микроопераций, кодирование, простейшие микропрограммы

|

№ |

Операция |

Обозначение |

АДР |

А |

W/R |

S3 |

S2 |

S1 |

S0 |

M |

V0 |

V1 |

V2 |

V3 |

P0 |

|

1 |

Передача содержимого регистра 1 в РОН с адресом Ак |

(Рг1)РОН-Ак |

Ак |

* |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

* |

|

2 |

Выполнение арифметических или логических операций над содержимым регистров Рг1 и Рг2 с размещением результата в РОН с адресом Ак и АС |

(Рг1)[S;M;P0] (Рг2)РОН-Ак, АС |

Ак |

* |

1 |

S3 |

S2 |

S1

|

S0 |

M |

0 |

0 |

0 |

1 |

* |

|

3 |

Передача информации от ВУ в Рг1 |

(ВУ)Рг1 |

* |

1 |

* |

* |

* |

* |

* |

* |

1 |

0

|

0 |

0 |

* |

|

4 |

Запись информации из РОН с адресом Ак в Рг1 и Рг2 |

(РОН-Ак)Рг1, Рг2 |

Ак |

0 |

0 |

* |

* |

* |

* |

* |

1 |

1 |

1 |

0 |

* |

|

5 |

Сложение содержимого РОН с адресами Аn и Am с размещением результата в РОН с адресом Ак |

(РОН-Аn)Рг1 (РОН-Аm)Рг2 (Рг1)плюс (Рг2)РОН-Ак |

Аn

Аm

Ак |

0

*

* |

0

0

1 |

*

*

1 |

*

*

0 |

*

*

0 |

*

*

1 |

*

*

1 |

1

0

0 |

0

1

1 |

0

1

0 |

0

0

0 |

*

*

P0 |

Если пришла микрокоманда, то не обязательно, что АЛУ учавствует в её выполнении.

Основное правило составления микрокоманд и микропроцедур.

Содержимое регистров, которые не учавствуют в выполнении команды или данной микрокоманды должно быть сохранено или восстановлено, если без искажения данных регистр выполнит команду или микрокоманду не представляется возможным. Таким образом формируется полный набор микрокоманд (МК), которые используются для:

написания программ ВУ, в которых требуется максимальное быстродействие (специализированные ВУ);

разработки системы команд в виде микропрограмм и макрокоманд:

а) директивная система команд

б) система команд, формируемая разработчиком.