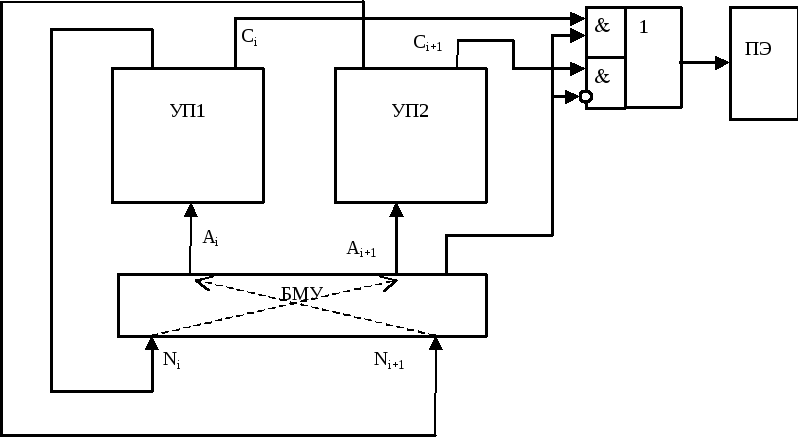

Структурные методы повышения быстродействия микропроцессора

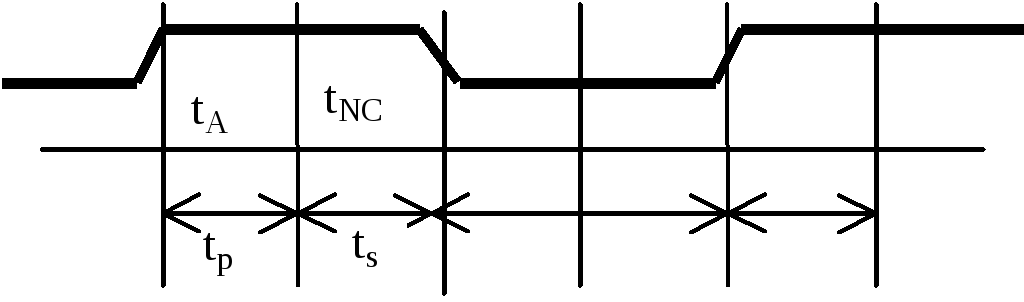

Временные диаграммы взаимодействия основных узлов микроЭВМ

![]()

Ni – ссылка на адрес следующей микрокоманды

Ci – разряды управления процессорными элементами и субблоками.

Si – информация о состоянии ПЭ (регистр состояния).

ai – адрес текущей микрокоманды.

ta – время установки информации на выходе.

tNC – время реакции управляющей памяти на адрес, поступающий из БМУ.

ts – время формирования результата операции в ПЭ с момента поступления сигнала Сi.

tm – время, необходимое для фиксации результата операции во внешнем устройстве.

Конвейерная обработка информации

В данном случае имеют место 2 параллельных процесса:

-

Формирование адреса следующей микрокоманды.

-

Выполнение операции в проц. эл-те.

При этом задержки ts и tNC совмещаются во времени. А т.к. tp и tA приблизительно одинаковы, то быстродействие повышается в 1,5 – 1,8 раза.

Достоинства: повышение быстродействия при минимальных аппаратных затратах.

Недостатки: наличие фазового сдвига в тех участках вычислительного процесса, в которых происходит анализ состояния ПЭ. Для устранения этого недостатка используются "длинные" микрокоманды. "Длинная" микрокоманда – это микрокоманда, в которой разряды управления не изменяются в течение двух тактов.

УП и ПЭ – устройства комбинационного типа.

Многоуровневая конвейерная обработка

В данном случае имеет место случай когда ПЭ по своему быстродействию значительно превышает быстродействие памяти. В этом случае устанавливается такое количество конвейерных регистров, во сколько раз быстродействие процессора выше быстродействия памяти.

Достоинства: максимальное быстродействие при минимальных аппаратных затратах.

Недостатки: наличие фазового сдвига в тех участках вычислительного процесса, когда оценивается состояние ПЭ.

Для устранения этого недостатка используются и длинные микрокоманды, т.е. микрокоманды, которые занимают 2 такта.

Память с расслоением

В данном случае используется такое количество слоёв памяти - во сколько раз быстродействие ПЭ выше быстродействия памяти.

Достоинства: повышение быстродействия при минимальных аппаратных затратах.

Недостатки: наличие фазового сдвига при выполнения программ ветвления.

Для ликвидации этого недостатка используются длинные микрокоманды, т.е. одна и та же микрокоманда размещена в соседних слоях памяти.

Вычислительные системы с переменной длительностью цикла

Такт,

когда выполняется операция в ПЭ

1 – время необходимое для выполнения логической операции.

2 – время необходимое для выполнения арифметической операции без формирования признаков состояний.

3 – арифметические операции с формированием признаков состояний.

В структуру микрокоманды вводятся дополнительные разряды, которые обеспечивают управление генератором ТИ, который формирует соответствующую временную диаграмму.

Достоинства: повышение быстродействия на 15-20%

Недостатки: наличие машинного цикла переменной длины.

При построении вычислительных систем обычно встречаются все 4 варианта структурных решений.