Model / Lab01_Mod

.docФедеральное государственное бюджетное образовательное учреждение профессионального образования

Санкт-Петербургский национальный исследовательский университет информационных технологий механики и оптики

ФАКУЛЬТЕТ СРЕДНЕГО ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ

Лабораторная работа №1

На тему: Моделирование вычислительного устройства с аккумулятором и флагами состояния вычисления.

По дисциплине: Компьютерное моделирование аппаратной обработки данных

Выполнил:

Студент группы 253

Сергиевский Денис.

Санкт-Петербург

2014г.

Задача – спроектировать и разработать в среде LabVIEW модель пятиразрядного вычислительного устройства, отвечающего функциональным требованиям:

-

Выполнение арифметических операций сложения и вычитания (в дополнительном коде).

-

Выполнение 16 основных логических операций (+2 арифм. п.1).

-

Формирование флагов состояния вычисления:

CF (Carry Flag) – флаг переполнения (0 – переполнения нет);

Err – флаг ошибки выполнения арифметической операции (0 – нет ошибки).

ZF (Zero Flag) – флаг нулевого результата (0 – ненулевой результат);

Type – тип операции (логический – 0, арифметический – 1);

-

Сохранение результата вычисления в аккумулятор.

В соответствии с заданием к лабораторной работе были сделаны:

-

мультиплексор;

-

16 логических функций;

-

Сумматоры двух и трех чисел;

-

Регистр;

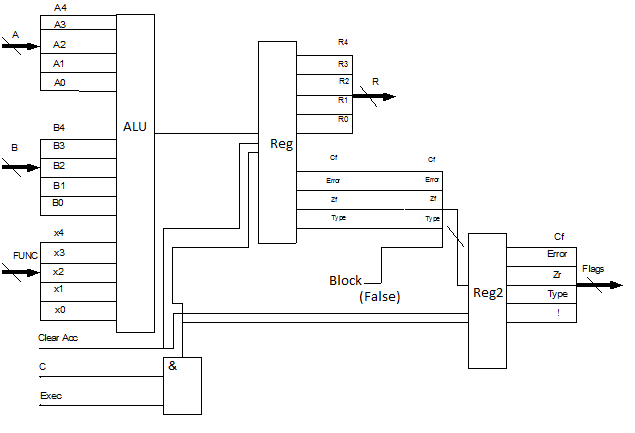

Общая схема модели пятиразрядного вычислительного устройства представлена на рисунке 1.

Рисунок №1.Общая схема пятиразрядного вычислительного устройства

Общая схема состоит из главного элемента «ALU»(Он же AluCombinated) – пятиразрядное АЛУ, которое выполняет все функции, с помощью команд. На выводе из данного устройства мы получаем пятиразрядное число в дополнительном коде. Также здесь присутствуют флаги, которые соответственно указывают на ошибки, переполнение или нулевой результат.

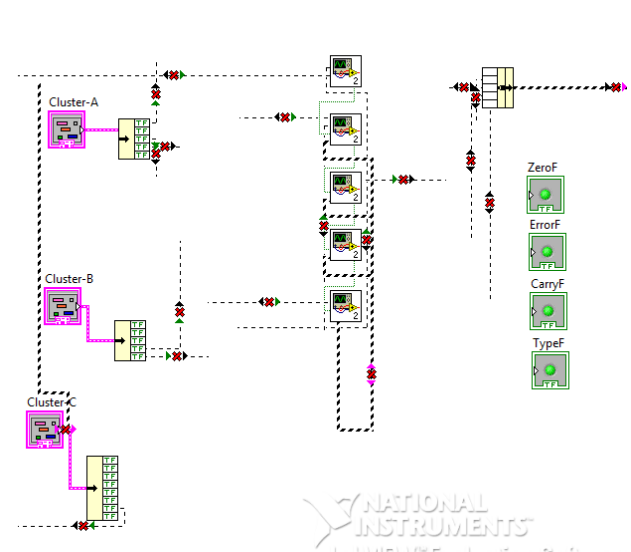

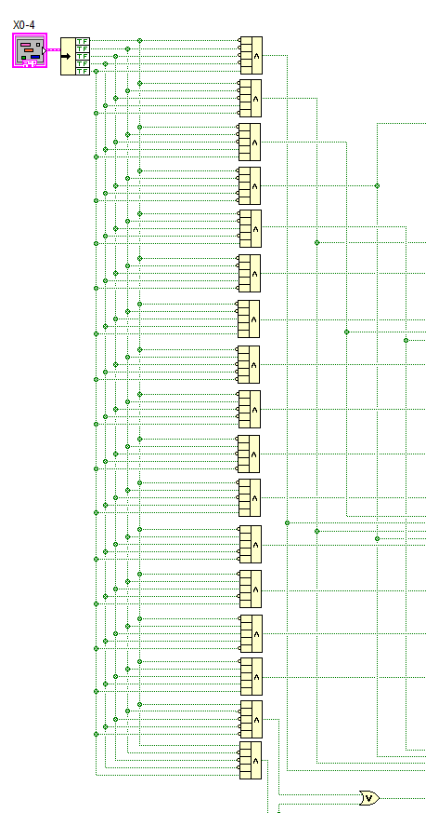

Рисунок №2 Одноразрядное АЛУ

Одноразрядное АЛУ состоит из двух больших модулей — арифметики, логики, а также дополнительных устройств (Мультиплексор). Сигнал С выбирает, какие функции должны выполняться логические или математические (сложение, вычитание).

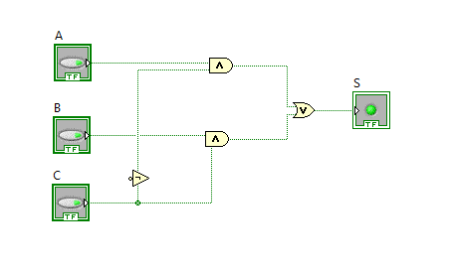

Математические функции заданы с помощью двоичного сумматора с функцией вычитания (рисунок 3). Присутствует возможность переноса (Р). Если X или Y равно 1, то S(младший разряд) равно 1, а P(старший разряд) равно 0. Если X и Y равны 1 то, на выходе P равно 1, а S равно 0.

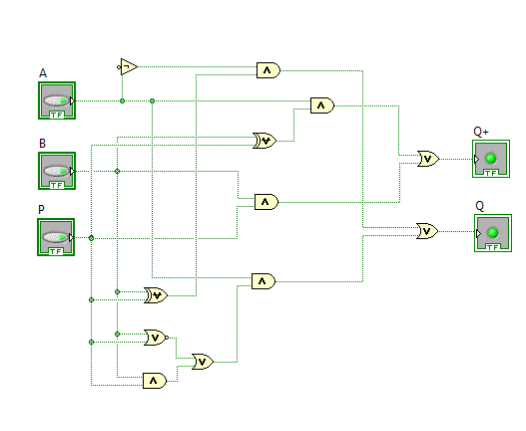

Логические функции реализованы с помощью модуля Логики (рисунок 4). В этом блоке расписаны 16 логических функций, которые представлены в таблице №1, выбираемые с помощью шести управляющих сигналов «С»:

С0 – определяет, инверсию А

С1 – определяет, инверсию В

С2 – инверсирует результа

С3 – Выбирает между блоками И/ИЛИ

С4 – глушит А

С5 – глушит В

Также, для выбора между использованием результатов модуля арифметики и логики используется одноразрядный мультиплексор (рисунок 5).

Таблица №1

|

Код операции (Func) |

Операция |

|

00000 |

«0»☺ |

|

00001 |

☺ |

|

00010 |

☺ |

|

00011 |

☺ |

|

00100 |

☺ |

|

00101 |

☺ |

|

00110 |

☺ |

|

00111 |

☺ |

|

01000 |

☺ |

|

01001 |

☺ |

|

01010 |

☺ |

|

01011 |

☺ |

|

01100 |

☺ |

|

01101 |

☺ |

|

01110 |

☺ |

|

01111 |

«1»☺ |

|

10000 |

A+B |

|

10001 |

A-B |

Рисунок №3 Арифметический модуль (Одноразрядный сумматор)

Рисунок №4 Логический модуль

Рисунок №5 Мультиплексор

В общей схеме используется регистр (рисунок 6) для сохранения значения и формируемых флагов. Для его нормальной работы используются Фронт. D-тригеры (5 блоков слева от выводимых сигналов).

Рисунок № 6 Регистр

На все устройства, выполняющие логические и арифметические операции, подаются команды (представленные в таблице №2).

Таблица №2 – соответствие заданных команд и внутренней системы команд АЛУ

|

Функции |

X1 |

X2 |

X3 |

X4 |

X5 |

С0 |

С1 |

С2 |

С3 |

С4 |

С5 |

C(ар) |

C(выч) |

|

«0» |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

☺ |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|

☺ |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

|

☺ |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

|

☺ |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|

☺ |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

☺ |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

|

☺ |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|

☺ |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

|

☺ |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

|

☺ |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

☺ |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

|

☺ |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

|

☺ |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|

☺ |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

|

«1» |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

A+B |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

A-B |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

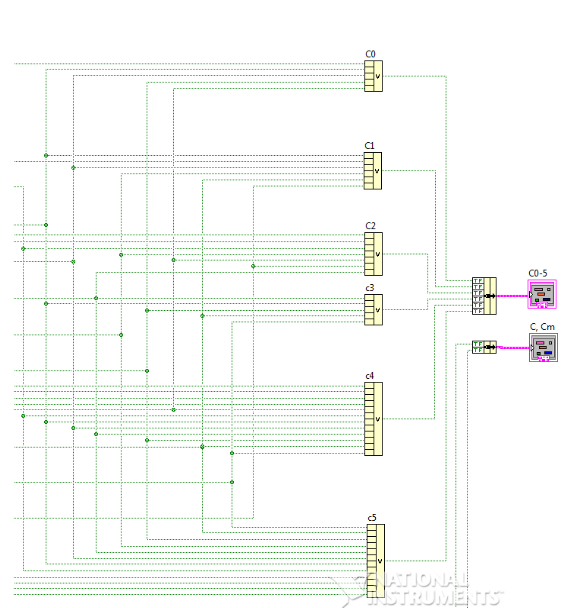

1-я часть дешифратора: множество операций «AND», а также выбор между арифметикой-вычитанием и арифметикой-сложением, представленный элементом «OR»

2 -я

часть дешифратора: множество

операций «OR»,

превращающих в итоге внешние управляющие

сигналы Х в понятные устройству внутренние

С.

-я

часть дешифратора: множество

операций «OR»,

превращающих в итоге внешние управляющие

сигналы Х в понятные устройству внутренние

С.

ВЫВОД: В ходе работы была разработана в среде LabVIEW модель зрядного АЛУ, отвечающего функциональным требованиям:

-

Выполнение арифметических операций сложения и вычитания (применяется дополнительный код).

-

Выполнение 16 основных логических операций.

-

Флаги состояния вычисления были выполнены в одноразрядном АЛУ:

CF (Carry Flag) – флаг переполнения (0 – переполнения нет, 1 – переполнение);

Err – флаг ошибки выполнения арифметической операции (0 – нет ошибки, 1 – ошибка).

ZF(0) (Zero Flag) – флаг нулевого результата (0 – ненулевой результат, 1 – нулевой результат);

Type – тип операции (логический – 0, арифметический – 1);

-

Сохранение результата вычисления в аккумулятор.