СВВиПУ_РК2

.pdf

Выбор подчиненного устройство происходит с помощью декодера адреса, формирующего сигналы HSEL.

Сигнал HREADY используется для информирования главного устройства о завершении или продолжении передачи данных. Если уровень этого сигнала активный, то передача данных завершена.

Рис. 72. Пример использования сигнала HRESP.

Сигнал HRESP[1:0] используется для подтверждения транзакции. Его значениями могут быть: OKAY – транзакция завершена успешно, ERROR – ошибка, RETRY – повторить попытку, SPLIT – данные переданы не полностью.

Сигналы HWDATA[31:0] используются для передачи данных от главного устройства к подчиненным.

Сигналы HRDATA[31:0] используются для передачи данных от подчиненных устройств к главным.

Арбитраж используется для того, чтобы только один мастер имел доступ к шине в один момент времени. Рассмотрим основные сигналы:

HBUSREQx – запрос шины у арбитра шины.

HLOCKx – сигнал, выставляемый мастером и означающий захват шины.

HGRANTx – сигнал, выставляемый арбитром и обозначающий, что мастер получил доступ к шине.

HMASTER[3:0] – сигнал показывающий номер мастера, захватившего шину.

31

Рис. 73. Пример арбитража.

На рисунке видно, что в первом такте шины главное устройство выставляет сигнал запроса шины HBUSREQx. В третьем такте арбитр подтверждает захват шины сигналом HGRANTx. На четвертом такте арбитр выставляет сигнал HMASTER с номером главного устройства, захватившего шину.

3.6.2 Системный интерфейс AMBA ASB

AMBA ASB (Advanced System |

Bus) является системным интерфейсом и |

предназначен для использования |

в высокопроизводительных 16- и 32- |

разрядных микроконтроллерах. Интерфейс позволяет связать процессор, встроенную и внешнюю память. В AMBA ASB заложена тестовая инфраструктура. AMBA ASB использовался в микроконтроллерах с процессорными ядрами ARM7TDMI, ARM 920 и ARM940. В настоящее время этот интерфейс используется сравнительно редко, вместо него обычно используют более производительный AMBA AHB.

В AMBA ASB поддерживается множество ведущих устройств и пакетная передача. Шина ASB является более простой, по сравнению с AMBA AHB. Коренными отличиями является двусторонняя шина данных (в AHB для данных есть отдельные шины, предназначенные для записи и чтения), более узкая шина данных (32 разряда), не поддерживается раздельная (SPLIT) передача данных.

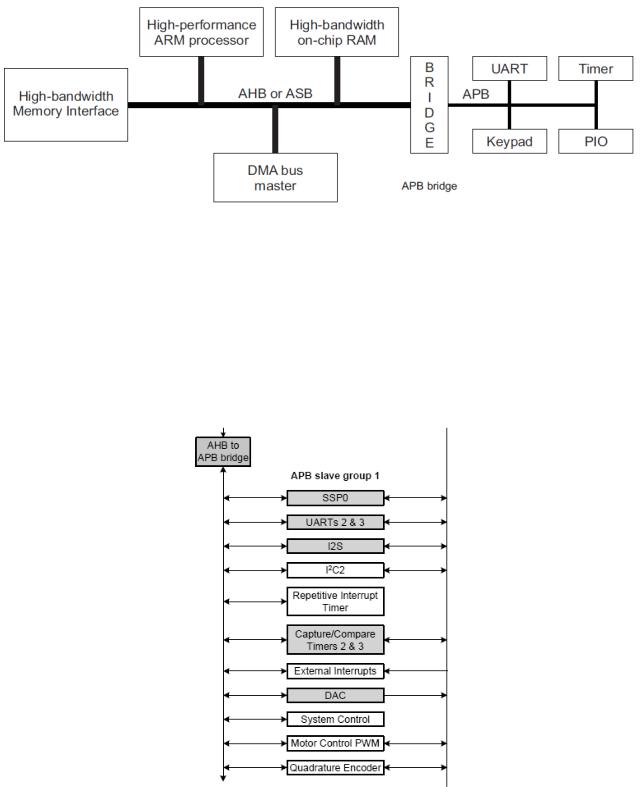

Рис. 74. Типичная система, построенная на базе AMBA ASB.

32

Система с шиной AMBA ASB (AHB) обычно содержит следующие компоненты:

ASB-ведущий (мастер). Мастер инициирует операции чтения и записи посредством подачи адреса и управляющих сигналов. Только один мастер в определенный момент времени может быть активным.

ASB-ведомый (слейв). Ведомый отвечает на операции чтения и записи в заданном адресном пространстве. Ведомый сигнализирует активному мастеру в случае успешного, ошибочного обмена данными или в случае ожидания.

ASB-дешифратор. Выполняет дешифровку адресов и выбирает соответствующего ведомого. Дешифратор также гарантирует, что шина остается в рабочем состоянии, когда никакого обмена не производится.

ASB-арбитр. Арбитр гарантирует, что только одному мастеру в данный момент времени позволяется инициировать обмен данными. И хотя протокол разрешения доступа к общей шине зафиксирован, любой алгоритм разрешения конфликтов может быть реализован в зависимости от требований области применения.

В шине возможны три основных состояния:

NONSEQUENTIAL (N-TRAN)– используется для одиночных передач или первой передачи данных в пакете.

SEQUENTIAL (S-TRAN) – используется при пакетной передаче данных.

ADDRESS-ONLY – используется, если нет необходимости в передаче данных.

33

Рис. 75. Одиночная (NONSEQUENTIAL) передача данных.

Рассмотрим основные сигналы шины: BCLK

– сигнал тактового генератора. BD[31:0] – шина данных.

BA[31:0] – шина адреса. BWRITE –

сигнал запись/чтение.

BTRAN[1:0] – тип передачи (NONSEQUENTIAL, SEQUENTIAL, ADDRESS-ONLY).

BSIZE[1:0] – размер передаваемых данных. DSELx – выбор устройства.

Рассмотрим взаимодействие нескольких главных устройств через арбитр шины:

Главное устройство выставляет сигнал AREQx, означающий запрос на захват шины.

Арбитр считывает запрос от главного устройства.

Если сигнал BLOCK пассивен, то арбитр разрешает захват шины главному устройству, выставляя сигнал AGNTx. В противном случае, если сигнал BLOCK активен, разрешение на захват шины не выдается.

34

Рис. 76. Арбитраж в мультимастерном режиме работы шины AMBA ASB.

Интерфейс подчиненного устройства на шине AMBA ASB имеет следующий вид:

Рис. 77. Интерфейс подчиненного устройства для AMBA ASB.

3.6.3 Периферийный интерфейс AMBA APB

Интерфейс AMBA APB (Advanced Peripheral Bus) является частью иерархии интерфейсов AMBA и предназначен для объединения периферии, используемой в микроконтроллерах. Интерфейс AMBA APB используется практически во всех современных микроконтроллерах с ядром ARM.

35

Цель создания интерфейса – минимизация потребляемой мощности и упрощение архитектуры вычислительной системы.

Рис. 78. Типичный микроконтроллер с периферийными контроллерами, подключенными к шине AMBA APB.

Интерфейс AMBA APB инкапсулирован в одном подчиненном устройстве шин AMBA AHB или AMBA ASB. При использовании шины APB потребление энергии значительно меньше, чем при прямом подключении контроллеров к системной шине. Интерфейс APB имеет смысл использовать с такими устройствами, в которых не требуется высокая пропускная способность шины и пакетный режим работы. Примерами таких устройств могут быть: контроллеры последовательного канала, таймеры, контроллеры I2C, SPI, ЦАП, АЦП, часов реального времени, сторожевого таймера и так далее.

Рис. 79. Фрагмент одной из шин APB в микроконтроллере NXP LPC 1768 на базе Cortеx-M3.

Единственным главным устройством (мастером) на шине APB является мост. Все остальные устройства (контроллеры) являются подчиненными устройствами.

36

Интерфейс AMBA APB может находиться в одном из трѐх состояний: IDLE – устройство не готово, шина находится в исходном состоянии. SETUP – запущен процесс инициализации устройства.

ENABLE – устройство готово к обмену.

Рис. 80. Три состояния шины AMBA APB.

Если требуется что-то передать по шине, мы должны выбрать устройство, с которым мы будем общаться, с помощью сигнала PSELx. После получения сигнала устройство производит инициализацию и выставляет на шину сигнал

PENABLE.

Циклы чтения и записи имеют вид, показанный на рисунке ниже.

Рис. 81. Цикл записи данных в шине AMBA APB.

37

Рис. 82. Цикл чтения на шине AMBA APB.

Для взаимодействия с шинами AMBA AHB или AMBA ASB используется мост

(APB bridge).

Рис. 83. Мост между периферийной шиной AMBA APB и шинами AMBA ASB или AMBA AHB.

Интерфейс для подключения подчиненных устройств к шине AMBA APB очень прост и имеет следующий вид:

Рис. 84. Интерфейс подчиненного устройства в шине AMBA APB

38

3.7 Системные интерфейсы

3.7.1 Интерфейс PCI

PCI (Peripheral Component Interconnect) – мультплексированный,

параллельный (разрядность 32 или 64 бита) системный интерфейс. Первая спецификация на этот интерфейс появилась в 1992 году. Первоначально интерфейс использовался в персональных компьютерах, работающих под управлением операционных

3.7.1.1 PCI-2.0

Спецификация PCI 2.0 (Peripheral Component Interconnect Local Bus Revision 2.0) определяет процессорно-независимую шину, предусматривающую подключение до шести устройств, в том числе контроллера шины PCI и дополнительного контроллера шины расширения ISA, EISA или МСА. Тактовая частота шины РСI достигает 33 МГц, причем обмен по ней может осуществляться 32или 64-разрядными словами.

Рис. 85. Блок схема вычислительной системы на базе PCI.

Предусматривается одновременная поддержка нескольких главных устройств локальной шины, что важно для будущих мультимедиа- и других систем, обрабатывающих большие объемы графики, видео и данных других типов. Шина РСI поддерживает блочный обмен последовательными данными при выполнении операций чтения и записи данных в память.

В архитектуре РСI предусмотрен мост, развязывающий процессор и шину расширения при сохранении 32-разрядного тракта обмена данными с периферийными устройствами. Контроллер шины позволяет организовывать очередь операций записи и чтения.

Предусматривается возможность использования одной и той же системной платы для ЦП разных поколений, что, однако, требует более сложных схем управления контроллером шины РСI.

39

С целью сокращения числа выводов периферийных интегральных схем и снижения стоимости компонентов используется мультиплексирование сигналов.

Средняя номинальная скорость передачи данных по шине составляет 120 МБ/с, а пиковая – 132 МБ/с для 32-разрядного тракта передачи данных и 264 МБ/с – для 64-разрядного тракта.

Шина РСI поддерживает интерфейсы различных типов: МСА, ISA и EISA. Некоторые платы РСI могут использоваться в системах на различных платформах.

Рис. 86. Сигналы PCI-2.0.

В спецификации PCI 2.0 предусмотрены разные соединители для нормального (5 В) и пониженного (3,3 В) напряжения питания. Существуют соответственно 5- и 3,3-вольтовые платы, а также универсальные платы, которые могут устанавливаться в соединители обоих типов.

Имеются два дополнительных контакта PRSNT1# (В9) и PRSNT2# (В11). Они используются для индикации установки платы в гнездо и указывают величину необходимой для ее питания мощности. Благодаря отмеченным особенностям шина РСI может стать оптимальным выбором для компьютеров будущего. Ее внедрение обеспечит высокую производительность и хорошую совместимость.

Основой управления всеми передачами данных на PCI служат три сигнала: FRAME# ведѐтся задатчиком для отображения конца запроса.

IRDY# ведѐтся задатчиком, позволяя вызывать циклы ожидания. TRDY#

ведѐтся исполнителем, позволяя ему вызывать циклы ожидания. |

|

Интерфейс не занят, если запрещены и FRAME# и IRDY#. Первый |

фронт |

синхроимпульса на котором разрешается FRAME# это адресная фаза, |

и |

40 |

|