pdm_03

.pdf

Управляющие входы триггеров

S– (от англ. Set - установка) раздельный вход установки триггера в единичное состояние по прямому выходу Q.

R– (от англ. Reset - сброс) раздельный вход установки триггера в нулевое состояние по прямому выходу Q.

J– (от англ. Jerk - включение) вход установки универсального триггера в состояние 1.

K– (от англ. Kill - выключение) вход сброса универсального триггера в состояние 0.

D– (от англ. Data - данные) информационный вход переключения триггера в состояние соответствующее логическому уровню на этом входе, требует подтверждения тактированием.

T– (от англ. Toggle - переключатель) счѐтный вход.

C – (от англ. Clock - время) синхронизирующий вход.

V – (от англ. Value - значение) вход запрета и начальной установки триггера.

Кроме основных, перечисленных входов триггер может иметь дополнительные входы.

21

Примеры расшифровки обозначений триггеров

CL RS - тактируемый RS - триггер вида L, |

переключаемый |

|

по входам |

R, S - сигналом высокого уровня |

(L). |

Возможно |

иное обозначени е : CL RS = CL R LSL = (CRS) L . |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

RS - тактируемый RS - триггер вида L, |

переключаемый |

|||||||||||||||||||||||||

L |

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

по входам |

R, S - сигналом низкого уровня |

(L). |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Возможно |

иное обозначени е : C |

|

|

|

RS = C |

|

|

R |

|

S |

|

|

= (CRS) |

|

. |

|

||||||||||||||

L |

L |

L |

|

L |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

C |

LFJK - тактируемый JK - триггер вида LF, |

|

|

переключаемый |

||||||||||||||||||||||||||

по входам J, K - сигналом л . нуля (0). |

|

|

|

|

|

|

|

|

||||||||||||||||||||||

Возможно |

иное обозначени е : C |

LFJK = C |

LFJ |

LFK |

LF = (CJK) |

LF . |

||||||||||||||||||||||||

Подробнее о номенклатуре триггеров можно прочитать в специализированной литературе [3].

22

Обобщѐнная модель триггера

S

A1

…

An

Вход V1

…

Vk C1

…

CRp

БУ |

S |

Q |

… |

a1 |

|

… |

|

Выход |

|

|

|

… |

a2 |

|

|

¬Q |

|

|

|

|

|

R |

|

Блок управления |

Блок памяти |

23

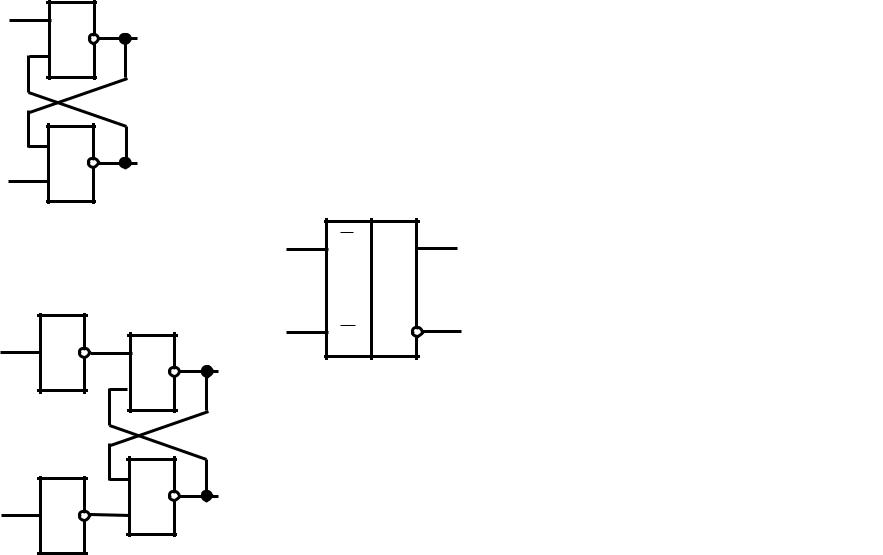

Однофазный асинхронный RS-триггер

RS-триггер – элементарный автомат с двумя устойчивыми состояниями, имеющий два информационных входа R и S, такие, что при R=1, S=0 триггер принимает состояние 0 (Q=0), а при S=1, R=0 – состояние 1 (Q=1). В соответствии с состоянием, принимаемым триггером, вход S называют единичным входом триггера, а вход R – нулевым входом триггера.

|

|

|

& |

Карта Карно |

|

|

|

|

Таблица истинности |

||||||

R |

1 |

|

Q |

Qn+1 |

|

RnSn |

|

|

Rn |

Sn Qn+1 состояние |

|||||

|

|

|

1 |

00 01 11 10 |

|

0 |

0 |

Qn |

разрешено |

||||||

S |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

разрешено |

|

(RS)L-триггер схема |

|

Qn |

|

||||||||||||

|

1 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

разрешено |

|||||

на логических элементах |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

Q |

Характеристическое уравнение |

|

1 |

1 |

1 |

запрещено |

||||||

|

|

R T |

RS-триггера имеет рекуррентную |

||||||||||||

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

форму: |

|

Qn+1=Sn+(Qn)∙¬(Rn). |

|

|

11 |

|

|||||

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

01 |

|

|

|

|

Обозначение |

|

|

|

00, 10 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

0 |

|

|

1 |

00, 01 |

|||||

|

|

|

|

|

|

|

|

|

10 |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В электронных схемах на логических |

|

|

|

|

|

|

|

|

|

|||||

элементах необходимо исключать |

Граф переходов RS-триггера |

|

возможность перехода RS-триггера в |

||

|

||

запрещѐнное состояние. |

24 |

Парафазный асинхронный RS-триггер

S

1 ¬Q

1 Q

R

(RS)L-триггер схема

на логических элементах ИЛИ-НЕ

S 1

& Q

& ¬Q

R 1

S T Q

R ¬Q

Обозначение

Таблица истинности

Rn Sn |

Qn+1 ¬Qn+1 |

|

состояние |

|||||||

0 |

0 |

|

Qn |

¬Qn |

|

разрешено |

||||

|

|

(Q ≠ ¬Q) |

|

|||||||

|

|

|

|

|

|

|

|

|||

0 |

1 |

1 |

0 |

|

разрешено |

|||||

|

(Q ≠ ¬Q) |

|

||||||||

|

|

|

|

|

|

|

|

|||

1 |

0 |

0 |

1 |

|

разрешено |

|||||

|

(Q ≠ ¬Q) |

|

||||||||

|

|

|

|

|

|

|

|

|||

1 |

1 |

0 |

0 |

|

запрещено |

|||||

|

(Q = ¬Q) |

|

||||||||

|

|

|

|

|

|

|

|

|||

Карта Карно |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Qn+1¬Qn+1 |

|

|

|

RnSn |

|

||||

|

|

00 |

01 |

11 |

|

10 |

||||

|

|

|

|

|

|

|||||

|

|

|

00 |

|

XX |

10 |

00 |

|

01 |

|

Qn¬Qn |

|

01 |

|

01 |

10 |

00 |

|

01 |

||

|

11 |

|

XX |

10 |

00 |

|

01 |

|||

|

|

|

|

|

||||||

|

|

|

10 |

|

10 |

10 |

00 |

|

01 |

|

(RS)L-триггер схема на |

|

логических элементах И-НЕ |

25 |

|

Парафазный асинхронный ¬R¬S-триггер

S |

& Q |

|

& ¬Q

R

(RS)¬L-триггер схема

на логических элементах И-НЕ

S 1

1 Q

1 ¬Q

R 1

S T Q

¬Q

R

Обозначение

Таблица истинности

Rn Sn |

Qn+1 ¬Qn+1 |

|

состояние |

||||||||

0 |

0 |

1 |

1 |

|

запрещено |

||||||

|

|

(Q = ¬Q) |

|

||||||||

|

|

|

|

|

|

|

|

|

|||

0 |

1 |

0 |

1 |

|

разрешено |

||||||

|

|

(Q ≠ ¬Q) |

|

||||||||

|

|

|

|

|

|

|

|

|

|||

1 |

0 |

1 |

0 |

|

разрешено |

||||||

|

|

(Q ≠ ¬Q) |

|

||||||||

|

|

|

|

|

|

|

|

|

|||

1 |

1 |

|

Qn |

¬Qn |

|

разрешено |

|||||

|

|

|

(Q ≠ ¬Q) |

|

|||||||

|

|

|

|

|

|

|

|

|

|||

Карта Карно |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Qn+1¬Qn+1 |

|

|

|

|

RnSn |

|

||||

|

|

00 |

|

01 |

11 |

|

10 |

||||

|

|

|

|

|

|

|

|||||

|

|

|

00 |

|

11 |

|

01 |

XX |

|

10 |

|

Qn¬Qn |

|

01 |

|

11 |

|

01 |

01 |

|

10 |

||

|

11 |

|

11 |

|

01 |

XX |

|

10 |

|||

|

|

|

|

|

|

||||||

|

|

|

10 |

|

11 |

|

01 |

10 |

|

10 |

|

(RS)¬L-триггер схема на |

|

логических элементах ИЛИ-НЕ |

26 |

|

Асинхронный парафазный JK-триггер

K |

1 |

& |

|

|

|

||

J |

|

1 |

Q |

|

& |

|

|

|

|

|

J T Q

K ¬Q

Обозначение

Карта Карно |

|

|

|

|||

Qn+1 |

|

JnKn |

|

|||

00 |

01 11 10 |

|||||

|

|

|||||

Qn |

0 |

0 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

1 |

||

|

||||||

1 |

¬Q |

|

Характеристическое уравнение JKтриггера имеет рекуррентную форму:

Qn+1=Jn∙(¬Qn)+(¬Kn)∙(Qn).

10, 11

00, 01 |

0 |

1 |

00, 10 |

01, 11

Граф переходов JK-триггера

При установке постоянным уровня J=K=1 триггер будет работать в режиме генератора, непрерывно переключаясь. Для исключения перехода триггера в режим генератора необходимо ограничивать продолжительность комбинации K=J=1 временем достаточным для требуемого переключения.

27

Тактируемый CLRS-триггер

S |

& |

|

|

Q |

|

|

S T |

||

|

& |

Q |

|

|

|

|

|

||

|

|

|

С |

|

C |

|

|

R |

¬Q |

|

|

|

|

|

|

& |

¬Q Обозначение |

||

|

& |

|

|

|

R |

|

|

|

|

CLRS-триггер, схема на |

|

|

||

логических элементах И-НЕ |

|

|

||

Характеристическое уравнение CLRSтриггера имеет рекуррентную форму:

Qn+1=(¬Cn )∙Qn+ Qn∙(¬Rn)+Cn∙Sn.

Таблица истинности

Qn |

Rn |

Sn |

|

Qn+1 |

||

Cn=1 Cn=0 |

||||||

|

|

|

||||

0 |

0 |

0 |

0 |

0 |

||

0 |

0 |

1 |

1 |

0 |

||

0 |

1 |

0 |

0 |

0 |

||

0 |

1 |

1 |

X |

|

0 |

|

1 |

0 |

0 |

1 |

1 |

||

1 |

0 |

1 |

1 |

1 |

||

1 |

1 |

0 |

0 |

1 |

||

1 |

1 |

1 |

X |

|

1 |

|

Карта Карно

Qn+1 |

|

|

RnSn |

|

||

|

00 |

01 |

11 |

10 |

||

|

|

|||||

|

00 |

0 |

0 |

0 |

0 |

|

СnQn |

01 |

1 |

1 |

1 |

1 |

|

11 |

1 |

1 |

X |

0 |

||

|

||||||

|

10 |

0 |

1 |

X |

0 |

|

Тактируемый CLRS-триггер наиболее часто реализуется на базисе

элементов одноступенчатой И-НЕ или двухступенчатой И-ИЛИ-НЕ |

28 |

|

логики. |

||

|

Однофазный синхронный CLD-триггер

&

С 1

1 Q

&

D

CLD-триггер, схема на логических элементах И, НЕ, ИЛИ

D T Q

C

Обозначение

Таблица истинности |

Карта Карно |

|

|

|||||

|

|

|

|

|

|

Cn |

|

|

Cn |

Qn |

Dn |

Qn+1 |

|

Qn+1 |

|

||

0 |

0 |

0 |

0 |

|

0 |

1 |

||

|

|

|

||||||

0 |

0 |

1 |

0 |

|

|

00 |

0 |

0 |

0 |

1 |

0 |

1 |

|

QnDn |

01 |

0 |

1 |

0 |

1 |

1 |

1 |

|

11 |

1 |

1 |

|

|

|

|||||||

1 |

0 |

0 |

0 |

|

|

10 |

1 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

1 |

1 |

0 |

0 |

|

|

|

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

Характеристическое уравнение CLD- триггера имеет рекурентную форму:

Qn+1=Cn∙Dn+(¬Cn)∙Qn.

Как и других триггеров у CLD-триггера имеется несколько вариантов схемотехнического решения предоставляющих равные функциональные возможности но отличающиеся техническими характеристиками (число логических элементов, потребляемая

мощность, быстродействие).

29

Регистры

Регистры – устройства выполняющие функции, приѐма, хранения и передачи информации. На базе регистров так же выполняют операции преобразования информации: сдвига, сравнения, сложения, умножения и др.

ПО СПОСОБУ ЗАПИСИ

Параллельные регистры – запись и чтение осуществляется параллельным кодом.

Последовательные регистры – запись и чтение осуществляется последовательным кодом, путѐм сдвига задаваемого тактирующими импульсами.

Параллельно-последовательные регистры – позволяют производить запись и чтение параллельным и последовательным способом в различных

комбинациях (например: последовательная запись, параллельное чтение). |

|

ПО ЧИСЛУ КАНАЛОВ ЗАПИСИ |

|

Однофазные регистры – информация для записи поступает по одному |

|

каналу, часто выполняются на триггеров СD типа. |

|

Парафазные регистры – информация для записи поступает по двум |

|

каналам, часто выполняются на базе триггеров СRS типа. |

|

ПО ЧИСЛУ РАЗРЯДОВ РЕГИСТРА |

|

По числу разрядов образующих связанный логическими функциями ряд |

|

однотипных или сходных элементов каждый из которых имеет свой номер |

|

(0…n). |

30 |