Московский Государственный Институт Электронной Техники

(Технический Университет)

Курсовой проект на тему:

«Демультиплексор из 1 в 16»

по дисциплине:

Компьютерное моделирование

интегральных приборов

Выполнил: Ермолаев Д. К.

Группа: ЭКТ-36

г. Москва

2005г.

Содержание.

Содержание. 2

Мультиплексоры и демультиплексоры 3

Мультиплексор 3

Демультиплексор 4

Предварительный расчет параметров транзисторов: 10

Расчет допустимой максимальной длины участка межсоединений: 10

Мультиплексоры и демультиплексоры

Мультиплексор

Мультиплексор – это устройство, осуществляющее выборку одного или нескольких входов и подключает его к своему выходу.

У словное

обозначение:

словное

обозначение:

D0 - D3 - входы данных

A0 - A1 - адресный вход

C - вход синхронизации

Q

и

![]() - прямой и инверсный выходы

- прямой и инверсный выходы

|

00 |

D0

|

|||||

|

01 |

D1

|

|||||

|

10 |

D2

|

|||||

|

11 |

D3

|

|||||

|

|

Адреса |

Стр. |

Вых. |

|

||

|

|

A1 |

A0 |

|

|

|

|

|

|

X |

X |

1 |

0 |

|

|

|

|

0 |

0 |

0 |

D0 |

|

|

|

|

0 |

1 |

0 |

D1 |

|

|

|

|

1 |

0 |

0 |

D2 |

|

|

|

|

1 |

1 |

0 |

D3 |

|

|

Каждому информационному

входу мультиплексора присваивается

адрес (D0

- D3).

При подачи сторобирующего сигнала

(сигнал на вход С) мультиплексор выбирает

один из входов, адрес которого подается

в двоичном коде на адресные входы и

подключает его к выходу. Таким образом

подавая на адресные входы адреса

различных информационных входов можно

передать цифровые сигналы с этих входов

на выход Q.

Следовательно, число информационных

входов nинф.

И число адресных входов nадр

связаны следующим соотношением:

![]() .

.

Мультиплексорное дерево

П ромышленностью

выпускаются мультиплексоры, в которых

количество адресных входов не более

4-х. Если необходимо смонтировать более

16-и каналов используется мультиплексорное

дерево.

ромышленностью

выпускаются мультиплексоры, в которых

количество адресных входов не более

4-х. Если необходимо смонтировать более

16-и каналов используется мультиплексорное

дерево.

Демультиплексор

Демультиплексор - устройство, имеющие один информационный вход, адресные входы и несколько выходов, осуществляющие коммуникацию входа на тот вход, адрес которого задан на адресных входах. (Е- вход разрешения работы).

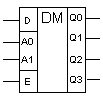

Условное обозначение:

С помощью демультиплексора и мультиплексора можно построить коммутатор каналов.

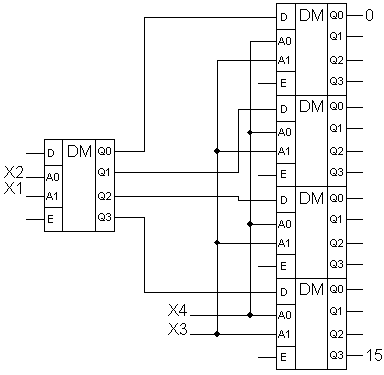

Манипулируя сигналами x1 - x4, можно скоммутировать любые входные и выходные цепи, т.е. например сигнал со входа D0 подать на выход Q2, для чего на адресные входы подаём: x1=0; x2=0; x3=0; x4=1.

Демультиплексорное дерево

Строится в том случае, если не хватает адресных входов, для реализации необходимого количества коммутируемых каналов.

|

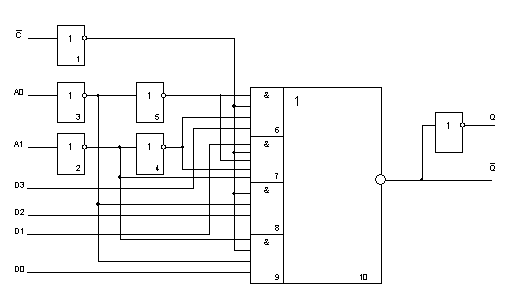

Исходная логическая схема проектируемого устройства: |

|

|

|

Электрические схемы используемых логических элементов в КМДП-базисе |

|

|

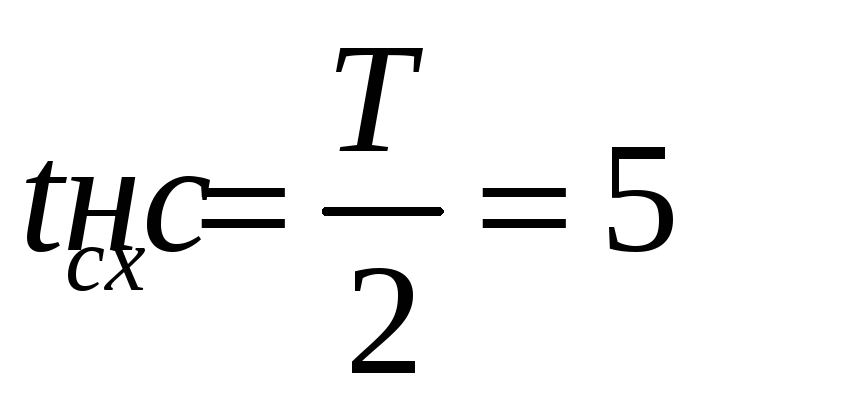

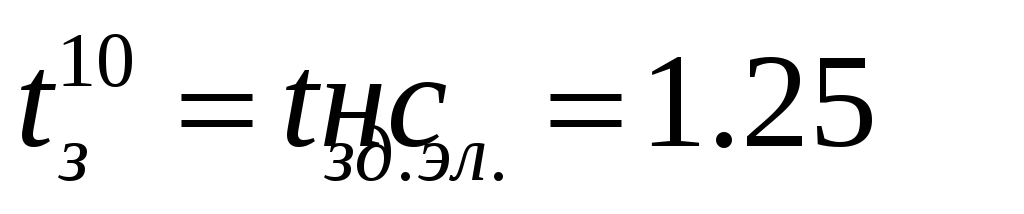

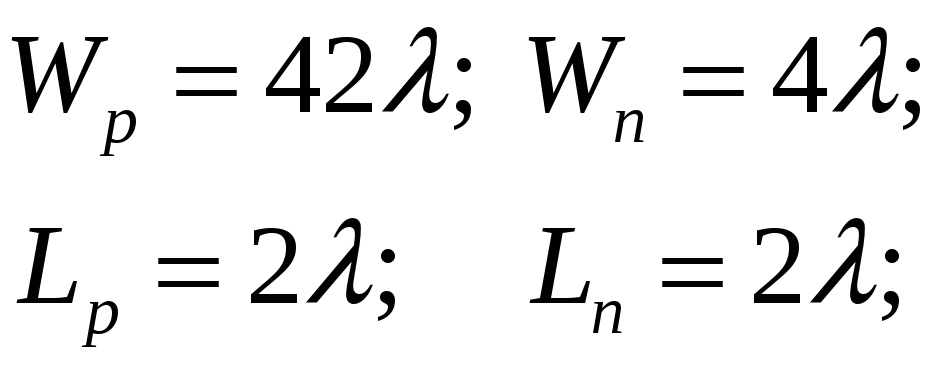

Предварительный расчет параметров транзисторов:

-

-

,

,

,

,

-

Полагая, что

,

,

получим

получим

![]()

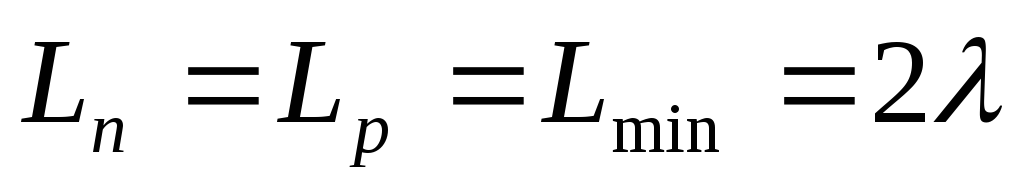

Размеры транзисторов в логических элементах для наихудшего случая:

а) 2-ИЛИ-НЕ:

б) 3-ИЛИ-НЕ:

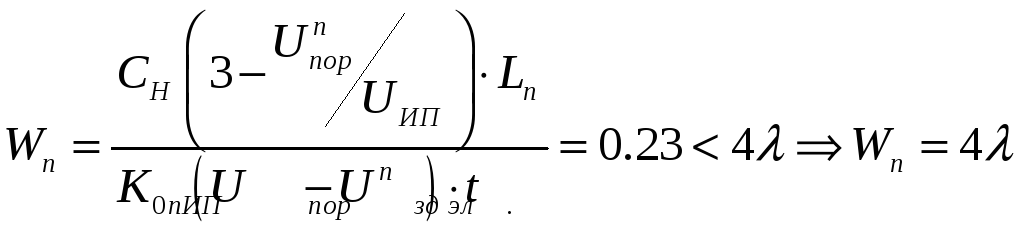

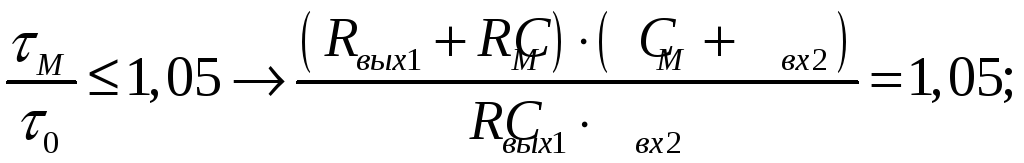

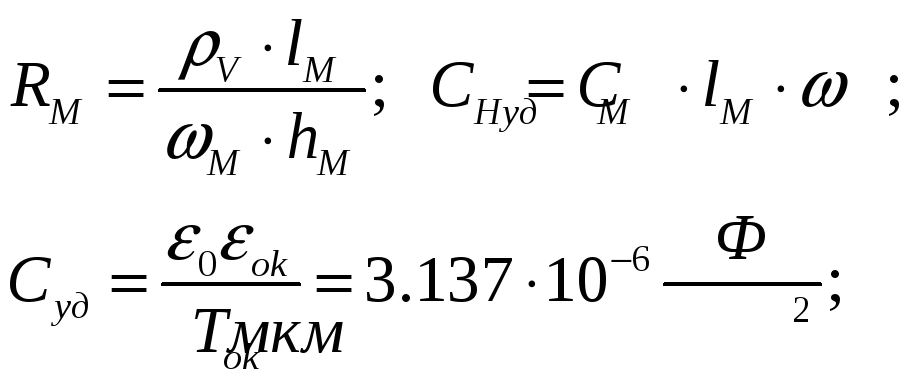

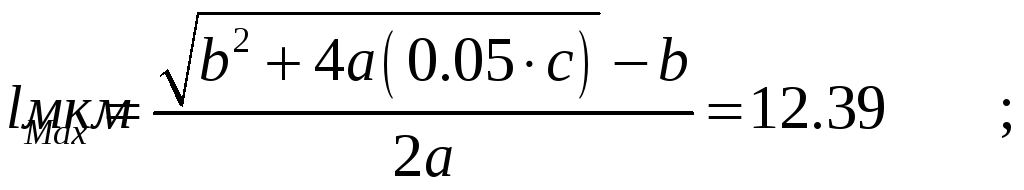

Расчет допустимой максимальной длины участка межсоединений:

|

hpoly, мкм |

TokPoly, мкм |

hMe, мкм |

TokMe, мкм |

Wpoly, |

Me, |

dok, нм |

||

|

мкм |

|

мкм |

|

|||||

|

0,25 |

0,4 |

0,7 |

1,1 |

2 |

0,6 |

3 |

0,9 |

15 |

hk, мкм = 45 dok – длина канала;

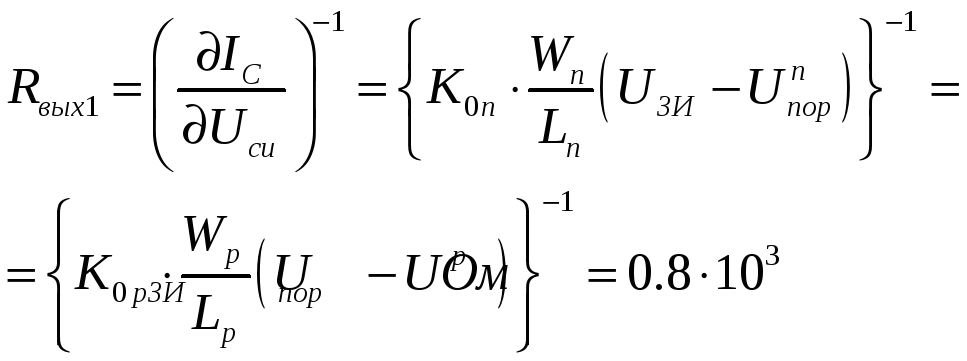

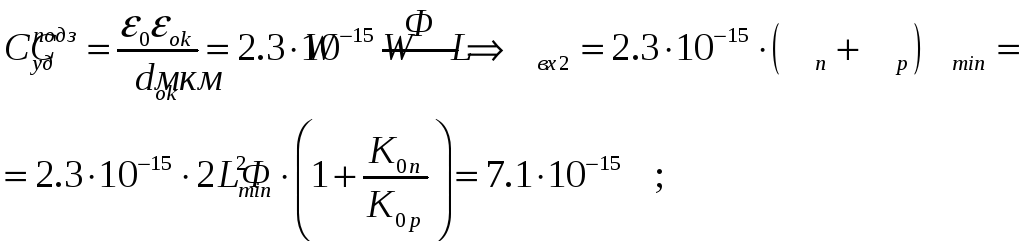

![]() - без

межсоединений;

- без

межсоединений;

![]() - с межсоединениями;

- с межсоединениями;

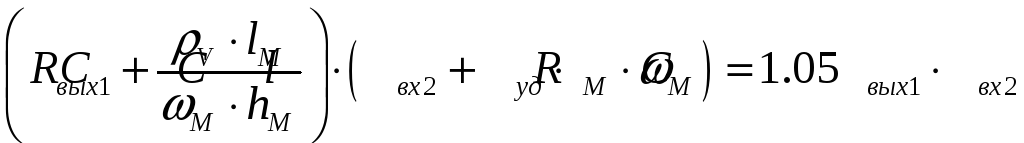

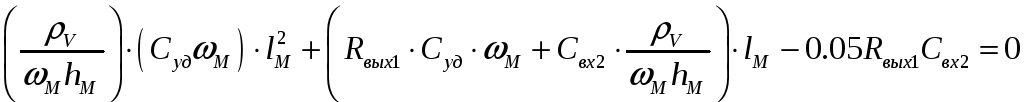

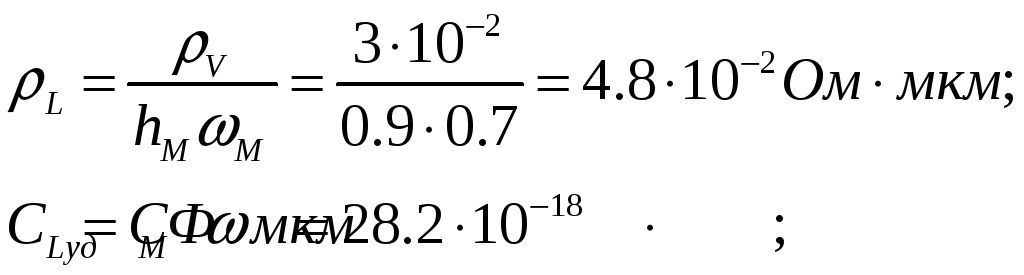

(*)

(*)

где

- погонное сопротивление и емкость

соответственно

- погонное сопротивление и емкость

соответственно

![]()

таким образом коэффициенты квадратного уравнения (*) равны:

![]()

и уравнение вида

![]() будет иметь решение:

будет иметь решение:

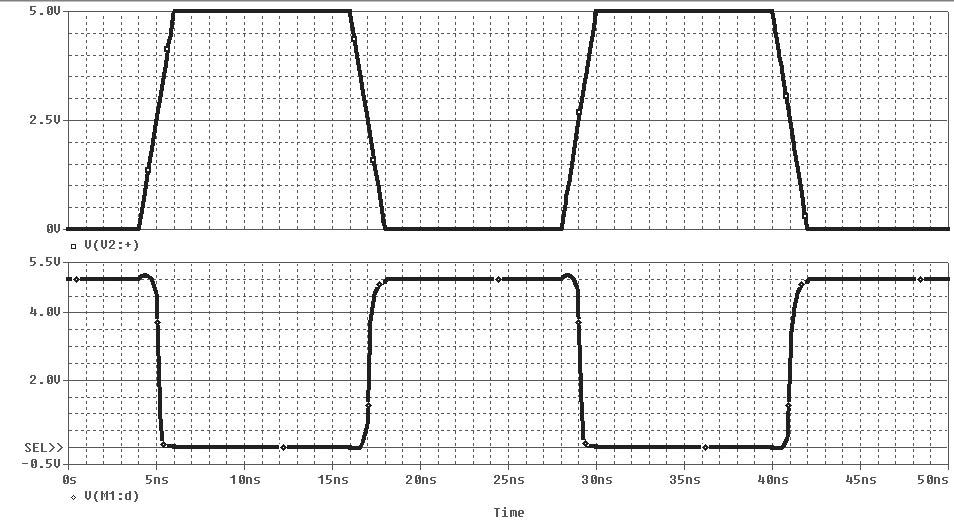

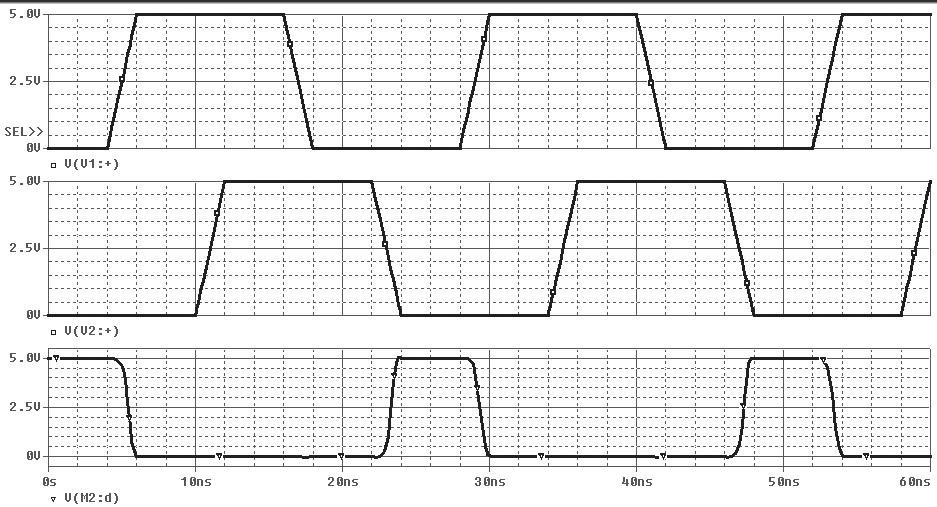

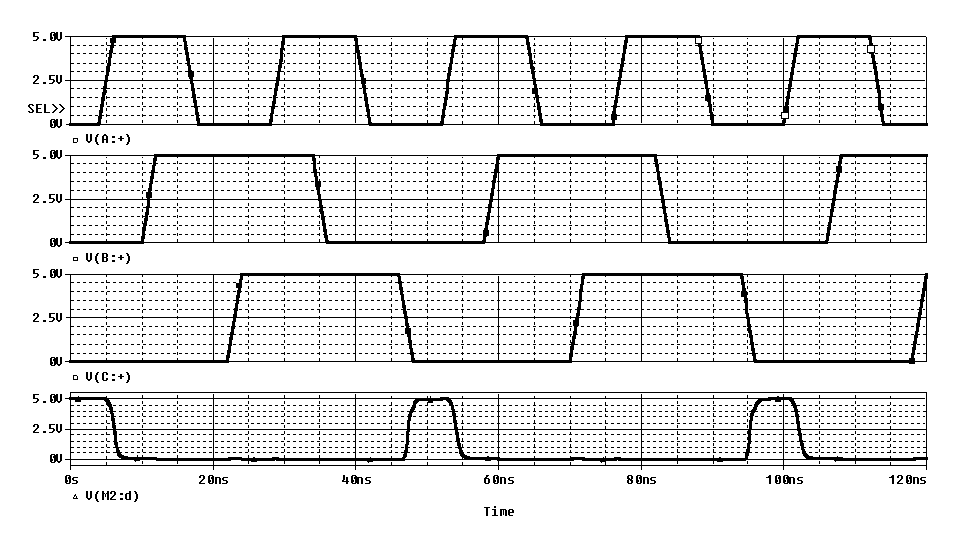

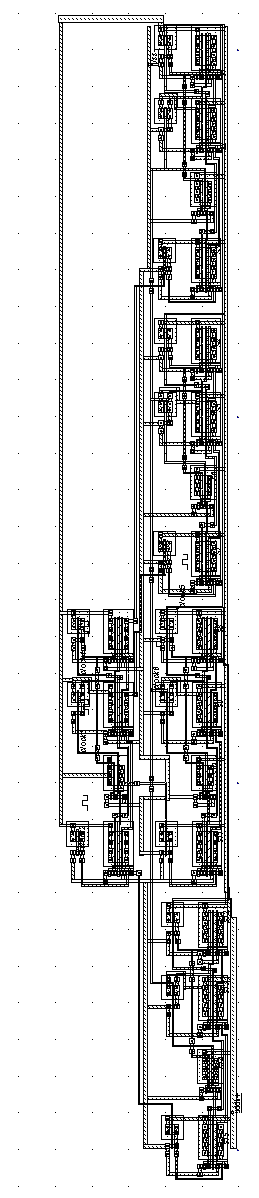

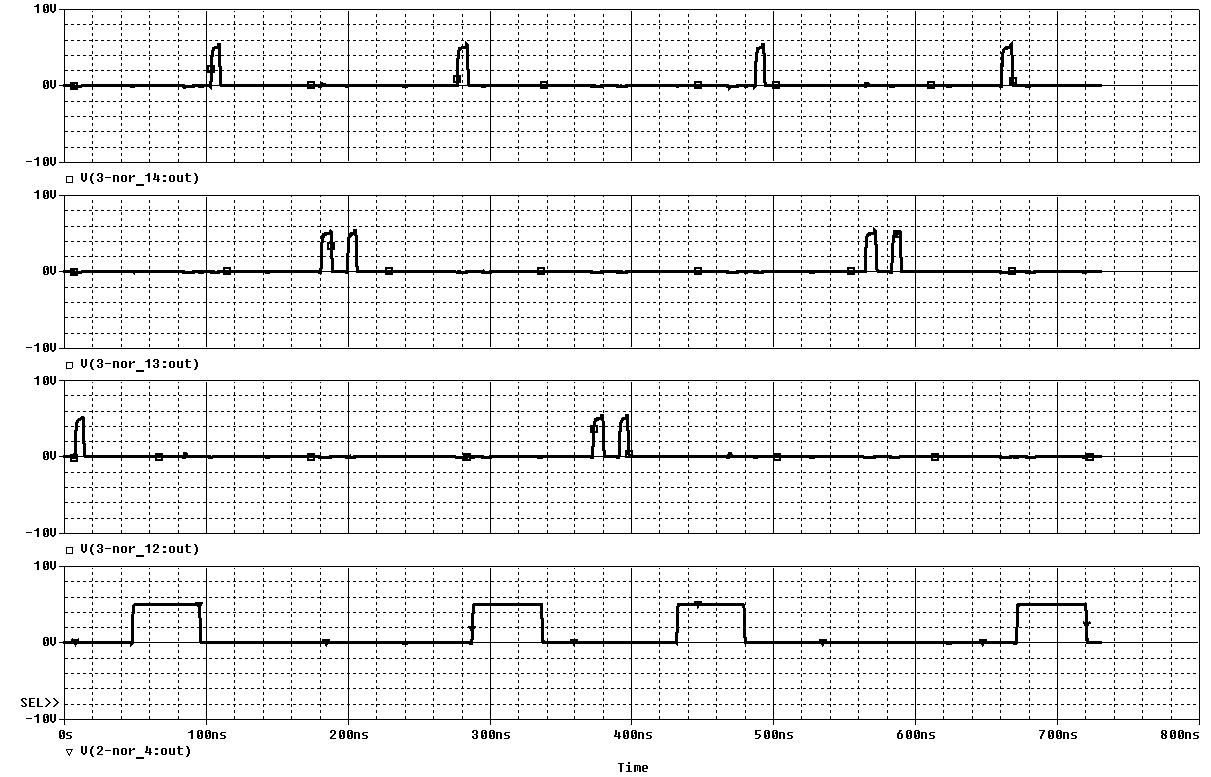

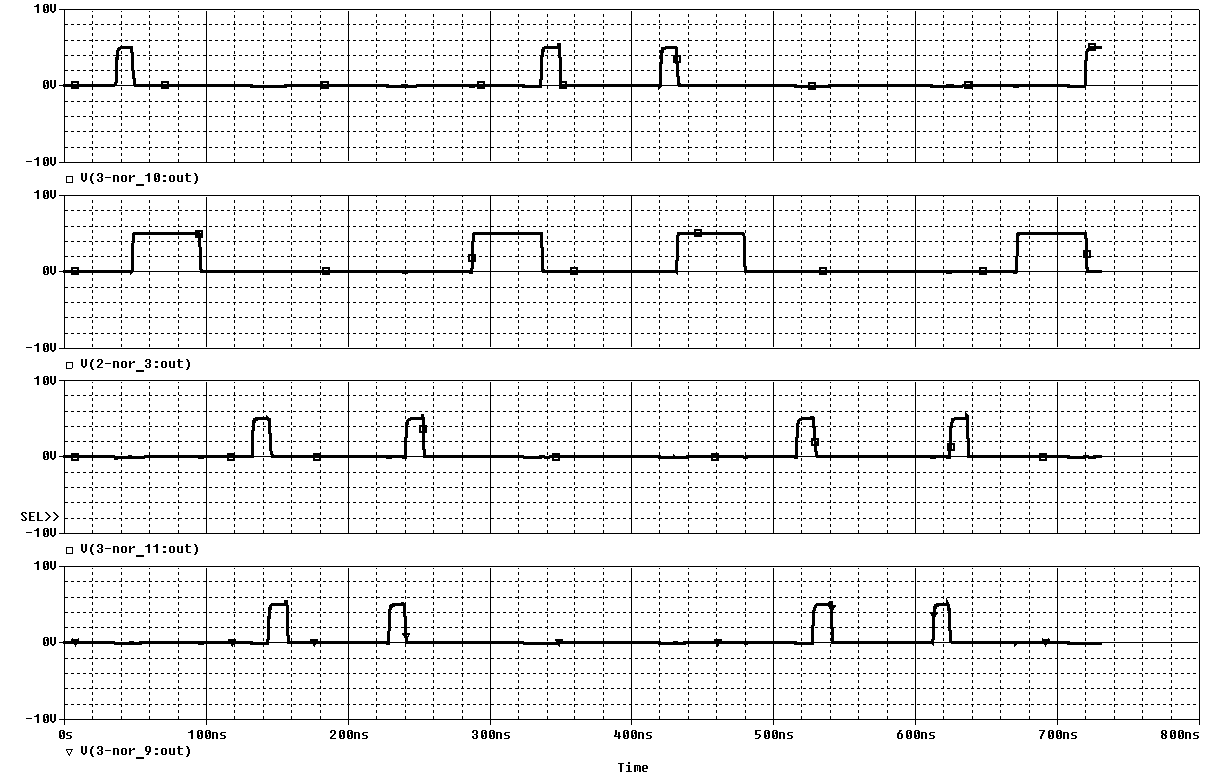

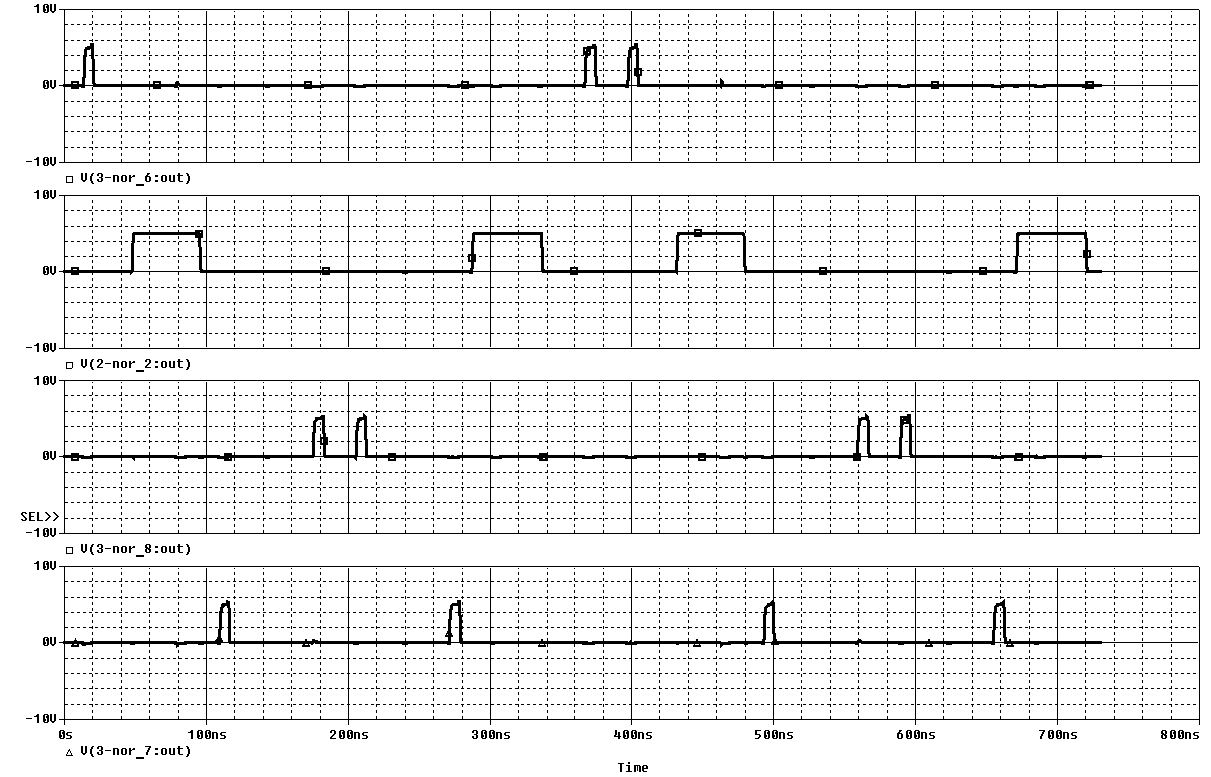

Результаты расчета переходных процессов в логических элементах в программе Schematics:

1) Инвертор:

2)

2ИЛИ-НЕ:

2)

2ИЛИ-НЕ:

3) 3ИЛИ-НЕ:

Задержки

на элементах:

Задержки

на элементах:

|

|

инвертор |

2ИЛИ-НЕ |

3ИЛИ-НЕ |

|

t10 , нс |

0,127 |

0,43 |

1,108 |

|

t01 , нс |

0,08 |

0,319 |

0,3 |

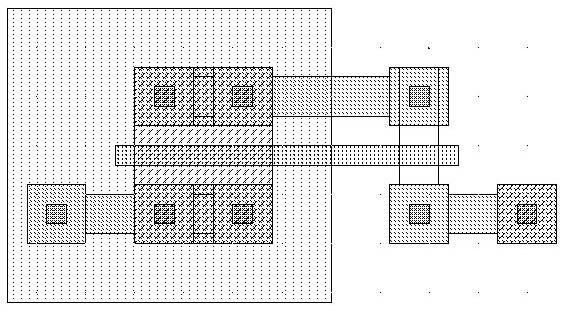

Топология логических элементов:

1) Инвертор:

Топологическая

площадь составляет:

![]()

2) 2ИЛИ -НЕ:

-НЕ:

Топологическая

площадь составляет:

![]()

3) 3ИЛИ-НЕ:

Топологическая

площадь составляет:

![]()

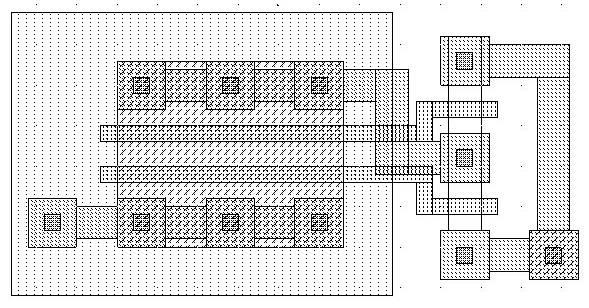

4) Топология всего устройства:

Топологическая площадь составляет:

![]()

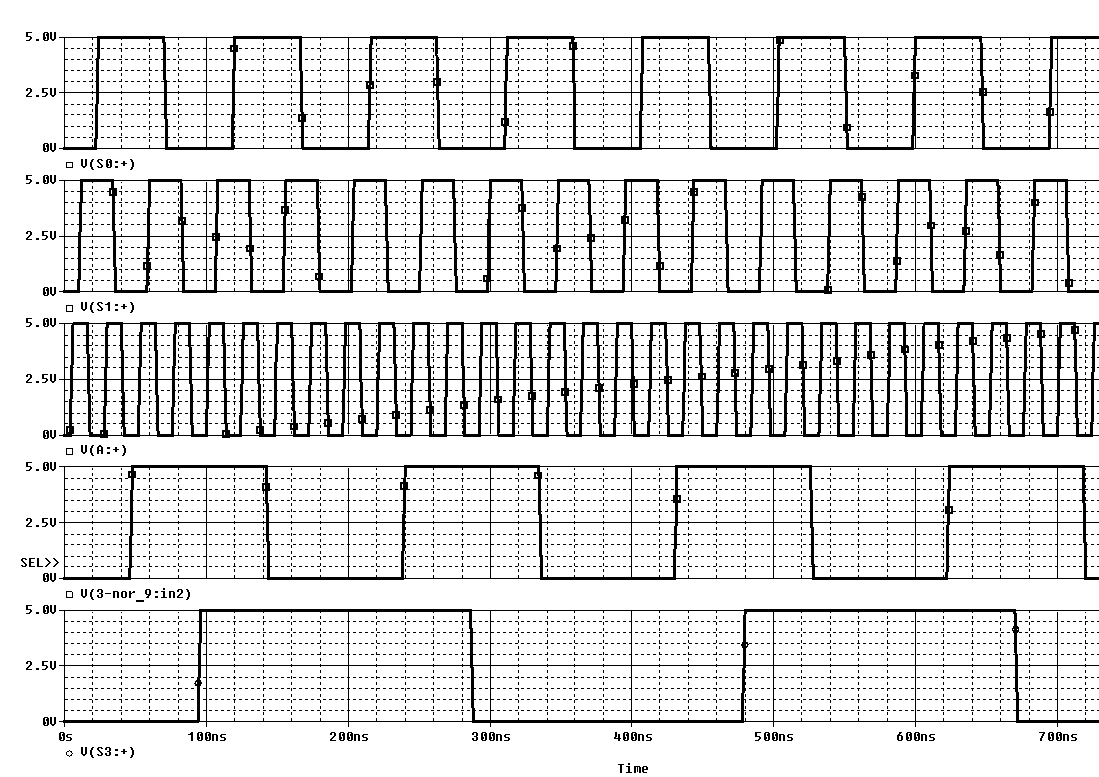

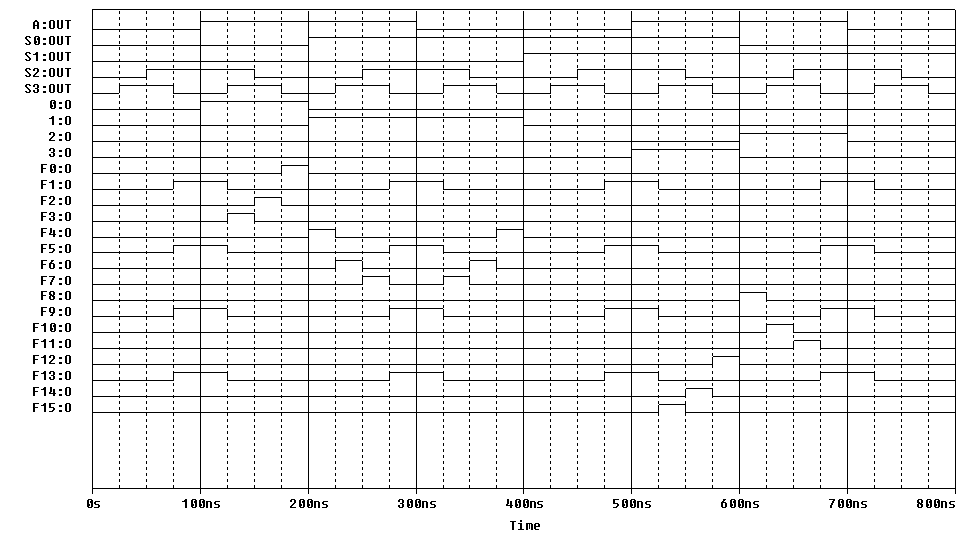

Результаты моделирования устройства в целом в программе Schematics

Входной сигнал:

Выходной сигнал:

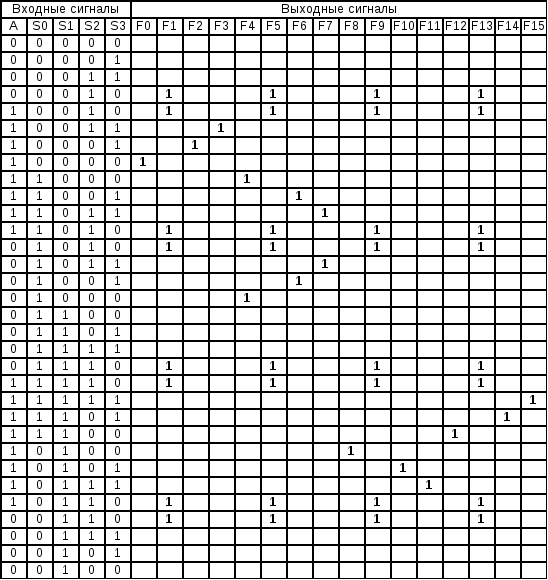

Результаты логического моделирования:

Таблица истинности:

Выводы

В итоге разработки устройства мы получили следующее:

- элемент Инвертор

имеет топологическую площадь равную

![]()

![]() ,

,

![]() ;

;

- элемент 2ИЛИ-НЕ

имеет топологическую площадь равную

![]()

![]() ,

,

![]() ;

;

- элемент 3ИЛИ-НЕ

имеет топологическую площадь равную

![]()

![]() ,

,

![]() ;

;

- общая площадь

устройства равна

![]() .

.