Комп тех и сети / Методички ВТиИТ / Полусумматор и сумматор

.docЛабораторная работа №6

Полусумматор и сумматор

Цель работы: построить схемы полусумматора и сумматора. Исследовать принцип их работы.

Ход работы:

-

Построить модель полусумматора.

Полусумматор — логическая схема, имеющая два входа и два выхода (двухразрядный сумматор, бинарный сумматор). Полусумматор используется для построения двоичных сумматоров. Полусумматор позволяет вычислять сумму A+B, где A и B — это разряды двоичного числа, при этом результатом будут два бита S,C, где S — это бит суммы по модулю, а C — бит переноса. Может "считать до двух".

Рисунок 1.1 - Схема полусумматора

-

Подготовить таблицу истинности.

-

Используя генераторы единичных логических импульсов и наблюдая за состоянием полусумматора по значениям логических тестеров заполнить таблицу истинности.

-

По результатам наблюдений построить временную диаграмму.

-

Построить модель сумматора.

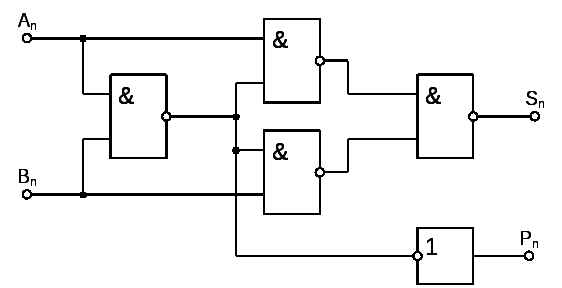

Сумматор (двоичный) - логическая схема, имеющая 3 входа и два выхода. Отличается от полусумматора тем, что может "считать до трех", т.е. на выходе может присутствовать комбинация Sn=Pn=1.

Рисунок 5.1 - Схема сумматора

На схеме элемент MS - полусумматор.

-

Выполнить пункты 2,3,4.