схемотехника лаб.работы / схемотехника лаб.работы / laba_5

.pdfЛАБОРАТОРНАЯ РАБОТА №5 «Исследование сумматоров»

5.1 ЦЕЛЬ РАБОТЫ:

-Ознакомится с назначением и принципом действия сумматоров; -Ознакомится с практической схемой сумматора и исследовать еѐ;

5.2 ПРИБОРЫ И ЭЛЕМЕНТЫ:

-учебный стенд;

-соединительные проводники.

5.3 КРАТКИЕ СВЕДЕНИЯ ИЗ ТЕОРИИ:

5.3.1. Сумматоры

Сумматоры представляют собой функциональные узлы, выполняющие операцию сложения чисел. В устройствах дискретной техники суммирование осуществляется в двоичном или, реже, в двоично-десятичном коде. По характеру действия сумматоры подразделяются на две категории: комбинационные – как и все ранее рассмотренные узлы, не имеющие элементов памяти; накопительные – сохраняющие результаты вычислений. В свою очередь, каждый из сумматоров, оперирующий с многоразрядными слагаемыми, в зависимости от способа обработки чисел может быть отнесен к последовательному или параллельному типу.

Сумматоры, выполненные в виде самостоятельных микросхем – комбинационные, и речь в дальнейшем будет идти только о них.

Как последовательные, так и параллельные сумматоры строятся на основе одноразрядных суммирующих схем. Сложение чисел в последовательных сумматорах осуществляется поразрядно, последовательно во времени. В сумматорах параллельного типа действия сложение всех разрядов много разрядных чисел происходит одновременно.

5.3.2. Полусумматор

Простейшим суммирующим элементом является полусумматор. Происхождение этого термина станет ясным в ходе изложения. Он имеет (см рис. ) два входа А и В для двух слагаемых и два выхода : S(сумма) и P(перенос). Обозначением полусумматора служат буквы HS (HalfSum – полусумма), работу прибора отражает таблица истинности :

|

Входы |

Выходы |

|

|

A |

|

B |

P |

S |

0 |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

0 |

0 |

1 |

1 |

|

1 |

1 |

0 |

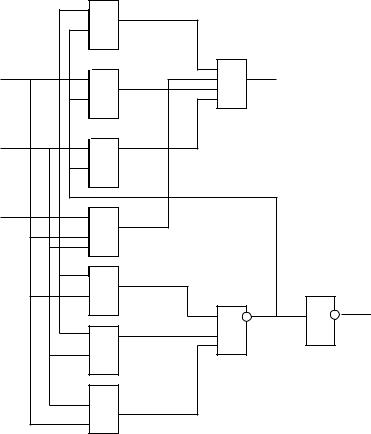

Полусумматор имеет два входа и пригоден для использования только в младших разряде. Устройство для суммирования многоразрядных чисел должно иметь, начиная со второго разряда, три входа (см. рис. 5.1): два для слагаемых Ai и Bi и один для сигнала переноса Pi-1 с предыдущего разряда. Этот узел – сумматор можно представить как объединение двух полусумматоров:

&

A

1 S

&

B

&

Pi-1

&

&

P

1

1

&

&

Рис. 5.1.

Первый полусумматор служит для сложения двух чисел, принадлежащих одному разряду, и обеспечивает выход промежуточной суммы Si и переноса Pi. Второй полусумматор складывает перенос с предыдущего разряда Pi-1 с промежуточной суммой

Si. Функции выходов S и P для этого случая определяется как: |

|

|||

S=(A+B)+Pi-1; |

|

|

(5.1) |

|

Pi+1=AiBi ^ (A+B) Pi-1 |

|

(5.2) |

||

Операции сложения подчиняется переносительному закону, из которого следует, что |

||||

входы сумматора можно менять местами без ущерба для результата. |

|

|||

Исходя из таблицы истинности сумматора, можно написать следующие булевы |

||||

уравнения для сигналов суммы и переноса: |

|

|||

_ _ |

_ |

__ |

_ __ |

|

Si=AiBiPi-1 ^ AiBiPi-1 ^ AiBiPi-1 ^ AiBiPi-1 |

(5.3) |

|||

_ |

|

_ |

__ |

|

Pi=AiBiPi-1 ^ AiBiPi-1 ^ AiBiPi-1 ^ AiBiPi-1 |

(5.4) |

|||

В уравнениях 5.3 и 5.4 представлены только те члены, для которых Si=1 и Pi=1, т.е. первый член функции Si относится к первой строке таблицы истинности, второй член ко второй и т.д. Сходным образом для функции P первый член принадлежит третей строке,

второйпятой и так до седьмой. |

|

||

Уравнения 5.3 и 5.4 поддаются оптимизации, в результате которой получается: |

|

||

_ |

_ |

_ |

|

Si = AiPi ^ BiPi ^ Pi-1Pi ^ AiBiPi-1 |

(5.5) |

||

Pi = BiPi-1 ^ AiPi-1 ^ AiBi |

(5.6) |

||

Легко убедится, что оба уравнения удовлетворяют таблице истинности, как и уравнения 5.3 и 5.4. Это следует прямо из данных таблицы истинности, а именно из того, что Pi=1, если по меньшей мере на двух входах из трѐх присутствует 1. Так же можно показать отсутствие в уравнении 6 члена AiBiPi, характеризующего последнюю строку таблицы истинности, т.к. достаточно двум его членам быть равными 1.

В микросхемах-сумматорах в качестве базового узла используется сумматор, логическая структура которого реализована на основе формул 5.5 и 5.6.

Как уже говорилось, суммирование многоразрядных чисел может быть последовательное либо параллельное. При последовательном вводе используется один, общий для всех разрядов полный сумматор с дополнительной цепью задержки. Оба слагаемых кодируются последовательностями импульсов, которые синхронно вводятся в

сумматор через входы A и B, начиная с младших разрядов. Цепь задержки обеспечивает хранение импульса переноса Pi+1 на время одного такта, т.е. до прихода пары слагаемых следующего разряда, с которыми он будет просуммирован. Задержку обеспечивает D- триггер (триггер задержки). Для хранения и ввода слагаемых А и В, а так же для преобразования последовательного кода выходных импульсов в параллельный применяют регистры сдвига. Работа регистров и схемы задержки синхронизируется общим генератором тактовых импульсов.

Достоинство последовательных сумматоров – малые аппаратные затраты. К недостаткам их следует отнести сравнительно невысокое быстродействие, поскольку одновременно суммируется лишь пара слагаемых.

Принцип действия n-разрядного параллельного сумматора с последовательным переносам следующий. Число сумматоров равно числу разрядов. Выход переноса P каждого сумматора соединен со входом переноса следующего, более старшего разряда. На входе переноса сумматора первого разряда установлен потенциал U0, поскольку сигнал переноса сюда не поступает. Слагаемые Ai и Bi складывается во всех разрядах одновременно, а перенос P поступает с окончанием операций сложения в предыдущем разряде.

Быстродействие многоразрядных сумматоров подобного вида ограничено задержкой переноса, т.к. формирование сигнала переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса с младшего разряда не распространится по всей системе.

Время переноса можно уменьшить, вводя параллельный перенос, для чего используются специальные узлы – блоки ускоренного (сквозного) переноса. Их принцип заключается в том, что для каждого двоичного разряда дополнительно находятся два сигнала : образование переноса G и его распространение H. Эти функции определяются следующим образом :

Gi = AiBi |

(5.7) |

Hi=Ai^Bi |

(5.8) |

В случае Gi=1, т.е. Ai=Bi=1, в данном i-ом разряде формируется сигнал переноса Pi в следующий высший разряд независимо от формирования функций суммы в предыдущих. Если хотя бы одно из слагаемых Ai или Bi равно 1 (Hi=1), то перенос в последующий разряд произойдет при наличии сигнала переноса из предыдущего. Если функции распространения в двух соседних разрядах равны 1, и при этом существует перенос Pi-1 из предыдущего разряда, то перенос производится непосредственно в разряд номер i+2.

Процесс формирования ускоренного переноса описывается следующим уравнением :

Pi=Gi ^ HiGi-1 ^ HiHi-1Gi-2 ^ … ^ HiHi-1…H2H1P0 |

(5.9) |

5.4 КОНТРОЛЬНЫЕ ВОПРОСЫ :

1.Для чего предназначены сумматоры, и каких типов они бывают?

2.Начертите схему полного одноразрядного сумматора и поясните его работу.

3.На каких логических элементах могут быть реализованы сумматоры?

4.Поясните назначение выхода переноса в одноразрядном сумматоре.

5.Сложение многоразрядных чисел.

5.5 ПОРЯДОК ПРОВЕДЕНИЯ ЭКСПЕРИМЕНТОВ:

Исследование четырехразрядного двоичного сумматора.

Схема четырехразрядного двоичного сумматора изображена на рис. 5.4. Переведите числа, заданные по варианту в двоичную систему исчисления, записав их в 8-разрядном формате. Произведите сложение полученных 8-разрядных двоичных чисел в два этапа: суммируйте младшие полубайты (тетрады), затем, с учетом переноса, суммируйте старшие полубайты. Заполните таблицы сложения младших и старших полубайтов.

|

Таблица заданий |

|

|

|

|

Вариант |

Числа (десятичное представление) |

|

1 |

150+11 |

|

2 |

230+10 |

|

3 |

38+100 |

|

4 |

45+28 |

|

5 |

184+9 |

|

6 |

120+28 |

|

7 |

56+123 |

|

8 |

200+55 |

|

9 |

120+30 |

|

10 |

101+34 |

|

Рис. 5.4.

5.6 РЕЗУЛЬТАТЫ ЭКСПЕРИМЕНТОВ:

Исследование четырехразрядного двоичного сумматора.

Число A в двоичной системе |

|

|

|

|

|

|

|

||||||||||||||||

A7 |

|

A6 |

|

A5 |

|

A4 |

|

A3 |

|

A2 |

|

A1 |

|

A0 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Число B в двоичной системе |

|

|

|

|

|

|

|

||||||||||||||||

B7 |

|

B6 |

|

B5 |

|

B4 |

|

B3 |

|

B2 |

|

B1 |

|

B0 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Суммирование младшего полубайта: |

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Cin |

|

|

|

|

A3 |

|

A2 |

|

A1 |

|

A0 |

|

|

|

|

|

|

|

|||||

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

B3 |

|

B2 |

|

B1 |

|

B0 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Cout |

|

|

|

|

S3 |

|

S2 |

|

S1 |

|

S0 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|||||||||||||||

Суммирование старшего полубайта: |

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Cin |

|

|

|

|

A3 |

|

A2 |

|

A1 |

|

A0 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

B3 |

|

B2 |

|

B1 |

|

B0 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Cout |

|

|

|

|

S3 |

|

S2 |

|

S1 |

|

S0 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Результат: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

Cout |

|

S7 |

|

S6 |

|

S5 |

|

S4 |

|

S3 |

|

S2 |

|

S1 |

S0 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|