-

МИНИСТЕРСТВО ОБЩЕГО И ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

КУРСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

КАФЕДРА ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ

Моделирование микропрограмм выполнения арифметических операций. Операции сложения и вычитания чисел

в двоичной системе счисления,

заданных в прямых кодах

Методические указания

к лабораторным работам по дисциплине:

Теория вычислительных процессов

(спец. 22.01)

Курск 1999

Составитель И.Е. Чернецкая

УДК

Моделирование микропрограмм выполнения арифметических операций. Операции сложения и вычитания чисел в двоичной системе счисления, заданных в прямых кодах: Методические указания к лабораторной работе по дисциплине «Теория вычислительных процессов» для студентов специальности 22.01/ Курск. гос. техн. ун-т; Сост. И.Е. Чернецкая. Курск, 1999. 13 с.

Излагаются методические указания по подготовке лабораторной работы.

Предназначены для студентов специальностей 22.01 «ЭВМ, комплексы, системы и сети»

Библиогр.: 2 назв.

Рецензент

Редактор

ЛР № от

Подписано в печать . Формат 6084 1/16. Печать офсетная.

Усл. печ. л. . Уч.-изд. л. . Тираж экз. Заказ .

Курский государственный технический университет.

Подразделение оперативной полиграфии Курского государственного технического университета.

Адрес университета и подразделения оперативной полиграфии:

305040 Курск, ул. 50 лет Октября, 94.

Оглавление

1.Цель работы………………………………………………….4

2.Теоретические основы………………………………………4

3.Порядок выполнения лабораторной работы……………….7

4.Содержание отчета………………………………………….12

5.Контрольные вопросы………………………………………13

-

Цель работы

Цель данной лабораторной работы является моделирование микропрограммы выполнения операций арифметического сложения и вычитания чисел в двоичной системе счисления, заданных в прямых кодах.

-

Теоретические основы

Интенсивное развитие информатики с ее алгоритмическими и техническими проблемами основывается на первичных построениях, связанных с разработкой алгоритмов и их аппаратной поддержки для выполнения арифметических операций в рамках архитектуры фон Неймана.

Архитектура фон Неймана отражает последовательные способы выполнения операций с параллелизмом работы арифметико-логического устройства в соответствии с заданной разрядной сеткой и формой представления чисел. Еще одной особенностью рассматриваемой архитектуры является поадресное обращение к запоминающему устройству с обменом по длине разрядной сетки. Два основных достоинства машин с указанной архитектурой:

-

простота структуры технических средств;

-

универсальность.

В данном методическом указании будет рассматриваться алгоритм, который выполняется с использованием единственного параллельного сумматора, регистров общего назначения и регистров с многофункциональной аппаратной поддержкой (сдвиг, кодовые преобразования, счетчик и т.д). В данной лабораторной работе мы будем иметь дело с операндами и результатами операций, представленных в прямых кодах, преобразовываться могут оба операнда, в сумматоре используется дополнительный код.).

Прямой код числа А=-0,001101 – машинное изображение [А]пр=1,001101 (все цифровые разряды отрицательного числа остаются неизменными, а в знаковой части записывается единица). Положительное число в прямом коде не меняет своего изображения, т.е правила преобразования чисел в прямой код записываются в следующем виде

Дополнительный код числа является математическим дополнением основанию системы счисления

![]() ,

,

где q – основание системы счисления.

Положительные числа не меняют своего изображения в дополнительном коде и правила преобразования в дополнительный код записываются следующим образом:

Дополнительным кодом числа А=-0,101110 является число [А]д=1,010010, т.е. инвертируется каждый значащий разряд, за исключением последнего значащего разряда, для которого инвертирование не производится.

Операция выполняется в три этапа: вначале в нужных случаях преобразуются один или оба операнда из прямого в дополнительный код, производится сложение на сумматоре и затем полученный результат преобразуется из дополнительного в прямой код.

Операнд А преобразуется при операциях А+В, А-В, если А – отрицательно.

Операнд В преобразуется при операциях А+В если В- отрицательно, и при операции А-В, если В – положительно.

Отрицательные числа поступают на сумматор в дополнительном коде.

Рассмотрим возможные случаи, в которых не возникает переполнения разрядной сетки, что позволяет складывать автоматные изображения чисел по правилам двоичной арифметики, не разделяя знаковую и цифровую части:

-

А>0, В>0, А+В<1.

Так как

![]() ,

,

![]() то

то

![]() - результат положительный.

- результат положительный.

-

А<0, В>0, А>В.

Здесь![]() ,

,

![]() .

Таким образом, в результате арифметического

сложения получится, что

.

Таким образом, в результате арифметического

сложения получится, что

![]() - результат отрицательный.

- результат отрицательный.

-

А<0, В>0, А<В.

Здесь![]() ,

,

![]() .

Таким образом, в результате арифметического

сложения получится, что значение этой

суммы больше q, и появляется единица

переноса из знакового разряда, что

равносильно изъятию из суммы q

единиц и результат равен

.

Таким образом, в результате арифметического

сложения получится, что значение этой

суммы больше q, и появляется единица

переноса из знакового разряда, что

равносильно изъятию из суммы q

единиц и результат равен

![]() .

.

-

А<0, В<0, А+В<1

Здесь![]() ,

,

![]() .

В результате арифметического сложения

получится:

.

В результате арифметического сложения

получится:

![]() - результат отрицательный. В данном

случае появляется единица переноса из

знакового разряда.

- результат отрицательный. В данном

случае появляется единица переноса из

знакового разряда.

3. Порядок выполнения лабораторной работы

Выбирается число разрядов исходных операндов и число разрядов сумматора (таблица 1), в зависимости от заданного варианта.

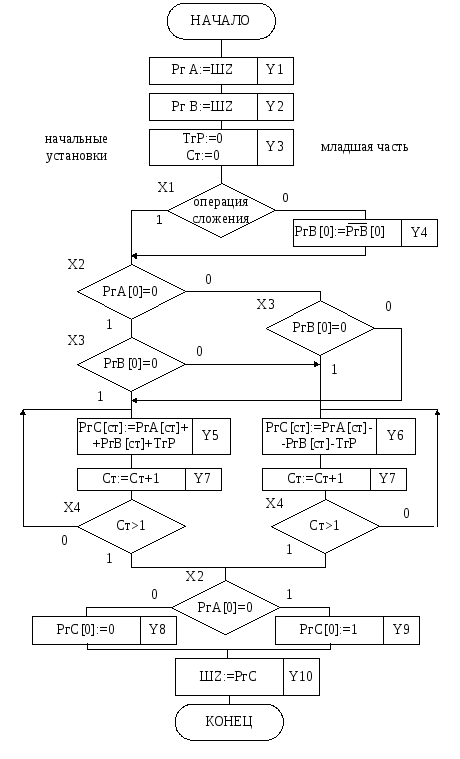

Описывается содержательный алгоритм (совокупная схема) выполнения арифметических операций сложения и вычитания, рисунок 1. В качестве примера, представлена содержательная граф-схема для разрядности операндов равной 8 разрядам и разрядности сумматора равной 4-м., учитывая следующие ограничения.

-

Операнд, записанный в регистре А, по модулю больше операнда регистра В

А>В.

-

При алгебраическом сложении и вычитании в результате не должно быть переполнения разрядной сетки.

-

Вычитание числа В из числа А выполняется по следующему правилу

А-В=А+(-В).

Производится кодирование микроопераций и условий (рисунок 1).

Таблица 1 – Разрядность операндов и сумматора

-

Номер варианта

Разрядность операндов

Разрядность сумматора

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

8

16

32

8

16

32

8

16

32

8

16

32

8

16

32

8

16

32

8

16

32

8

16

32

8

16

32

8

16

32

8

16

32

2

2

2

4

4

4

8

8

8

2

2

2

4

4

4

8

8

8

2

2

2

4

4

4

8

8

8

2

2

2

4

4

4

Р исунок

1 – Содержательный алгоритм (совокупная

схема)

исунок

1 – Содержательный алгоритм (совокупная

схема)

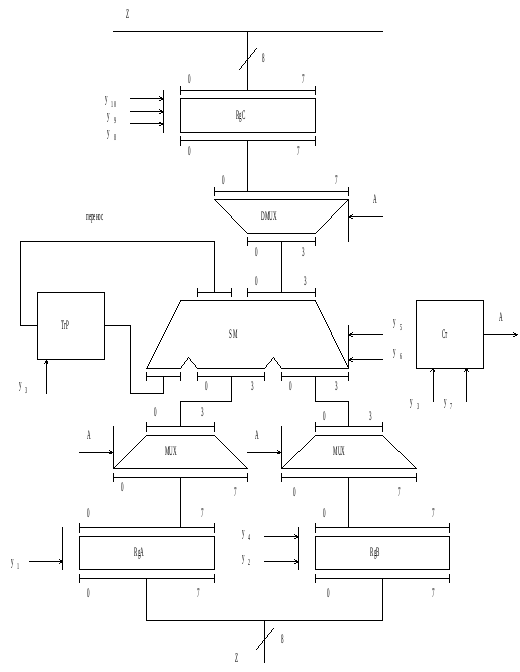

Р исунок

2 – Структурный операционный автомат

для выполнения операции сложения

вычитания

исунок

2 – Структурный операционный автомат

для выполнения операции сложения

вычитания

Проектируется операционный автомат арифметико-логического устройства, представленный на рисунке 2. В регистры RgA и RgB производится запись чисел, заданных в прямых кодах, поступающих с шины Z. В RgC записывается результат операции сложения и вычитания чисел в двоичной системе счисления с использованием дополнительного кода. На шину Z поступает результат арифметической операции, заданный в прямом коде. В триггер переноса ТгР производится запись переноса из младшей части числа в старшую. Счетчик Ст вырабатывает управляющую информацию для мультиплексоров MUX и демультиплексора DMUX.

Производится описание микрокоманд и условий.

y1: RgA:=ШZ;

y2: RgB:= ШZ

y3: ТгР:=0; Ст:=0;

y4: RgB[0]:= RgB[0];

y5: RgC[ст];= RgA[ст] +RgB[ст]+ТгР;

y6: RgC[ст];= RgA[ст] -RgB[ст]-ТгР;

y7:Ст:=Ст+1;

y8: RgC[0]:=0;

y9: RgC[0]:=1;

y10: ШZ:=RgC;

x1: определение операции;

x2: RgA[0];

x3: RgB[0];

x14:Ст>1.

Затем производится программирование математической модели арифметических операций сложения вычитания чисел, заданных в прямых кодах с использованием дополнительных кодов на языке высокого уровня.

Математическая модель строится исходя из следующих ограничений.

-

Входные и выходные данные представляют собой двоичные векторы с заданной разрядностью.

-

Каждое устройство, включенное в схему операционного автомата, должно быть представлено в виде подпрограммы (функции, модуля).

-

Головная часть программы должна включать в себя последовательность микрокоманд и условных операторов и предусматривать возможности просмотра промежуточных результатов.

4. Содержание отчета

-

Задание на лабораторную работу.

-

Содержательный алгоритм выполнения арифметических операций.

-

Структура операционного автомата выполнения арифметических операций сложения и вычитания чисел, заданных в ПК.

-

Составленный список микрокоманд и условий.

-

Разработанная программа на алгоритмическом языке высокого уровня, моделирующая полученную микропрограмму.

-

Составленные тестовые примеры для различных соотношений знаков операндов.

-

Выводы по работе.

5. Контрольные вопросы

-

Написать изображения чисел –31,-5,-18, 45 в прямом и дополнительном кодах в двоичной системе счисления.

-

Вычесть из числа –6 число 9, предварительно представив их в двоичной системе счисления.

-

С

ложить

на сумматоре дополнительного кода

числа –28 и 45, предварительно представив

их в двоичной системе счисления.

ложить

на сумматоре дополнительного кода

числа –28 и 45, предварительно представив

их в двоичной системе счисления.

-

Майоров С.А., Новиков Т.И. структура электронных вычислительных машин. - Л.: машиностроение,1979.-384 с.

-

Савельев А.Я. Прикладная теория цифровых автоматов: Учеб. Для вузов по спец. ЭВМ. –М.: Высшая школа, 1987. –272 с.