- •«Теория дискретных устройств автоматики и телемеханики в электроснабжении» курс лекций

- •Введение

- •1. Математическое описание дискретных устройств

- •1.1. Системы счисления

- •1.2. Дискретные сигналы

- •1.3. Логические константы и переменные. Логические операции. Логические элементы

- •1.4. Классификация логических устройств

- •1.5. Способы записи функций алгебры логики

- •1.6. Структурная схема логического устройства

- •1.7. Принцип двойственности

- •1.8. Теоремы алгебры логики

- •2. Минимизация функций алгебры логики

- •2.1. Цель минимизации фал

- •2.2. Способ представления фал с использованием карт Вейча – Карно

- •2.3. Минимизация полностью определённой фал

- •2.4. Минимизация недоопределённой фал

- •2.5. Минимизация системы фал

- •3. Техническая реализация логических устройств на реальной элементной базе

- •3.1. Техническая реализация лу на электромагнитных реле

- •3.2. Техническая реализация лу на базе диодной матрицы

- •3.3. Техническая реализация лу на цифровых микросхемах

- •4. Типовые функциональные узлы комбинационных логических устройств

- •4.1. Мультиплексор

- •4.2. Демультиплексор

- •4.3. Шифратор

- •4.4. Дешифратор

- •4.5. Цифровой компаратор

- •4.6. Функция «Исключающее или»

- •4.7. Логические элементы, реализующие сложные функции

- •5. Триггеры

- •5.1. Асинхронный rs-триггер

- •5.2. Синхронный rs-триггер

- •5.3. D-триггер

- •5.4. Т-триггер

- •5.5. Двухступенчатый т-триггер

- •5.6. Двухступенчатый синхронный jk-триггер

- •5.7. Триггер с динамическим управлением

- •6. Счётчики

- •6.1. Двоичный суммирующий счётчик

- •6.2. Двоичный вычитающий счётчик

- •6.3. Двоично-кодированный счётчик

2.4. Минимизация недоопределённой фал

ФАЛ называется недоопределённой (частично определённой), если часть её значений yiне задана (см. п. 1.5). При минимизации такой ФАЛ необязательным значениям, которые обычно обозначают *, можно произвольно присваивать единичные или нулевые значения из условия получения на карте ВейчаКарно минимального числа максимально больших областей.

Рассмотрим пример минимизации ФАЛ, заданной таблицей истинности:

|

Х3 |

Х2 |

Х1 |

Х0 |

Y |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

* |

|

0 |

0 |

1 |

0 |

* |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

* |

|

0 |

1 |

0 |

1 |

* |

|

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

* |

|

1 |

0 |

0 |

0 |

* |

|

1 |

0 |

0 |

1 |

* |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

* |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

* |

|

1 |

1 |

1 |

0 |

* |

|

1 |

1 |

1 |

1 |

0 |

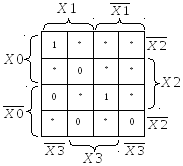

Составим карту Вейча – Карно.

Как видно из карты, ни единичные, ни нулевые значения ФАЛ невозможно объединить друг с другом. Поэтому ДНФ имеет вид

![]() ,

(2.5)

,

(2.5)

а КНФ

![]() .

(2.6)

.

(2.6)

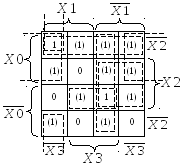

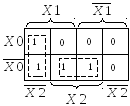

Предположим, что для доопределения ФАЛ принято решение присвоить всем необязательным значениям функции единичные значения. В результате получим следующий вид карты, на которой выделены области единичных значений, и соответствующую МДНФ.

|

|

|

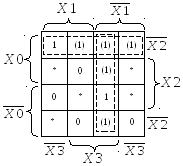

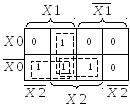

Очевидно, что такое решение привело к отрицательному результату. Полученная МДНФ оказалась даже сложнее исходной ДНФ (2.5). Поэтому проведём новое доопределение ФАЛ, добавив единичные значения функции только для получения на карте Вейча Карно минимального числа максимально больших областей.

|

|

|

Поскольку выделить область из восьми клеток не удалось, выбрано решение о выделении двух областей из четырёх клеток каждая. Полученное выражение МДНФ проще исходной ДНФ и требует для своей реализации два инвертора, два элемента 2И и один элемент 2ИЛИ.

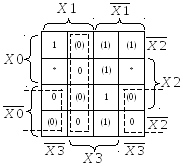

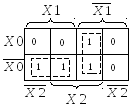

Теперь проведём доопределение ФАЛ, добавив нулевые значения функции только для получения на карте Вейча Карно минимального числа максимально больших областей.

|

|

|

Аналогично выделяем две области по четыре клетки в каждой, поскольку выделить область из восьми клеток невозможно. Полученное выражение для МДНФ, инверсной заданной, также содержит логическую сумму двух логических произведений. Для реализации потребуется три инвертора (два для переменных и один для функции), два элемента 2И и один 2ИЛИ.

Для дальнейших преобразований воспользуемся теоремой Де-Моргана:

![]() .

.

В результате получилось выражение существенно проще, чем исходная КНФ (2.6), для реализации которого потребуется два инвертора, два элемента 2ИЛИ и один элемент 2И. Следует также отметить, что в варианте МКНФ не нужна переменная Х2.

Окончательный выбор варианта технической реализации ФАЛ будет зависеть от типа заданных (или имеющихся в наличии) ЛЭ.

2.5. Минимизация системы фал

Если логическое устройство имеет mвыходов, то его структура описывается системойmФАЛ. Минимизация структуры такого устройства может быть выполнена с использованием метода карт Вейча – Карно раздельно для каждого выхода. При этом может оказаться, что структура всего устройства получится неоптимальной.

Достижение оптимального результата может быть реализовано выделением в каждом выражении одинаковых импликант, то есть выделением на картах одинаковых областей. Сформировав такую импликанту только один раз, можно использовать её для нескольких из mуравнений, сократив, таким образом, общее число логических элементов в технической реализации логического устройства.

Рассмотрим пример минимизации системы ФАЛ из трёх функций Y1,Y2,Y3 для трёх переменныхX2,X1,X0 [1], заданных таблицей истинности.

|

X2 |

X1 |

X0 |

Y3 |

Y2 |

Y1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

0 |

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

Составим карты Вейча – Карно и проведём минимизацию для получения МДНФ раздельно для каждого выхода.

|

|

|

|

|

|

|

|

|

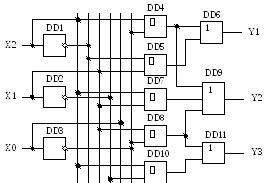

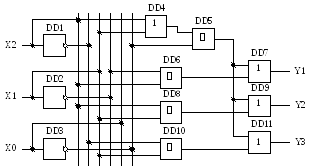

Техническая реализация системы ФАЛ, уравнения которой получены раздельно для каждого выхода, потребует три инвертора, семь элементов 2И, два элемента 2ИЛИ и один элемент 3ИЛИ, то есть всего 13 элементов.

Если

проанализировать полученные уравнения,

можно выделить в них общие члены

![]() и

и![]() .

Сформировав их только один раз, можно

упростить техническую реализацию

системы ФАЛ. В этом случае потребуется

три инвертора, пять элементов 2И, два

элемента 2ИЛИ и один элемент 3ИЛИ, то

есть всего 11 элементов. Структурная

схема такого логического устройства

представлена на рис. 2.4.

.

Сформировав их только один раз, можно

упростить техническую реализацию

системы ФАЛ. В этом случае потребуется

три инвертора, пять элементов 2И, два

элемента 2ИЛИ и один элемент 3ИЛИ, то

есть всего 11 элементов. Структурная

схема такого логического устройства

представлена на рис. 2.4.

|

|

Рис. 2.4. Структурная схема ЛУ для Y1, Y2 и Y3

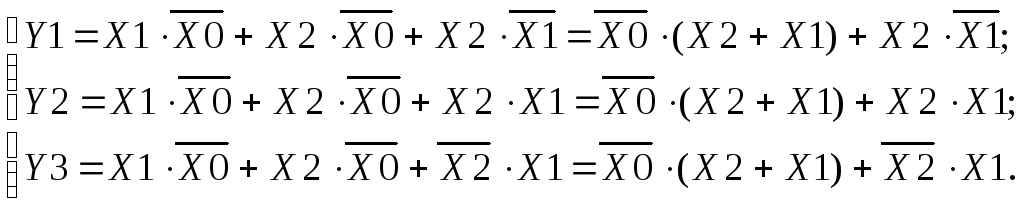

Нетрудно

заметить, что для Y1

не использована область![]() ,

а дляY3область

,

а дляY3область![]() .

Эти области при раздельной минимизации

получаются лишними. Но если стремиться

к получению наилучшего результата

минимизации системы ФАЛ, можно добавить

эти импликанты в соответствующие

уравнения, а затем провести дополнительные

преобразования по теоремам алгебры

логики:

.

Эти области при раздельной минимизации

получаются лишними. Но если стремиться

к получению наилучшего результата

минимизации системы ФАЛ, можно добавить

эти импликанты в соответствующие

уравнения, а затем провести дополнительные

преобразования по теоремам алгебры

логики:

(2.7)

(2.7)

Реализация такой схемы логического устройства потребует три инвертора, четыре элемента 2И и четыре элемента 2ИЛИ, то есть тоже 11 элементов. Однако из схемы исключается элемент 3ИЛИ, что является преимуществом, так как упрощает реализацию. Структурная схема такого логического устройства представлена на рис. 2.5.

|

|

Рис. 2.5. Структурная схема ЛУ для Y1, Y2 и Y3 по выражению (2.7)

Контрольные вопросы

1. В чём заключается цель минимизации логических устройств?

2. Почему реализация логического устройства по ДНФ или КНФ, полученным непосредственно из таблицы истинности, не будет оптимальной?

3. Почему преобразования по теоремам алгебры логики не всегда могут обеспечить получение минимальной технической реализации логического устройства?

4. Что такое карта Вейча – Карно?

5. Приведите примеры карт Вейча – Карно для двух, трёх и четырёх переменных.

6. Приведите алгоритм минимизации ФАЛ с помощью карт Вейча – Карно.

7. Что такое импликанта?

8. В чём заключается порядок минимизации недоопределённой ФАЛ?

9. Почему замена всех необязательных значений недоопределённой ФАЛ может привести к отрицательному результату минимизации?

10. Почему желательно проводить минимизацию и по единичным и по нулевым значениям ФАЛ?

11. Каковы особенности минимизации системы ФАЛ?

12. Почему минимизация системы ФАЛ раздельно для каждого выхода может привести к неоптимальному результату технической реализации логического устройства в целом?