- •«Теория дискретных устройств автоматики и телемеханики в электроснабжении» курс лекций

- •Введение

- •1. Математическое описание дискретных устройств

- •1.1. Системы счисления

- •1.2. Дискретные сигналы

- •1.3. Логические константы и переменные. Логические операции. Логические элементы

- •1.4. Классификация логических устройств

- •1.5. Способы записи функций алгебры логики

- •1.6. Структурная схема логического устройства

- •1.7. Принцип двойственности

- •1.8. Теоремы алгебры логики

- •2. Минимизация функций алгебры логики

- •2.1. Цель минимизации фал

- •2.2. Способ представления фал с использованием карт Вейча – Карно

- •2.3. Минимизация полностью определённой фал

- •2.4. Минимизация недоопределённой фал

- •2.5. Минимизация системы фал

- •3. Техническая реализация логических устройств на реальной элементной базе

- •3.1. Техническая реализация лу на электромагнитных реле

- •3.2. Техническая реализация лу на базе диодной матрицы

- •3.3. Техническая реализация лу на цифровых микросхемах

- •4. Типовые функциональные узлы комбинационных логических устройств

- •4.1. Мультиплексор

- •4.2. Демультиплексор

- •4.3. Шифратор

- •4.4. Дешифратор

- •4.5. Цифровой компаратор

- •4.6. Функция «Исключающее или»

- •4.7. Логические элементы, реализующие сложные функции

- •5. Триггеры

- •5.1. Асинхронный rs-триггер

- •5.2. Синхронный rs-триггер

- •5.3. D-триггер

- •5.4. Т-триггер

- •5.5. Двухступенчатый т-триггер

- •5.6. Двухступенчатый синхронный jk-триггер

- •5.7. Триггер с динамическим управлением

- •6. Счётчики

- •6.1. Двоичный суммирующий счётчик

- •6.2. Двоичный вычитающий счётчик

- •6.3. Двоично-кодированный счётчик

6.2. Двоичный вычитающий счётчик

Рассмотрим двоичный вычитающий счётчик до восьми (М = 8). Для схемы такого счётчика также потребуется три триггера. Составим таблицу состояний триггеров счётчика (таблица 6.2).

Таблица 6.2

Таблица состояний триггеров двоичного вычитающего счётчика М = 8

|

№ импульса на входе счётчика |

С |

Q0 |

Q1 |

Q2 |

|

1 |

1 |

1 |

1 |

1 |

|

2 |

1 |

0 |

1 |

1 |

|

3 |

1 |

1 |

0 |

1 |

|

4 |

1 |

0 |

0 |

1 |

|

5 |

1 |

1 |

1 |

0 |

|

6 |

1 |

0 |

1 |

0 |

|

7 |

1 |

1 |

0 |

0 |

|

8 |

1 |

0 |

0 |

0 |

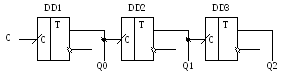

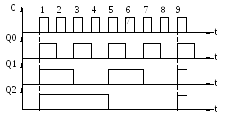

Для реализации такого алгоритма работы следует применить счётный триггер с прямым динамическим входом. В момент поступления на вход счётчика фронта первого импульса все триггеры переключаются. Затем работа триггеров будет стандартной: первый триггер (выход Q0) изменяет своё состояние с приходом каждого импульса на вход С, второй триггер (выходQ1) изменяет своё состояние с приходом каждого второго импульса, третий триггер (выходQ2) изменяет своё состояние с приходом каждого четвёртого импульса. Структурная схема счётчика представлена на рис. 6.4, а временная диаграмма работы – на рис. 6.5.

|

|

Рис. 6.4. Структурная схема двоичного вычитающего счётчика М = 8

|

|

Рис. 6.5. Временная диаграмма работы двоичного вычитающего счётчика М = 8

Счётный триггер с прямым динамическим входом переключается по фронту импульса синхронизации (переключение от логического 0 к логической 1). Поэтому при последовательном соединении триггеров, когда вход следующего подключается к прямому выходу предыдущего, получается счёт на уменьшение. С выходов Q0,Q1 иQ2 можно считывать информацию о количестве подсчитанных импульсов в параллельном коде (в виде трёхразрядного двоичного числа).

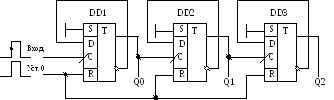

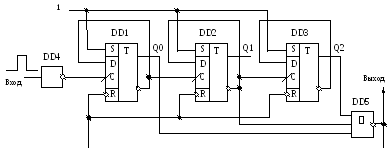

Вычитающие двоичные счётчики в виде отдельных микросхем не выпускаются. Техническая реализация такого счётчика может быть выполнена на D-триггерах К155ТМ2 или К561ТМ2. Пример схемы вычитающего двоичного счётчика наD-триггерах представлен на рис. 6.6.

|

|

Рис.6.6. Схема вычитающего двоичного счётчика на D-триггерах К561ТМ2

6.3. Двоично-кодированный счётчик

Как было отмечено выше, у двоично-кодированного счётчика модуль счёта может принимать любое значение, не равное целой степени числа 2. Для получения такого модуля счёта применяется метод управляемого сброса. Суть метода заключается в принудительном формировании сигнала сброса триггеров схемы двоичного счётчика (установки их в 0) при появлении на выходах счётчика кода, совпадающего с требуемым модулем счёта М. Чтобы добиться этого, необходимо к счётчику добавить дешифратор на логическом элементе И. На входы дешифратора надо подать сигнал с прямого выхода триггера, состояние которого при поступлении на вход счётчика требуемого числа импульсовQ= 1, и с инверсного выхода триггера, состояние которогоQ= 0. Тогда на выходе элемента И будет сформирован сигнал, который следует подать на параллельно соединённые входыRвсех триггеров.

Предположим, что требуется суммирующий счётчик М = 5. Поскольку 22< 5 < 23, для счётчика требуется три триггера. Составим таблицу состояний триггеров такого счётчика (таблица 6.3).

Таблица 6.3

Таблица состояний триггеров двоичного суммирующего счётчика М = 5

|

№ импульса на входе счётчика |

С |

Q0 |

Q1 |

Q2 |

|

1 |

1 |

0 |

0 |

0 |

|

2 |

1 |

1 |

0 |

0 |

|

3 |

1 |

0 |

1 |

0 |

|

4 |

1 |

1 |

1 |

0 |

|

5 |

1 |

0 |

0 |

1 |

|

6 |

1 |

1 |

0 |

1 |

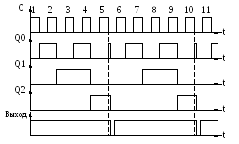

Воспользуемся временной диаграммой работы суммирующего счётчика, отметив на ней состояние выходов триггеров (выходной двоичный код), соответствующий моменту времени после поступления на вход пятого импульса (рис. 6.7). Этот момент времени отмечен пунктирной линией.

Как

только закончится пятый импульс, на

выходах счётчика устанавливается код

101. Чтобы сформировать импульс сброса

триггеров, входы дешифратора на логическом

элементе 3И следует подключить к прямым

выходам Q0 иQ2

и к инверсному выходу![]() .

.

|

|

Рис. 6.7. Временная диаграмма работы двоично-кодированного суммирующего счётчика М = 5

Схема двоичного суммирующего счётчика М = 5 представлена на рис. 6.8. Техническая реализация выполнена на D-триггерах К155ТМ2 с прямым динамическим входом С и инверсными входамиRиS, поэтому входные импульсы проинвертированы, входы С последующих триггеров соединены с инверсными выходами предыдущих, в качестве дешифратора использован логический элемент 3И-НЕ К155ЛА4.

|

|

Рис.6.8. Схема двоично-кодированного счётчика М = 5 на D-триггерах К155ТМ2

Изменяя порядок подключения входов дешифратора, можно получить любой модуль счёта, отличный от целой степени числа 2. Например, в данной схеме, кроме М = 5 можно получить М = 6 и М = 7. Сигнал установки триггеров счётчика в «0» можно использовать как выходной сигнал схемы.

Следует отметить, что при использовании метода управляемого сброса на выходе Q0 на время задержки распространения сигнала в элементеDD5 и времени установления триггера в «0» появляется лишнее выходное состояние («игольчатый» импульс). Это недостаток, который является «расплатой» за универсальность данного метода.