- •«Теория дискретных устройств автоматики и телемеханики в электроснабжении» курс лекций

- •Введение

- •1. Математическое описание дискретных устройств

- •1.1. Системы счисления

- •1.2. Дискретные сигналы

- •1.3. Логические константы и переменные. Логические операции. Логические элементы

- •1.4. Классификация логических устройств

- •1.5. Способы записи функций алгебры логики

- •1.6. Структурная схема логического устройства

- •1.7. Принцип двойственности

- •1.8. Теоремы алгебры логики

- •2. Минимизация функций алгебры логики

- •2.1. Цель минимизации фал

- •2.2. Способ представления фал с использованием карт Вейча – Карно

- •2.3. Минимизация полностью определённой фал

- •2.4. Минимизация недоопределённой фал

- •2.5. Минимизация системы фал

- •3. Техническая реализация логических устройств на реальной элементной базе

- •3.1. Техническая реализация лу на электромагнитных реле

- •3.2. Техническая реализация лу на базе диодной матрицы

- •3.3. Техническая реализация лу на цифровых микросхемах

- •4. Типовые функциональные узлы комбинационных логических устройств

- •4.1. Мультиплексор

- •4.2. Демультиплексор

- •4.3. Шифратор

- •4.4. Дешифратор

- •4.5. Цифровой компаратор

- •4.6. Функция «Исключающее или»

- •4.7. Логические элементы, реализующие сложные функции

- •5. Триггеры

- •5.1. Асинхронный rs-триггер

- •5.2. Синхронный rs-триггер

- •5.3. D-триггер

- •5.4. Т-триггер

- •5.5. Двухступенчатый т-триггер

- •5.6. Двухступенчатый синхронный jk-триггер

- •5.7. Триггер с динамическим управлением

- •6. Счётчики

- •6.1. Двоичный суммирующий счётчик

- •6.2. Двоичный вычитающий счётчик

- •6.3. Двоично-кодированный счётчик

6. Счётчики

Счётчиком называется последовательностное логическое устройство, предназначенное для счёта входных импульсов и фиксации их числа в двоичном коде.

Как было отмечено в главе 5, для реализации схем счётчиков применяют триггеры. Поскольку счётный триггер реализуется либо на двухступенчатом JK-триггере, либо наD-триггере с динамическим управлением, то схемы счётчиков выполняют на этих триггерах.

Счётчики могут выполнять следующие операции:

1) установка в исходное состояние (запись нулевого кода);

2) установка в предварительную позицию (запись кода начала счёта);

3) хранение информации;

4) выдача хранимой информации в параллельном коде;

5) счёт на увеличение (инкремент) – увеличение хранящегося кодового слова на единицу;

6) счёт на уменьшение (декремент) – уменьшение хранящегося кодового слова на единицу.

Основным параметром счётчика является модуль счёта М. Модуль счёта характеризует максимальное число импульсов, после подсчёта которого счётчик устанавливается в исходное состояние. По значению модуля счёта счётчики делятся на:

- двоичные, у которых модуль счёта равен целой степени числа 2 (М = 2n);

- двоично-кодированные, у которых модуль счёта может принимать любое значение, не равное целой степени числа 2.

По направлению счёта счётчики делятся на:

- суммирующие, считающие на увеличение;

- вычитающие, считающие на уменьшение;

- реверсивные, считающие на увеличение или на уменьшение в зависимости от значения управляющего сигнала.

6.1. Двоичный суммирующий счётчик

Рассмотрим двоичный суммирующий счётчик до восьми (М = 8). Для схемы такого счётчика потребуется три триггера (8 = 23, то естьn= 3). Составим таблицу состояний триггеров счётчика (таблица 6.1).

Таблица 6.1

Таблица состояний триггеров двоичного суммирующего счётчика М = 8

|

№ импульса на входе счётчика |

С |

Q0 |

Q1 |

Q2 |

|

1 |

1 |

0 |

0 |

0 |

|

2 |

1 |

1 |

0 |

0 |

|

3 |

1 |

0 |

1 |

0 |

|

4 |

1 |

1 |

1 |

0 |

|

5 |

1 |

0 |

0 |

1 |

|

6 |

1 |

1 |

0 |

1 |

|

7 |

1 |

0 |

1 |

1 |

|

8 |

1 |

1 |

1 |

1 |

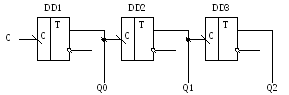

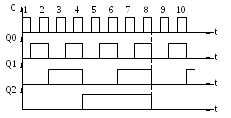

Первый триггер (выход Q0) изменяет своё состояние с приходом каждого импульса на вход С, второй триггер (выходQ1) изменяет своё состояние с приходом каждого второго импульса, третий триггер (выходQ2) изменяет своё состояние с приходом каждого четвёртого импульса. Для реализации такого алгоритма работы следует применить счётный триггер с инверсным динамическим входом. Структурная схема счётчика представлена на рис. 6.1, а временная диаграмма работы – на рис. 6.2.

|

|

Рис. 6.1. Структурная схема двоичного суммирующего счётчика М = 8

|

|

Рис. 6.2. Временная диаграмма работы двоичного суммирующего счётчика М = 8

Счётный триггер с инверсным динамическим входом переключается по срезу импульса синхронизации (переключение от логической 1 к логическому 0). Поэтому при последовательном соединении триггеров, когда вход следующего подключается к прямому выходу предыдущего, получается счёт на увеличение. С выходов Q0,Q1 иQ2 можно считывать информацию о количестве подсчитанных импульсов в параллельном коде (в виде трёхразрядного двоичного числа).

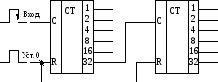

Пример технической реализации двоичного суммирующего счётчика микросхема К176ИЕ1. Это шестиразрядный двоичный счётчик. У него два входа: входR– установка всех шести триггеров в 0 и инверсный динамический вход счёта импульсов С (рис. 6.3). Установка в 0 происходит при подаче уровня логической 1 на входR, переключение триггеров при счёте – по срезу импульсов на входе С. Для увеличения разрядности счётчика микросхемы К176ИЕ1 можно соединять последовательно: вход С следующей микросхемы с выходом «32» предыдущей.

|

|

Рис. 6.3. Принципиальная схема двоичного суммирующего счётчика на микросхемах К176ИЕ1