- •«Теория дискретных устройств автоматики и телемеханики в электроснабжении» курс лекций

- •Введение

- •1. Математическое описание дискретных устройств

- •1.1. Системы счисления

- •1.2. Дискретные сигналы

- •1.3. Логические константы и переменные. Логические операции. Логические элементы

- •1.4. Классификация логических устройств

- •1.5. Способы записи функций алгебры логики

- •1.6. Структурная схема логического устройства

- •1.7. Принцип двойственности

- •1.8. Теоремы алгебры логики

- •2. Минимизация функций алгебры логики

- •2.1. Цель минимизации фал

- •2.2. Способ представления фал с использованием карт Вейча – Карно

- •2.3. Минимизация полностью определённой фал

- •2.4. Минимизация недоопределённой фал

- •2.5. Минимизация системы фал

- •3. Техническая реализация логических устройств на реальной элементной базе

- •3.1. Техническая реализация лу на электромагнитных реле

- •3.2. Техническая реализация лу на базе диодной матрицы

- •3.3. Техническая реализация лу на цифровых микросхемах

- •4. Типовые функциональные узлы комбинационных логических устройств

- •4.1. Мультиплексор

- •4.2. Демультиплексор

- •4.3. Шифратор

- •4.4. Дешифратор

- •4.5. Цифровой компаратор

- •4.6. Функция «Исключающее или»

- •4.7. Логические элементы, реализующие сложные функции

- •5. Триггеры

- •5.1. Асинхронный rs-триггер

- •5.2. Синхронный rs-триггер

- •5.3. D-триггер

- •5.4. Т-триггер

- •5.5. Двухступенчатый т-триггер

- •5.6. Двухступенчатый синхронный jk-триггер

- •5.7. Триггер с динамическим управлением

- •6. Счётчики

- •6.1. Двоичный суммирующий счётчик

- •6.2. Двоичный вычитающий счётчик

- •6.3. Двоично-кодированный счётчик

5.2. Синхронный rs-триггер

Синхронный RS-триггер получается добавлением входной логики к схеме асинхронногоRS-триггера. Чтобы триггер переключался от сигналов управляющих входов только при наличии разрешающего сигнала на входе синхронизации, входная логика должна быть выполнена на элементах И. Рассмотрим таблицу переходов синхронногоRS-триггера с прямыми входамиR,Sи С (таблица 5.2).

Таблица 5.2

Таблица переходов синхронного RS-триггера

|

С |

R |

S |

Qn |

Qn+1 |

|

1 |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

|

1 |

1 |

|

0 |

|

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

0 |

1 |

1 |

|

0 |

0 |

|

1 |

1 |

Примечание: «» сигнал может принимать любое значение 0 или 1

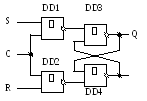

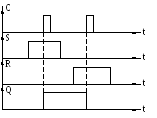

Когда на входе С сигнал активный (логическая 1), триггер переключается по сигналам входов RиS. Когда на входе С логический 0, триггер находится в режиме хранения информации. Следует отметить, что при активном сигнале на входе С на входыRиSнельзя одновременно подавать активные сигналы. Состояние триггера при этом будет непредсказуемо. Схема и временная диаграмма работы синхронногоRS-триггера представлены на рис. 5.4.

|

а |

б |

Рис. 5.4. Схема синхронного RS-триггера на элементах 2И-НЕ (а) и временная диаграмма работы (б)

Условное графическое обозначение синхронного RS-триггера представлено на рис. 5.5. Следует отметить, что синхронныйRS-триггер является основой для построения более сложных триггерных схем. Отдельно синхронныйRS-триггер в составе микросхем не выпускается.

|

|

Рис. 5.5. Условное графическое обозначение синхронного RS-триггера

5.3. D-триггер

Схема D-триггера строится на основе синхронногоRS-триггера. Поскольку на входыRиSRS-триггера нельзя одновременно подавать активные сигналы, то для выполнения этого условия достаточно установить инвертор. Получится информационный входD(вход данных), сигнал с которого (логический 0 или логическая 1) будут перенесены на прямой выход триггера по активному сигналу входа синхронизации. Рассмотрим таблицу переходовD-триггера с прямыми входамиDи С (таблица 5.3).

Таблица 5.3

Таблица переходов D-триггера

|

С |

D |

Qn |

Qn+1 |

|

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

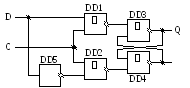

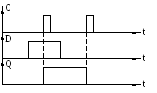

Схема и временная диаграмма работы D-триггера представлены на рис. 5.6.

|

а |

б |

Рис. 5.6. Схема D-триггера на элементах 2И-НЕ (а) и временная диаграмма работы (б)

В составе микросхем ТТЛ и КМОП имеется большое число различных типов D-триггеров, которые отличаются наличием или отсутствием дополнительных асинхронных входовRиS. Например, микросхемы К155ТМ5 и К155ТМ7 не содержат асинхронных входов; микросхемы К155ТМ2 и К561ТМ2 содержат два асинхронных входаRиS, а микросхема К561ТМ1 – только один асинхронный входR. Асинхронные входы имеют приоритет над сигналом информационного входаDи сигналом синхронизации входа С. Условное графическое обозначение различных типовD-триггеров представлено на рис. 5.7.

-

а)

б

)

)

Рис. 5.7. Условное графическое обозначение D-триггера:

а – без асинхронных входов; б – с асинхронными входами R и S

Следует отметить, что некоторые из вышеперечисленных микросхем D-триггеров реагируют на перепад логических уровней входа синхронизации. Принцип работы таких схем будет рассмотрен ниже.

)

) )

)

)

) )

)