- •Методические указания к лабораторной работе

- •Краткие теоретические сведения. Последовательная схема.

- •Асинхронный sr-триггер с инверсными входами.

- •Синхронный sr-триггер с прямыми входами.

- •Jk-триггер.

- •D- и t-триггеры.

- •Далее построить самостоятельно следующие таблицы: sr-триггеры

- •Jk-триггеры

- •D-триггер

- •T-триггер

- •Приложение. Работа в Logic Works.

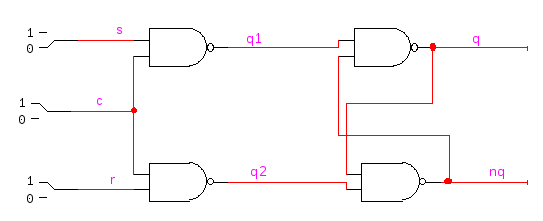

Синхронный sr-триггер с прямыми входами.

Если на С вход (в синхронном триггере) подать 1, то триггер работает также, как асинхронный. Если на С - 0, то состояние триггера ни при каком изменении входа не меняется.

Рис. 3. SR-триггер синхронизируемый по уровню сигнала на элементах И-НЕ

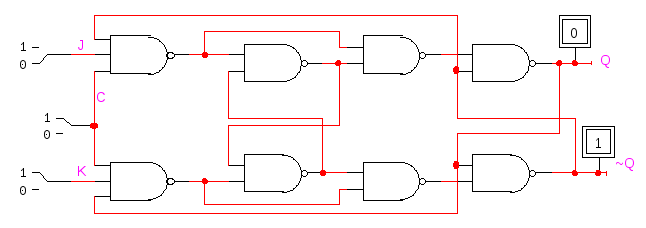

Jk-триггер.

JK-триггер работает на такой же логике, как и SR- триггер. Функции S выполняет J, а функции R выполняет K. Отличие от SR – возможность подать на его входы две единицы. В этом случае триггер перебросится в противоположное состояние. На основе JK-триггера можно построить любой триггер, следовательно он является универсальным.

Рис.4. Схема JK –триггера на элементах И-НЕ.

В приведенной на рис.4 схеме JK-триггера вход C –инверсный, то есть триггер срабатывает при низком уровне сигнала ("0") на входе С.

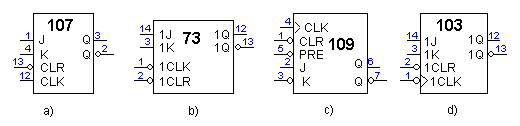

На рис.5 представлены некоторые библиотечные элементы JK-триггеров, соответствующие импортным микросхемам JK-триггеров серии 7400, отличающиеся входом для синхроимпульсов. Эти элементы применяются при моделировании работы конкретной электрической схемы, собранной на реальных микросхемах серии 7400. Триггер на рис. 5а управляется высоким уровнем сигнала на входе CLK (Clock) для синхроимпульса (то есть переход осуществляется при высоком уровне сигнала), а триггер на рис. 5б – низким. Триггер на рис.5с срабатывает при переходе сигнала на входе CLK с низкого уровня на высокий (то есть по переднему фронту положительного импульса), а триггер на рис. 5d срабатывает при переходе сигнала на входе CLK с высокого уровня на низкий (то есть по заднему фронту положительного импульса). Триггеры, управляющиеся по фронту синхроимпульса имеют маленький треугольник на входе СLK на изображении элемента. Для удобства использования в схемах элементы могут иметь дополнительные входы, например, инверсный вход CLR служит для установки начального состояния триггера равным "0" (то есть очистить- CLEAR) при подаче на этот вход "0". Затем следует подать на этот вход "1", и тогда, в дальнейшем, он не будет влиять на логику работы триггера, задаваемую последовательностью сигналов на входе.

Рис.5. Микросхемы JK-триггеров из библиотеки 7400 Flip-Flops.clf.

Если нас интересует только логика работы схемы, то можно применять обобщенные стандартные элементы триггеров из библиотеки Simulation Logic.clf без привязки к конкретным микросхемам (рис.6). Эти элементы также имеют вспомогательные входы для установки начальных значений (вход S-Set устанавливает триггер в "1", а вход R-Reset сбрасывает триггер в "0").

Рис.6. Стандартные элементы JK, D и T-триггеров и их обозначение в Logic Works.

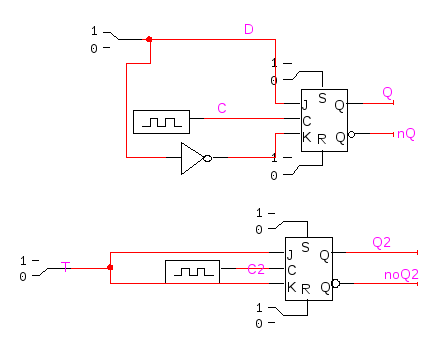

D- и t-триггеры.

D-триггер (рис.6)- простейший элемент памяти . На его выходе тот же сигнал, но с задержкой по времени на такт. Чтобы JK превратить в D-триггер, нужно J вход через инвертор подать на K.

Т-триггер(рис.6) - счетный триггер. Имеет один вход. При подаче на него 1, срабатывает, меняя свое состояние на противоположное. При подаче 0 не меняет состояние. Чтобы JK превратить в T-триггер, нужно J и K закоротить и превратить в один вход.

Рис.6. Схема D и T –триггеров, построенных с помощью JK –триггера.