Московский Институт Электронной Техники

(Технический Университет)

Кафедра

ПРОЕКТИРОВАНИЕ И КОНСТРУИРОВАНИЕ

ИНТЕГРАЛЬНЫХ МИКРОСХЕМ

Курсовая работа

по дисциплине:

«АВТОМАТИЗАЦИЯ

ФУНКЦИОНАЛЬНО-ЛОГИЧЕCКОГО

ПРОЕКТИРОВАНИЯ»

на тему:

«D триггер»

Выполнил: Кононов А.В.

Группа: ЭКТ-42

Преподаватель: Ермак В.В.

Москва, 2004 г.

Триггер D-типа.

Триггером D-типа, известным в литературе под названием «триггер задержки», называют логическое устройство с двумя устойчивыми состояниями и одним информационным входом D. Закон функционирования триггера D-типа приведён в таблице и описывается логическим уравнением:

Qn+1=Dn

|

t n |

tn+1 |

|

Dn |

Dn+1 |

|

0 |

0 |

|

1 |

1 |

Логическое уравнение показывает, что состояние D-триггере в момент времени tn+1 совпадает с кодом входного сигнала, действующего в момент времени tn, т.е. осуществляется «задержка» входного сигнала.

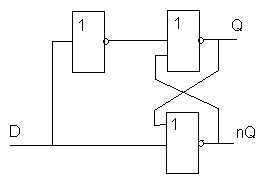

Простейшим видом тактового триггера является асинхронный D-триггер рис.

Однако его схема не имеет практического применения, так как функцию D-триггера выполняет схема, состоящая из двух последовательно включённых инверторов. Наибольший интерес представляют тактируемые триггеры, нашедшие широкое распространение в интегральных схемах.

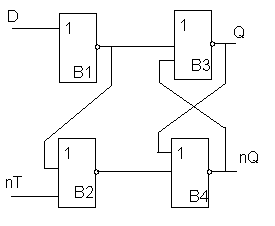

Варианты реализации однотактных триггеров D-типа, управляемых уровнем тактового импульса, выполняемые на элементах И-НЕ, ИЛИ-НЕ. Здесь вход D является информационным, а вход Т – тактовым. Схема рис. 1 тактируется сигналом логической 1, а схема на рис. 2 – сигналом логического 0.

Рис. 1

Рис. 2

В отсутствие тактового импульса вентили B1 и В2 закрыты и независимо от информации на входе D состояние триггера не изменяется.

При Т=1 и D=1 (рис. 1) на выходе вентиля В1 формируется уровень логического 0. Последний, поступая на входы вентилей В3 и В2, осуществляет установку триггера в состояние Q=1 и одновременно блокирует включение вентиля В2.

Схема 1

Рассмотрим подробнее схему номер 1

Таблица истинности:

С D Qn+1

0 0 Qn

0 1 Qn

1 0 0

1 1 1

С

D

Q

Qn

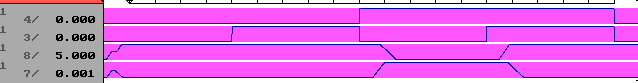

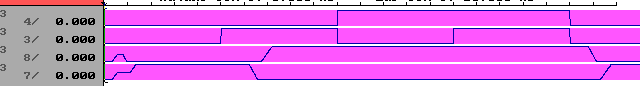

Функциональная верификация:

Схема тактируется сигналом логической 1.

При С=1 и D=1 на выходе вентиля В1 формируется уровень логического 0. Последний, поступая на входы вентилей В3 и В2, осуществляет установку триггера в состояние Q=1 и одновременно блокирует включение вентиля В2.

С

D

Q

Qn

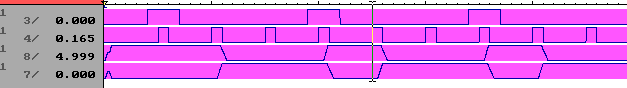

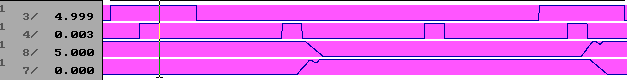

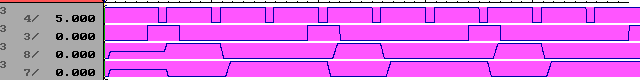

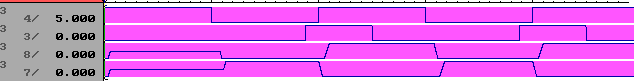

Временная верификация:

При уменьшении продолжительности синхроимпульса до величины равной 7 нс на выходах триггера начинают появляется отклонения от нормальной работы триггера при переключении из 0 в 1, это связано с тем один из сигналов проходит большее количество элементов и появляется на выходе «состязание».

7 ns величина синхроимпульса

D

С

Q

Qn

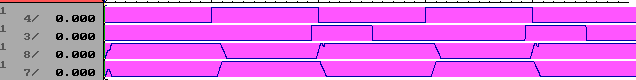

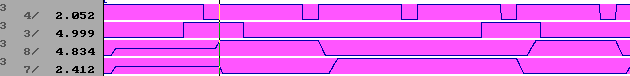

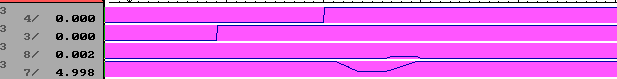

Если же сигнал уменьшить до величины равной 6 нс то триггер полностью перестает работать здесь большую роль играет управляющая ячейка (УЯ стоящая из триггеров В1 и В2), она не позволяет запоминающей ячейке (ЗЯ стоящая из триггеров В3 и В4) установится в стационарное положения.

6 ns величина синхроимпульса

D

С

Q

Qn

Поведение триггера при дестабилизирующих факторах:

Схема 1

Информационный вход (3) на правой границе синхроимпульса (4), Q (8), nQ(7).

Рис 7 ns(Информационный и синхроимпульс в еденице)

Рис 6 ns(Информационный и синхроимпульс в еденице)

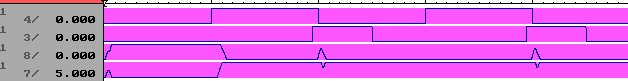

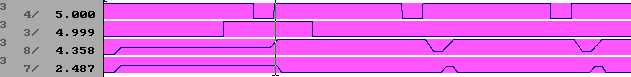

Информационный вход (3) на левой границе синхроимпульса (4), Q (8), nQ(7)

Рис 7 ns(Информационный и синхроимпульс в еденице)

Рис 6 ns(Информационный и синхроимпульс в еденице)

С хема

2

хема

2

Таблица истинности:

С D Qn+1

0 0 0

0 1 1

1 0 Qn

1 1 Qn

Функциональная верификация:

Временная верификация:

8ns величина инверсного синхроимпульса

7ns величина инверсного синхроимпульса

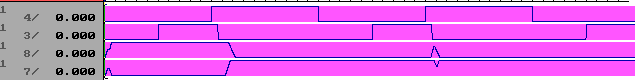

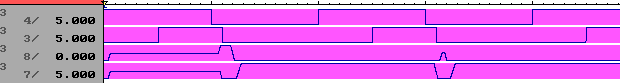

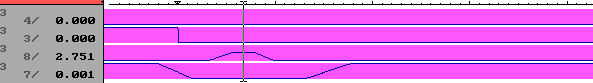

Поведение триггера при дестабилизирующих факторах:

Схема 2

Информационный вход (3) на правой границе синхроимпульса (4), Q (8), nQ(7).

Рис 12 ns(Информационный в единице, а синхроимпульс в нуле)

Рис 11 ns(Информационный в единице, а синхроимпульс в нуле)

Информационный вход (3) на левой границе синхроимпульса (4), Q (8), nQ(7)

Рис 12 ns(Информационный в единице, а синхроимпульс в нуле)

Рис 11ns (Информационный в единице, а синхроимпульс в нуле)

Список использованных материалов

-

Букреев И.Н и др. Микроэлектронные схемы цифровых устройств – 3-е издание, переработанное и дополненное - М: «Радио и связь», 1990г.

-

Букреев И.Н., Мансуров Б.М., Горячев В.И. Микроэлектронные схемы цифровых устройств – 2-е издание, переработанное и дополненное - М: «Советское радио», 1975г.

-

Конспект лекций.

-

Программа PLogCad.