Московский Институт Электронной Техники

Кафедра ПКИМС

Курсовая работа на тему:

“Проектирование вычитателя”

по курсу

“Автоматизация функционально-логического проектирования”

Выполнил:

Студент гр. ЭКТ-43

Сидорин В.А

Проверил:

Попова Т.В.

Москва 2000г.

- 2 -

Содержание:

Задание……………………………………………….3

Теоретическая часть…………………………………3

Анализ работы схемы……………………………….5

Логическая схема вычитателя………………………6

Диаграммы…………………………………………...7

Литература……………………………………………8

- 3 -

Задание:

-

Построить логическую схему полусумматора

-

Построить логическую схему сумматора

-

Произвести анализ работы вычитателя. Определить пределы изменения уменьшаемого и вычитаемого.

Теоретическая часть.

Операция вычитания не является основной в цифровых устройствах обработки информации и выполняется как сложение уменьшаемого с вычитаемым, представленным в дополнительном коде. Поэтому для синтеза вычитателей часто используют полные одноразрадные сумматоры.

Сумматор – логический операционный узел ЭВМ, выполняющий арифметическое сложение кодов двух чисел.

Сумматоры можно классифицировать:

по количеству одновременно обрабатываемых разрядов чисел:

одноразрядные

многоразрядные

по чилсу входов-выходов:

четвертьсумматоры

полусумматоры

полные одноразрядные двоичные сумматоры

по способу представления и обработки данных:

последовательные

параллельные

по способу организации переноса:

последовательный перенос

параллельный перенос

групповая структура

специальная организация цепей переноса

по способу выполнения операции сложения и возможности сохранения результата сложения:

комбинационный

накапливающий

В данной курсовой работе был проведен анализ работы четырехразрядного вычитателя, построенного на основе полных сумматоров.

Полусумматор – имеет два входа a и b для двух слагаемых и два выхода: S – сумма, P – перенос.

- 4 -

Таблица истинности полусумматора:

a b S P

0 0 0 0

0 1 1 0

1 0 1 0

1 1 1 1

Его логическая схема:

Полный двоичный сумматор – имеет три входа: a,b – для двух слагаемых и p – перенос из предыдущего разряда и два выхода: S – сумма и P – перенос.

Таблица истинности:

a b p P S

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 0 1 0

1 1 1 1 1

Логическая схема:

- 5 -

Анализ работы вычитателя:

Для данного вычитателя используется прием вычитания с помощью циклического переноса:

Примем, что A={a3 a2 a1 a0} – уменьшаемое, а

B={b3 b2 b1 b0} – вычитаемое.

Проведя анализ работы вычитателя, можно заметить, что он корректно работает, только в том случае, когда A>B. В случае, если A=B на выходах вычитателя получается S={1 1 1 1} в не зависимости от входов.

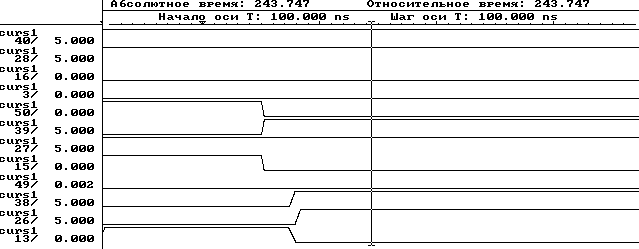

После временного анализа можно установить, что минимальный период, с которым может работать схема, равен – Tmin=54нс.

То есть частота работы схемы 19Мгц.

Задержки переключений:

из 0 - > 1 из 1 - > 0 tср

для 0 разр. 47.5нс 47.3нс 47.4нс

для 1 разр. 42.6нс 43.3нс 42.9нс

для 2 разр. 33.8нс 34.3нс 34.1нс

для 3 разр. 25.1нс 25.4нс 25.3нс

- 6 -

Логическая схема анализируемого вычитателя (сумматоры заменены на их схемные символы) :

- 7 -

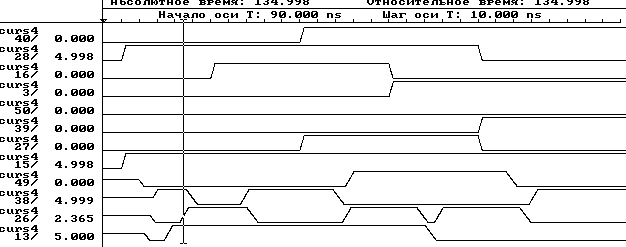

Диаграммы:

Функциональная верификация:

Временная верификация:

Временная верификация проводилась по нулевому разряду вычитаемого, так как у этого сигнала наиболее далекий путь до выхода.

- 8 -

Анализ диаграмм на “риски сбоев”:

Изучив первую диаграмму можно увидеть, что между переключениями схемы:

A={ 1 1 1 0 } -> A={ 1 1 0 1 } при B={ 0 0 1 1 },

получаем S={ 1 0 1 1 } -> S={ 1 0 1 0 }, и в первом разряде суммы возникает “риск сбоя”.

Литература:

-

Н.В. Воробьев “Сумматоры”, Москва, МИЭТ 1993г.

-

А.Г. Алексенко, И.И. Шагурин, “Микросхемотехника”, Москва, Радио и связь 1990г.