МИЭТ (ТУ)

Курсовой проект

по курсу АИС

на тему

"Четырёх канальный распределитель импульсов с перекрестной связью”

Выполнил: ФилипповМ.К

ЭКТ-45

Проверил: Шишина Л.Ю.

Москва 2001

Задание.

Спроектировать схему четырёх канального распределителя импульсов с перекрестной связью на RS-триггерах в ИЛИ-НЕ логическом базисе, выполненную по КМОП технологии. Результатом проектирования является схема, выполняющая заданную логическую функцию для указанной рабочей частоты при минимальной из заданных значений нагрузочной емкости.

Внешние условия функционирования:

а) напряжение источника питания UИП = 5В;

б) нагрузочная емкость CН = 0.5 пФ;

Рабочие параметры схемы, условия работоспособности:

а) рабочая частота 20 Мг;

б) длительность и симметрия фронтов выходного сигнала tФ01 = tСР10 =1 нс.

Технологические и топологические ограничения:

а) пороговое напряжение n- и p-МДПТ UПОРn = 0.8 В, UПОРp = -1,2 В;

б) электрофизические параметры технологической МДП структуры для расчета крутизны транзисторов и паразитных емкостей и сопротивлений:

-

подвижность носителей: n= 360 см2/В*с; p = 165 см2/В*с;

-

концентрация носителей NA = 1015 см –3; ND = см-3;

-

толщина слоя подзатворного диэлектрика dOX = 20 нм.

в) топологические ограничения:

-

минимальный тополографический размер = 1 мкм.

Получить:

-

Структурную схему четырёх канального распределителя импульсов с перекрестной связью на RS триггерах.

-

Размеры всех транзисторов W, L на основании предварительного расчета по заданным параметрам tф, fT.

-

Расчет статических и динамических характеристик устройства при помощи программы “SPICE” с возможной коррекцией параметров W, L ряда транзисторов для обеспечения заданных условий работоспособности.

-

Получить и оценить:

-

получить зависимость времени задержки сигнала от величины нагрузочной емкости;

-

оценить предельную рабочую частоту для заданных топологических норм.

-

Оценить потребляемую мощность.

-

Разработать эскиз топологии полученной схемы и заданного триггера.

-

Проверить с помощью программы ASKT правильность работы схемы.

Теоретические сведения.

Триггеры RS-типа.

Триггером RS-типа называют логическое устройство с двумя устойчивыми состояниями, имеющие два информационных входа R и S, такие что при S =1 и R=0 триггер принимает состояние 1 (Q=1), а при R=1 и S=0 триггер принимает состояние 0 (Q=0).

Закон функционирования триггера RS-типа отображен в табл.1

|

tn |

tn+1 |

|

tn |

tn+1 |

||||

|

Qn |

Rn |

Sn |

Qn+1 |

|

Qn |

Rn |

Sn |

Qn+1 |

|

0 0 0 0 |

0 0 1 1 |

0 1 0 1 |

0 1 0 X |

|

1 1 1 1 |

0 0 1 1 |

0 1 0 1 |

1 1 0 X |

При одновременном поступлениина входы R и S логических 1 триггер принимает неопределенное состояние. Поэтому логические устройства на основе RS триггеров должны строится с учетом исключения комбинаций сигналов R*S = 1. Логическое уравнение RS триггера, составленное в соответствии с его таблицей переходов и с учетом оговоренного выше ограничения, записывается в виде

_

Qn+1 = S n +Rn *Qn; Rn * Sn = 0 (1)

Многотактные тригерные устройства, как правило, выполняются на основе тактируемых триггеров RS типа по схеме “M-S”. Основной (Master) принимает входную информацию, а вспомогательный триггер (Slave) фиксирует состояние тригерного устройства.

Распределителя импульсов с перекрестной связью

Счетчики на сдвигающих регистрах с перекрестными связями позволяют создавать устройства с 2N устойчивыми состояниями (N—разрядность регистра). Задача построения распределителя на их основе сводится к созданию схемы дешифрации состояний. В зависимости от способа сдвига информации в регистре различают распределители многократного и однократного действия. Последние выполняются на D, R-S, J-K триггерах и находят наибольшее применение.

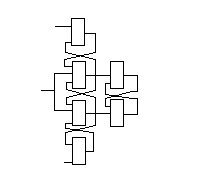

На рис.1 приведена схема четырёх канального распределителя импульсов с перекрестной связью, выполненная на двух R-S триггерах .

Рис.1.

схема четырёх канального распределителя

импульсов с перекрестной связью

Рис.1.

схема четырёх канального распределителя

импульсов с перекрестной связью

Анализ и расчет

В данной работе схема четырёх канального распределителя импульсов с перекрестной связью была реализован в ИЛИ-НЕ логическом базисе по схеме предложенной на рис. 1Схема триггера, используемого в данном счетчике, представлена на рис. 2

рис.2

Все устройства в этой работе были выполнены на элементах 2ИЛИ-НЕ, 3ИЛИ-НЕ, 4ИЛИ-НЕ и инвертор.

Быстродействие данной схемы заданно тактовой частотой fT=20МГц. Максимальное число элементов, которое входной сигнал проходит до выхода равно восьми.

Воспользуемся выражениями для приближенной оценки задержки переключения:

tЗД01 = (CH UИП)/(K0N Wn/Ln (UИП - UПОРn)2)

tЗД10 = (СH UИП)/(K0P WP/Ln(UИП - UПОРp)2)

откуда

Wn/Ln = (CH UИП)/(K0N tЗД01 (UИП - UПОРn)2)

Wp/Lp = (CH UИП)/(K0p tЗД10 (UИП - UПОРp)2) (3)

Определим K0n = nCod/2, где

Сod = d0/dox = (3*10-13 Ф/см)/(20*10-7 см) = 1,5*10-7 Ф/см2

K0n = (360 см2/В с * 1.5*10-7 Ф/см2)/2 = 28 мкФ/В с

Аналогично для p-типа

K0p = pCod/2,

K0p = (165 см2/В с * 1.5*10-7 Ф/см2)/2 = 12 мкФ/В с.

Wp/Lp = (0.5*1-12 Ф * 5 В )/(28*10-6 Ф/В с (5 В – 0.8 В)2 * 2 * 10-9 с) = 15

Wn/Ln = (0.1*1-12 Ф * 5 В )/(12*10-6 Ф/В с (5 В + 1,2 В)2 * 2 * 10-9 с) = 5

Берем длины всех транзисторов минимальными, т.е 2 мкм. Отсюда Wn= 10мкм, а WP = 30 мкм.

С помощью программы “PSPICE” в данной работе были уравнены tФ и tСР схемы. Это было достигнуто выравниванием крутизны n- и p-канального эквивалентного транзистора Kn=Kp.

Таким образом удалось достичь (рис.):

tФ01 = 1 нс; tСР10 =1 нс.

С помощью средств программы “PSPICE” из графиков (рис. ) были найдены:

tЗД01 = 0.5 нс; tЗД10 =0.5нс;

Определим

tЗД = (tЗД01 + tЗД10)/2 = 0.5нс.

fT < 1/3 * tЗД = 6.7 МГц.

Таким образом при данных размерах транзисторов и величине нагрузочной емкости (CH = 0,5 пФ) схема работает нормально. Путем повышения номинала нагрузочной емкости была найдена такая нагрузочная емкость, при которой схема перестает переключаться. Она составила CH = 18.7 пФ. Для этой емкости были найдены:

tФ01 = 38нс; tСР10 =45нс.

Из графиков рис. были найдены:

tЗД01 = 0.848нс; tЗД10 =0.595 нс;

откуда

tЗД = (tЗД01 + tЗД10)/2 = 0.721нс.

На рис. показана зависимость времени задержки переключения выходного сигнала от величины емкости нагрузки.

Рис. Зависимость времени задержки от нагрузочной емкости.

Расчет потребляемой мощности.

Статическая мощность в КМДП схемах не потребляется, а динамическая рассчитывается для максимально допустимой величины CH:

PДИН = fт СH МАК UИП2 = 3.1 мВт.

Проектирование эскиза топологии.

Топология счетчика показана на рис.

Общая площадь схемы составила S =1375мкм * 1250мкм = 1718750мкм2.

Оценку величины паразитной емкости между проводящими слоями можно сделать, пологая минимальную толщину межслойной изоляции (SiO2) dox = 0.5 мкм и зная площадь самой длинной шины в схеме:

Cпар = d0/dox *S = (3*10-13 Ф/см)/(0.5*10-6 см) *0.0007121= 4.6пФ/см2

R=p*n=0.07*791=55.37 Om

T=R*C=26*е-09

Проектирование в ASKT.

Схема счетчика была собрана в программе ASKT. Результаты этого моделирования показаны на рис.

Вывод.

В данной работе были получены следующие результаты:

-

при минимальной нагрузочной емкости (СH=0.5 пФ):

tФ01 = 0.5нс; tСР10 =0.5 нс

tЗД = 0.5 нс.

fT < 6.7 МГц.

-

при максимальной нагрузочной емкости (СН=18.7пФ):

tФ01 = 0.848 нс; tСР10 =0.595нс.

tЗД = 0.721нс.

Для обеспечения равенства tФ = tСР =1нс были подобраны размеры транзисторов:

- nМДПТ l=2u w=20u

-

pМДПТ l=2u w=60u

Приведена зависимость времени задержки схемы от величины нагрузочной емкости.

Рассчитана динамическая потребляемая емкость между проводящими слоями: СПАР=.4.6 мпФ/см2

Рассчитана динамическая потребляемая мощность PДИН = 3.1 мВт

Общая емкость схемы S = 1718750 мкм2.

Схема триггера была смоделирована в программе PSPICE, где были получены все расчетные данные. А также схема счетчика была смоделирована в программе ASKT, где была проверена логика работы схемы.

Список используемой литературы.

-

Л.Ю.Шишина “Методические указания по курсовому проектированию по курсу “элементарная база цифровых ИС” МИЭТ, 1994.

-

Н.В.Воробьев “Счетчики и пересчетные устройства” МИЭТ, 1992

-

И.Н.Букреев “Микроэлектронные схемы цифровых устройств” “Советское радио”, 1975.

-

Конспект лекций по курсу “Микросхемотехника ЦИС” 2001.

-

В.И.Старосельский “Физика МДП транзисторов” Москва, 1992.