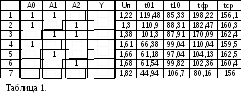

Лабораторная работа №4.

Тестируемая схема 3И-НЕ:

С пособы

переключения схемы занесены в таблицу

1.

пособы

переключения схемы занесены в таблицу

1.

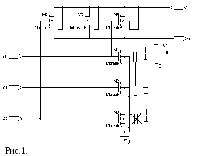

Д ля

объяснения разницы задержек и фронтов

возьмем два каких-нибудь переключения

и покажем, чем отличается их принцип

работы. Сравнивать будем для первого и

третьего случаев, поскольку они идентичны

по переключению. В идеале их задержки

и фронты должны быть одинаковыми. Но

реально происходит следующее: в открыто

состоянии у транзистора имеется какое-то

сопротивление канала и какая-то выходная

емкость (рис.1.). Поскольку для первых 3х

случаев емкость p-канального

транзистора заряжается и разряжается

одинаково, то влияние ее можно учесть

в общей емкости. Теперь для первого

состояния, пока на входе А2 держится 0,

транзистор М4 открыт, а значит нагрузочная

емкость заряжена до Еп, транзисторы М1

и М2 открыты, и их емкости заряжены также

до Еп, транзистор М3 закрыт, но его емкость

исходя из представления на рисунке тоже

заряжена до Еп. Теперь переключаем вход

А2 из 0 в 1. При это увеличивается

сопротивление канала p-канального

транзистора, а транзистор М3 наоборот

открывается. Все емкости начинают

разряжаться до 0. Этот процесс происходит

относительно быстро, а поскольку основной

вклад здесь вносит нагрузочная емкость,

при каждого в отдельности входа из 0 в

1 задержка и фронт остаются примерно

постоянными.. Совсем друге дело, когда

напряжение меняется потом от 1 до 0.

Транзистор М4 открывается, а М2 опять

закрывается. Тогда для окончания

переходного процесса нужно зарядить

все емкости в цепочке (см. рисунок), а на

это уходит самое большое время, поскольку

данная цепочка имеет при переключении

одного входа самое большое число

емкостей.

ля

объяснения разницы задержек и фронтов

возьмем два каких-нибудь переключения

и покажем, чем отличается их принцип

работы. Сравнивать будем для первого и

третьего случаев, поскольку они идентичны

по переключению. В идеале их задержки

и фронты должны быть одинаковыми. Но

реально происходит следующее: в открыто

состоянии у транзистора имеется какое-то

сопротивление канала и какая-то выходная

емкость (рис.1.). Поскольку для первых 3х

случаев емкость p-канального

транзистора заряжается и разряжается

одинаково, то влияние ее можно учесть

в общей емкости. Теперь для первого

состояния, пока на входе А2 держится 0,

транзистор М4 открыт, а значит нагрузочная

емкость заряжена до Еп, транзисторы М1

и М2 открыты, и их емкости заряжены также

до Еп, транзистор М3 закрыт, но его емкость

исходя из представления на рисунке тоже

заряжена до Еп. Теперь переключаем вход

А2 из 0 в 1. При это увеличивается

сопротивление канала p-канального

транзистора, а транзистор М3 наоборот

открывается. Все емкости начинают

разряжаться до 0. Этот процесс происходит

относительно быстро, а поскольку основной

вклад здесь вносит нагрузочная емкость,

при каждого в отдельности входа из 0 в

1 задержка и фронт остаются примерно

постоянными.. Совсем друге дело, когда

напряжение меняется потом от 1 до 0.

Транзистор М4 открывается, а М2 опять

закрывается. Тогда для окончания

переходного процесса нужно зарядить

все емкости в цепочке (см. рисунок), а на

это уходит самое большое время, поскольку

данная цепочка имеет при переключении

одного входа самое большое число

емкостей.

Для случая 3 рассмотрим рисунок 2.

Здесь при подаче на вход сначала 1 разряжается емкость транзистора М1 и нагрузочная. Когда же подается сигнал из 1 в 0, М1 закрывается и время переключения затрачивается только на зарядку нагрузочной емкости и емкости транзистора М1. Соответственно времени затачивается меньше, что и подтверждается теорией.

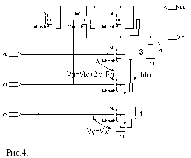

Оценим теперь статические характеристики, а именно характер изменения порогового напряжения.

З десь

существенную роль играет сопротивление

каналов открытых и закрытых транзисторов,

и соответственно падение напряжения

на них (рис .4.). Рассмотрим первый случай.

Для него транзисторы М1 и М2 открыты

(p-канальные транзисторы

опять же не рассматриваем в силу их

аналогичности переключения для первых

трех случаев), следовательно, они имеют

маленькое сопротивление канала.

Транзистор начинает открываться. Когда

значение Vgs=Vg-0=Vg

достигает порогового напряжения

n-канального транзистора,

он откроется и через него начнет протекать

ток. При этом сопротивление канала

p-канального транзистора

увеличивается, и ток через него перестает

протекать. В системе установится

логический ноль. В третьем случае

ситуация почти такая же. Только транзистор

М1 откроется при значении

Vgs=Vg-VdM2=Vg-(IdпRM2+IdпRM3)=Vg-2IdпRn=Vto,

где Rn – сопротивление

канала открытого n-канального

транзистора. Тогда значение Vg=Vto+2IdпRn,

а поскольку в транзисторе в закрытом

состоянии текут подпороговые токи, то

величина 2IdRn

больше нуля. Соответственно для открытия

транзистора надо подать большее

напряжение на затвор (вход), а следовательно

порог сместится вверх. Это подтверждается

измеренными значениями в таблице.

десь

существенную роль играет сопротивление

каналов открытых и закрытых транзисторов,

и соответственно падение напряжения

на них (рис .4.). Рассмотрим первый случай.

Для него транзисторы М1 и М2 открыты

(p-канальные транзисторы

опять же не рассматриваем в силу их

аналогичности переключения для первых

трех случаев), следовательно, они имеют

маленькое сопротивление канала.

Транзистор начинает открываться. Когда

значение Vgs=Vg-0=Vg

достигает порогового напряжения

n-канального транзистора,

он откроется и через него начнет протекать

ток. При этом сопротивление канала

p-канального транзистора

увеличивается, и ток через него перестает

протекать. В системе установится

логический ноль. В третьем случае

ситуация почти такая же. Только транзистор

М1 откроется при значении

Vgs=Vg-VdM2=Vg-(IdпRM2+IdпRM3)=Vg-2IdпRn=Vto,

где Rn – сопротивление

канала открытого n-канального

транзистора. Тогда значение Vg=Vto+2IdпRn,

а поскольку в транзисторе в закрытом

состоянии текут подпороговые токи, то

величина 2IdRn

больше нуля. Соответственно для открытия

транзистора надо подать большее

напряжение на затвор (вход), а следовательно

порог сместится вверх. Это подтверждается

измеренными значениями в таблице.