- •Архитектура цп 80286: основные регистры, режимы работы, адресация памяти

- •Режимы работы

- •Формирование линейного адреса без участия селекторов

- •Формирование линейного адреса в защищенном режиме

- •Вопросы

- •Структура микропроцессоров ia-32

- •Регистры

- •Формат команды микропроцессора ia-32

- •Вопросы для самоконтроля

- •Защищенный режим (Protected Mode)

- •Вопросы для самоконтроля

- •Конвейеризация команд

- •Динамическое (спекулятивное) исполнение

- •Вопросы для самоконтроля

- •Организация и режимы работы процессоров семейства Pentium

- •Динамическое исполнение программ в процессоре Pentium Pro

- •Simd-расширения архитектуры ia-32

- •Микроархитектура NetBurst

- •Архитектурные особенности процессоров семейства Pentium

- •Инициализация пэвм на базе i86-х

- •Вопросы для самоконтоля

|

Анализ развития процессоров фирмы Intel IA-32 В табл. 2.1приведены основные свойства процессоров фирмы Intel, от процессора 8086 до первых представителей семейства Pentium.

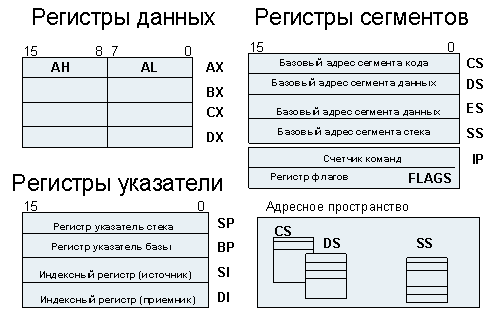

Архитектура ЦП 8086: основные регистры, организация памяти Программная модель МП представляется набором его регистров.Регистрявляется устройством временного хранения данных и используется с целью облегчения арифметических, логических и пересылочных операций. Центральный процессор 8086 имеет четыре 16-битных регистраобщего назначения AX, BX, CX, DX, четыре регистра-указателя SI, DI, BP и SP, четыререгистрасегментовCS, DS, ES, SS, один 16-битовыйрегистрфлагов FLAGS и указатель программ IP (см.рис.2.1)

Регистр-аккумулятор AX используется для хранения промежуточных данных и результатов. При базовых типах адресации регистрBX содержит адрес области памяти либо адрес, который суммируется для получения нового значения со смещением. Регистр-счетчик CX предназначен для управления числом итераций в цикле или числом повторений в командах REP в строковых операциях. Регистрданных DX используется как вторичный аккумулятор для хранения промежуточных данных и результатов. Индексный регистр-источник SI применяется в качестве указателя адреса байта или слова в таких строковых командах, как LODS ("загрузить строку"), CMPS ("сравнить строку"), MOVS ("переслать строку"). При базово-индексной адресации содержимое регистраSI может суммироваться с содержимымрегистраBX. Индексный регистр-источник DI используется как указатель назначения для адреса байта или слова в строковых командах, таких как SCAS (сканировать строку), CMPS, MOVS, STOS (записать строку). При базово-индексной адресации для получения адреса операнда содержимое регистраDI может суммироваться с содержимымрегистраBX. Регистр-указатель стека SP применяется для работы с данными в стековых структурах. Его содержимое указывает адрес элемента на вершине стека, что удобно при организации обработки прерываний, процедур вызова подпрограммы и выхода из нее путем сохранения адреса возврата на вершине стека. Регистр-указатель базы BP используется как дополнительный указатель для работы с данными в стековых структурах. В режиме базово-индексной адресации содержимое регистраBP может суммироваться с содержимымрегистровSI или DI. Адресное пространство памяти процессора, откуда происходит выборка команд и данных, разделено на сегменты(области памяти) емкостью до 64 Кбайт каждый. Процессор 8086 имеет прямой доступ одновременно к четыремсегментам. Начальный адрес сегментаможет быть установлен прикладной программой и всегда должен начинаться с 16-байтовых границ. Базовый адрессегментаполучается делением действительного физического адреса начальной ячейкисегментана 16. Базовые адреса содержатся в одном из четырех 16-битных сегментныхрегистровCS, DS, ES и SS. На расположениесегментане накладывается никаких специальных ограничений, кроме одного: он должен быть на границе 16 байт (т.е. физический адрес начальной ячейки должен делиться на 16).Сегментымогут быть смежными, разделенными, перекрываться частично или полностью. Регистрысегментовиспользуются для идентификации текущегосегментаадресного пространства. Регистрсегмента команд CS указывает сегмент, содержащий адрес текущей выполняемой программы. Регистрсегментаданных DS содержит начало зоны адресов, которая в общем случае включает программно изменяемые таблицы и константы. РегистрдополнительногосегментаES указывает начало области памяти, которая обычно используется для запоминания промежуточных данных. Регистрсегментастека SS содержит начальный адрес стековой структуры в памяти ЭВМ. Указатель команд IP содержит адрес следующей команды в сегменте памяти, определяемом содержимым регистрасегментакоманд CS. Регистрфлагов FLAGS содержит информацию о текущем состоянии микропроцессора. Имеет шесть однобитовых флагов состояния, которые индицируют результаты выполнения арифметических и логических операций. | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Архитектура цп 80286: основные регистры, режимы работы, адресация памяти

Программная модель процессора 80286 включает 14 регистровЦП 8086, пять новыхрегистров:

GDTR - 40-разрядный регистр определяет размер и положение глобальной дескрипторной таблицы;

LDTR - 16-разрядный регистр определяет базовый адрес локальной дескрипторной таблицы;

IDTR - 40-разрядный регистр определяет начало и размер таблицы векторов прерываний;

MSW - слово состояния программы (, если флаг PE = 1 в MSW, то процессор переключается в защищенный режим).;

TR - 16-разрядный регистр содержит селектор сегмента состояния задачи, используется для многозадачности,

и шесть программно недоступных регистров, связанных с CS, DS, ES, SS, GDTR, IDTR.

Режимы работы

С появлением Inte-l286 впервые стали говорить о различных режимах работы IA-32. Это первый представитель данного семейства микропроцессоров, в котором были реализованы многозадачность и защищенная архитектура. Чтобы обеспечить совместимость с предыдущими представителями этого семейства (8086/88, 80186/188), в Inte-l286 было реализовано два режима функционирования: режим реального адреса(режим эмуляции 8086) изащищенный режим, в котором используются все возможности МП. В последующих поколениях МП этого семействазащищенный режимстановится основным режимом работы.

Формирование линейного адреса без участия селекторов

В режиме реального адресаиспользуется упрощенная схема формирования линейного адреса.

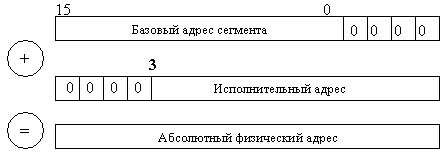

В этом случае базовый адрес сегментаберется из сегментногорегистра. Значение в сегментномрегистрепредставляет собой биты 4-19 базового адресасегмента. Из этого следует, чтосегментыв этих режимах выровнены по 16-байтной границе и всесегментыначинаются в пределах нижнего мегабайта линейного адресного пространства. Действительный физический адрес получается умножением на 16 базового адресасегмента(рис. 2.2). Предел для всехсегментоводинаков. Врежиме реального адресапределсегмента- 64 Кбайт.

Рис.

2.2.Формирование физического адреса

в реальном режиме

Рис.

2.2.Формирование физического адреса

в реальном режиме

Формирование линейного адреса в защищенном режиме

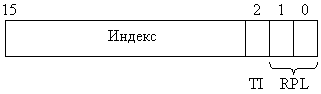

Значения, помещаемые в сегментные регистры, называютсяселекторами.Селекторсодержит индексдескриптора, определяющий номер записи вдескрипторной таблице, бит TI, указывающий, к какойдескрипторной таблицепроизводится обращение LDT (TI = 1) или GDT (TI = 0), а также запрашиваемые права доступа ксегменту- RPL (рис. 2.3.).

Рис.

2.3.Структура селектора

Рис.

2.3.Структура селектора

По указанному в селектореномеру записи в соответствующей (бит TIселектора)дескрипторной таблицеопределяетсядескрипторсегмента.

Дескриптор- это 8-байтная единица описательной информации, распознаваемая устройством управления памятью взащищенном режиме, хранящаяся вдескрипторной таблице.

Дескрипторсегментасодержит базовый адрес описываемогосегмента, предел (размер)сегментаи права доступа ксегменту. Взащищенном режимесегментымогут начинаться с любого линейного адреса.

Для определения физического адреса базовый адрес сегментасуммируется со смещением.

Существуют две обязательных дескрипторных таблицы- глобальная (GDT) и дескрипторная таблица прерывания (IDT), - а также множество (до 8192) локальных дескрипторных таблиц (LDT), из которых в одинединый момент времени процессору доступна только одна. Расположениедескрипторных таблицопределяетсярегистрамипроцессора GDTR, IDTR, LDTR.

РегистрыGDTR и IDTR - содержат базовый адрес и пределдескрипторной таблицы.

Программно доступная часть регистраLDTR - 16 бит, которые являютсяселекторомLDT.ДескрипторыLDT находятся в GDT. Однако, чтобы не обращаться каждый раз к GDT, в процессоре имеется теневая (программно недоступная) частьрегистраLDTR, в которую процессор помещаетдескрипторLDT при каждой перегрузкеселектораврегистреLDTR.

Рис.

2.1.Программная модель ЦП 8086

Рис.

2.1.Программная модель ЦП 8086