PGTU / 5 семестр / ЦСП для ТК-12бзу / метод.указания по курсовому проектированию

.pdfМинистерство образования и науки РФ

Пермский государственный технический университет

Кафедра автоматики и телемеханики

Методические указания

по выполнению курсового проекта по дисциплине

«Цифровые системы передачи»

для студентов специальности 200900 «Сети связи и системы коммутации»

Проектирование узлов первичного мультиплексора

Пермь, 2009

Целью курсового проекта является разработка отдельных узлов первичного мультиплексора ИКМ-30.

Структура первичного мультиплексора

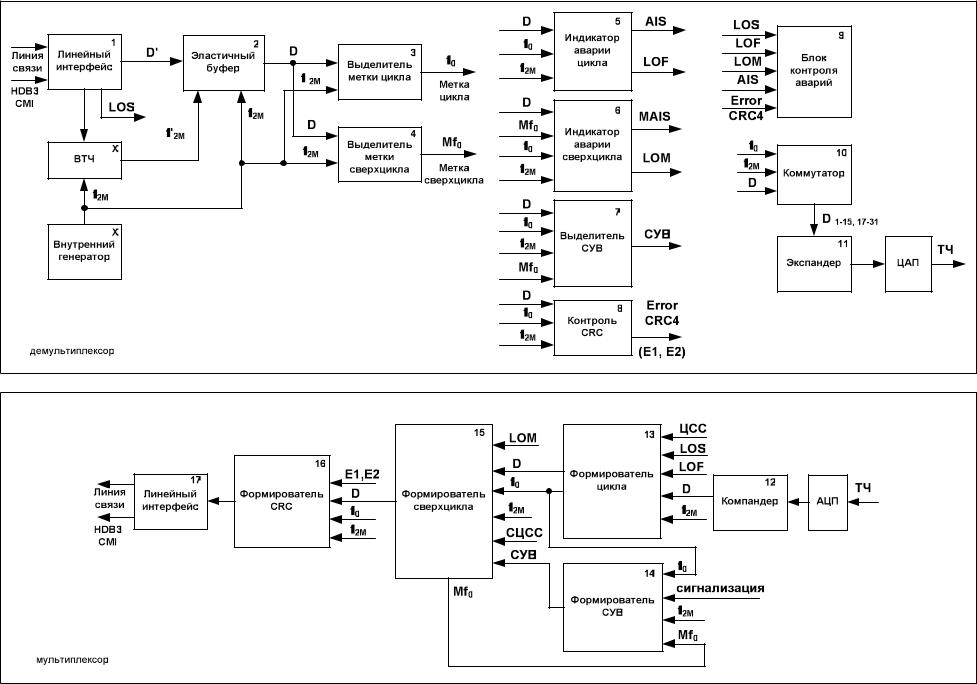

Общая структурная схема первичного мультиплексора представлена на рисунке 1. Условные обозначения сигналов, показанных на схеме:

f2M – тактовая частота, полученная от внутреннего генератора первичного мультиплексора. f'2M – тактовая частота, выделенная из линии связи блоком выделения тактовой частоты (ВТЧ). D – поток данных, обрабатываемый с частотой f2M

D' – поток данных, принятый из линии и обрабатываемый с частотой f'2M f0 – метка цикла

Mf0 – метка сверхцикла

Остальные обозначения соответствуют стандартным обозначениям и аббревиатурам, использующимся в терминологии потока Е1.

В структурной схеме первичного мультиплексора можно выделить две основных части:

1.Демультиплексор – блоки, которые выполняют прием из линии и разборку потока Е1.

2.Мультиплексор – блоки, которые выполняют формирование и передачу в линию потока Е1.

Рассмотрим функционирование отдельных блоков для каждой из частей.

Демультиплексор

Из линии связи приходит поток, в виде последовательности импульсов, сформированных в соответствии с правилами линейного кода. Блок линейного интерфейса выполняет преобразование линейного кода в двоичный код и определяет отсутствие входного сигнала (выдает сигнал LOS).

Так как данные из линии (D') приходят с частотой, заданной предыдущим мультиплексором в линии (f'2M), то их нужно согласовать с частотой внутреннего генератора нашего мультиплексора (f2M). Для этой цели используется блок эластичный буфер, который должен иметь возможность записывать данные с одной частотой, а считывать – с другой. Таким образом, с выхода эластичного буфера выходит поток данных D, тактируемый частотой f2M.

Далее необходимо выполнить анализ цикловой и сверхцикловой структуры потока. Для этой цели используются два блока: выделитель метки цикла и выделитель метки сверхцикла. Оба блока должны искать в приходящем потоке метку цикла и метку сверхцикла, соответственно. При обнаружении метки на их выходе должен появляться импульс, который соответствует моменту прохождения соответствующей метки.

В случае, если произошла потеря циклового или сверхциклового синхронизма, необходимо убедиться, что это действительно произошло и выдать соответствующий аварийный сигнал. Блок индикатора аварии цикла выполняет дополнительную проверку правильности нахождения метки цикла блоком «выделитель метки цикла» и, в случае потери метки цикла, выдает далее вместо потока данных сигнала индикации аварии AIS и сигнал потери цикла LOF. Блок индикатора аварии сверхцикла выполняет дополнительную проверку правильности нахождения метки сверхцикла блоком «выделитель метки сверцикла» и, в случае потери метки сверхцикла, выдает далее в канальном интервале №16 сигнала индикации аварии сверхцикла MAIS и сигнал потери сверхцикла LOM.

Блок выделитель сигналов управления и взаимодействия (СУВ) выполняет распределение сигналов управления и взаимодействия из канального интервала №16 по 30 пользовательским линиям.

Блок контроль CRC выполняет проверку наличия ошибок в принимаемом потоке по процедуре CRC4 и выдает ошибку ErrorCRC4 в случае, если не совпала принятая и вычисленная последовательности битов С1-С4. При обнаружении ошибки в одном из подсверхциклов блок должен выдать единицу на выходе Е1 или Е2, в соответствии с номером подсверхцикла.

Блок контроля аварий должен обрабатывать все аварии, зафиксированные на приеме и выполнять их анализ, выдавая на блок из семисегментных индикаторов мнемоническую запись аварии, которая является первопричиной текущего набора аварий в мультиплексоре.

Блок коммутатор двух каналов должен выполнять перестановку информации из одного канального интервала потока в другой канальный интервал этого потока. Номера канальных интервалов задаются индивидуально для каждого задания.

Блок экспандер выполняет операцию экспандирования по А- или μ-закону компандирования. Блок должен выполнять преобразование из 8-разрядного нелинейного кода (отдельный канальный интервал, поступающий из коммутатора) в 12-разрядный линейный код. 12-разрядные данные поступают на цифро-аналоговый преобразователь (ЦАП) и выводятся на аналоговое окончание ТЧ.

Мультиплексор

Аналого-цифровой преобразователь (АЦП) выполняет преобразование аналогового сигнала ТЧ в цифровой линейный 12-разрядный код и выдает этот код на компандер. Компандер выполняет операцию компандирования по А- или μ-закону компандирования, преобразовывая 12-разрядный линейный код в 8-разрядный нелинейный, в соответствии с законом компандирования. Данные с компандера поступают на блок формирователя цикла.

Блок формирователь цикла выполняет объединение 30 каналов пользователей в цикловую структуру. Так же он должен при формировании канального интервала №0 заполнять цикловой синхросигнал, а также соответствующие биты, в которых индицируются аварии (LOS, LOF), зафиксированные приемником потока Е1 (демультиплексором).

Блок формирователь сигналов управления и взаимодействия (СУВ) выполняет объединение тридцати сигналов от сигнализации каналов пользователей в канальный интервал №16 в соответствии номером текущего цикла в сверхцикле. Сигналы метки цикла и метки сверхцикла приходят с блоков формирователя цикла и формирователя сверхцикла соответственно.

Блок формирователь сверхцикла получает данные в виде последовательности циклов от блока формирователя цикла, и добавляет в канальный интервал №16 сверхцикловой синхросигнал, сигнал индикации потери сверхцикла на приемной стороне, а также принимает сигналы управления и взаимодействия от блока формирователь СУВ.

Блок формирователь CRC выполняет разбиение потока данных на подсверхциклы и обсчитывает их по процедуре CRC4, формируя биты С1-С4. Также в соответствующие позиции вставляются значения бит Е1, Е2.

Блок линейного интерфейса формирует из двоичного сигнала потока данных линейный код и передает его в линию связи.

Выполнение курсового проекта

Каждый студент получает индивидуальное задание в соответствии с номером своего варианта. Необходимо разработать один из блоков, указанных на структурной схеме первичного мультиплексора.

На первом этапе следует изучить все функции, выполняемые указанным блоком, и описать алгоритм функционирования. Далее необходимо разработать структурную схему блока, на которой следует указать основные узлы, из которых состоит блок и связи между ними.

На втором этапе следует составить функциональную схему для разрабатываемого блока. Функциональная схема реализуется с использованием основных элементов цифровой схемотехники. Далее необходимо выполнить моделирование функциональной схемы в одном из прикладных пакетов схемотехнического моделирования.

Структурная схема первичного мультиплексора |

Задание на курсовое проектирование

Разработать блок первичного мультиплексора:

1.Приемник линейного интерфейса по G.703 с реализацией кода HDB3

2.Приемник линейного интерфейса по G.703 с реализацией кода CMI

3.Передатчик линейного интерфейса по G.703 с реализацией кода HDB3

4.Передатчик линейного интерфейса по G.703 с реализацией кода CMI

5.Выделитель метки цикла потока Е1

6.Выделитель метки сверхцикла потока Е1

7.Эластичный буфер

8.Индикатор аварии цикла

9.Индикатор аварии сверхцикла

10.Выделитель сигналов управления и взаимодействия

11.Блок контроля ошибки CRC4

12.Коммутатор 2-х каналов

13.Цифровой компандер, выполняющий сжатие по -закону, с окончанием ТЧ

14.Цифровой компандер, выполняющий сжатие по -закону, с окончанием ТЧ

15.Цифровой экспандер, выполняющий декодирование по -закону, с окончанием ТЧ

16.Цифровой экспандер, выполняющий декодирование по -закону, с окончанием ТЧ

17.Формирователь цикла

18.Формирователь сверхцикла

19.Формирователь CRC4

20.Формирователь сигналов управления и взаимодействия

21.Блок контроля аварий

Требования к оформлению пояснительной записки

При оформлении пояснительной записки необходимо придерживаться следующей структуры:

Содержание Задание на проектирование Введение

1.Теоретическая часть (содержит теоретический материал, относящийся к проектируемому блоку)

2.Разработка блока

2.1.Разработка структурной схемы

2.2.Разработка функциональной схемы

Заключение Список литературы Приложения

Схемы должны быть оформлены в соответствии с требованиями ЕСКД и приведены в приложениях.

Временные диаграммы работы отдельных узлов и всего устройства должны быть приведены в приложениях.

Объем пояснительной записки должен составлять 15-20 страниц.

Процедура защиты курсового проекта

Студент должен показать разработанную схему блока, объяснить принципы функционирования, и продемонстрировать результат схемотехнического моделирования в одном из прикладных пакетов.

Список рекомендуемой литературы

1.Цифровые и аналоговые системы передачи : учебник для вузов / В. И. Иванов [и др.]; Под ред. В. И. Иванова. – Москва: Горячая линия-Телеком, 2003. – 232 с.: ил.

2.И.Г. Бакланов. Технологии измерений первичной сети. Ч. 1. Системы Е1, PDH, SDH / И.Г. Бакланов – М.: Эко;Трендз, 2000. – 142 с.

3.Цифровая схемотехника : учебное пособие для вузов / Е. П. Угрюмов .– 2-е изд., перераб. и доп. – Санкт-Петербург : БХВ-Петербург, 2004 .– 782 с.