§ 9.3. Интегральные микросхемы в системах управления

батываемые сигналы имеют вид импульсов с двумя |

элементов, второй степени – от 11 до 100, третьей |

ярко выраженными уровнями: высокий уровень, |

степени – от 101 до 1000 и т. д. Соответственно |

соответствующий логической ”1” (как правило на- |

различают малые (K = 2), средние (K = 3), большие |

пряжение порядка 5–10 В) и низкий уровень, со- |

(K = 3,4) и сверхбольшие (K = 5,6) ÈÌÑ. |

ответствующий логическому ”0” (как правило на- |

Наиболее сложными ИМС являются микропро- |

пряжение порядка 0–1 В). Аналоговые ИМС пре- |

цессоры (программируемые устройства), которые |

образуют непрерывные переменные во времени |

нашли широкое применение и являются перспек- |

сигналы. |

тивным узлом управления силовых электронных |

Сложность ИМС определяется степенью интег- |

аппаратов. Специфика построения и принципы |

рации K = lgN, ãäå N число элементов входящих |

работы программируемых аппаратов на базе микро- |

в ИМС. В соответствии с этой формулой микро- |

процессоров являются достаточно сложными и по- |

схема первой степени интеграции содержит до 10 |

дробно рассматриваются в гл. 10. |

9.3.2. БАЗОВЫЕ ЦИФРОВЫЕ ИМС

Наиболее простые и распространенные цифровые ИМС – логические элементы. Простейшим логическим элементом является элемент логического отрицания ÍÅ. Выход элемента ÍÅ всегда находится в противоположном состоянии по сравнению с входом, то есть элемент ÍÅ производит инверсию входного сигнала. Другие базовые элементы реализуют логические функции È è ÈËÈ. Изображения элементов на принципиальных схемах приведены на рис. 9.11. Практически все более сложные цифровые устройства основаны на соче- тании этих элементов. Помимо отдельных логических элементов выпускаются микросхемы, содержащие комбинации типа È-ÍÅ, ÈËÈ-ÍÅ, È-ÈËÈ- ÍÅ, È-ÈËÈ è äð.

На основе логических элементов можно синтезировать схемы любых логических преобразований Булевой алгебры, а так же более сложные цифровые устройства, такие как ячейки памяти, счетчики импульсов и др. Промышленность серийно выпускает различные типы цифровых устройств, структура большинства которых основана на логических элементах [94].

Важной характеристикой логических ИМС является быстродействие или длительность фронта импульсов на выходе ИМС. Для современных логических элементов характерными значениями длительности фронтов являются десятки и даже единицы наносекунд.

По виду компонентов, входящих в цифровые ИМС, их разделяют на следующие типы: ТЛ – транзисторная логика; РТЛ – резисторно-транзис- торная логика; ДТЛ – диодно-транзисторная логика; ТТЛ – транзисторно-транзисторная логика. Наиболее широкое распространение получили два последних типа.

Широкое распространение получили цифровые ИМС релейного типа, имеющие два устойчивых состояния и называемые триггерами. Переход триггера из одного устойчивого состояния в другое происходит под воздействием сигнала управления и сопровождается скачкообразным изменением выходных токов и напряжений. В настоящее время выпускаются серии различных триггеров в виде самостоятельных ИМС.

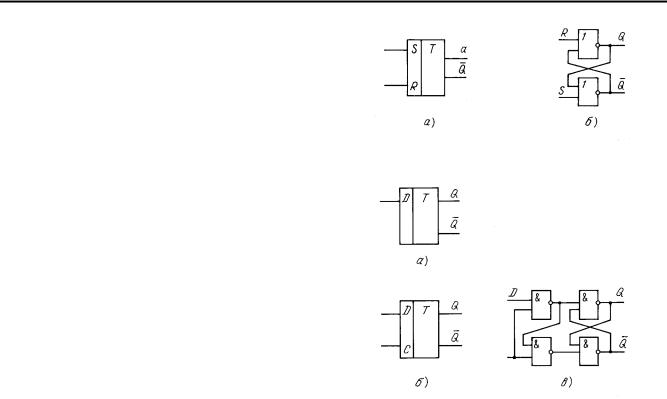

Наиболее простой симметричный триггер может быть выполнен на основе двух элементов È-ÍÅ (ðèñ. 9.12,à) или двух элементов ÈËÈ-ÍÅ (ðèñ. 9.12,á). Если на выходе одного логического элемента, например F1 имеется сигнал логической единицы, то на входе второго тоже будет сигнал ”1”. На выходе второго и на входе первого элемента будет сигнал логического нуля, так как элементы содержат на выходе функцию ÍÅ. Логический нуль на входе первого элемента обеспечивает единицу на его выходе, таким образом описанное состояние

Рис. 9.11. Логические элементы: |

Рис. 9.12. Простейший триггер: |

à – ÍÅ; á – ÈËÈ; â – È |

à – на элементах ÈËÈ-ÍÅ; á – на элементах È-ÍÅ |

253

Гл. 9. Системы управления силовыми электронными аппаратами

является устойчивым. Изменение одного входного, а, следовательно, и выходного сигнала приводит схему в противоположное устойчивое состояние.

Более распространенной является схема RS- триггера (рис. 9.13). RS-триггер имеет два информационных входа S (îò àíãë. set) è R (îò àíãë. reset)

èдва инверсных относительно друг друга выхода Q

èQ. Ïðè R = 0 è S = 1 выход принимает состояние Q = 1, à ïðè R = 1 è S = 0 состояние Q = 0. Таким образом сигнал логической единицы на входе S

устанавливает” единицу на выходе, а на входе R ””сбрасывает”. При нулевом сигнале на входах триггер не меняет своего состояния, поэтому он может использоваться как простейший элемент памяти. Комбинация R = 1 è S = 1 приводит к неопределенному состоянию на выходах и является запрещенной.

Более сложным примером триггера является тактируемый RS-триггер, который имеет синхронизирующий вход. Это позволяет изменять выходные сигналы только в момент подачи тактовых импульсов.

D-триггер иногда называют триггером задержки. Он имеет один информационный вход D (ðèñ. 9.14,à) и два устойчивых состояния. Состояние триггера в момент времени tn+1 совпадает с кодом

входного сигнала, существовавшего в момент времени tn. Время задержки переключения триггера определяется задержкой распространения сигнала в логическом элементе.

Наиболее часто применяют синхронизируемые D-триггеры (рис. 9.14,á). Изменение сигнала на выходе такого триггера происходит только по сигналу тактового импульса на входе C; при отсутствии тактового импульса схема не меняет своего состояния при любых изменениях на информационном входе. Схема D-триггера может содержать четыре элемента È-ÍÅ, соединенных по определенной схеме (рис. 9.14,â).

T-триггер иногда называют счетным, потому что он меняет свое состояние на противоположное

Ðèñ. 9.13. RS-триггер:

à – обозначение; á – принципиальная схема

Ðèñ. 9.14. D-триггер:

à – обозначение несинхронизируемого D-триггера; á – обозна- чение синхронизируемого D-триггера; â – принципиальная схема

всякий раз, когда на его вход поступает сигнал логической единицы. T-триггер является основным элементом для построения счетных устройств.

JK-триггер имеет два входа J è K. Функционально он подобен RS-триггеру, вход J соответствует входу S, à âõîä K входу R. Отличие заключается в том, что комбинация J = 0 R = 0 не является запрещенной, а меняет состояние выхода на противоположное.

Существуют триггеры типов V, R, E, TV и другие, но применяются они значительно реже [95].

9.3.3. БАЗОВЫЕ АНАЛОГОВЫЕ ИМС

К аналоговым микросхемам относят те виды |

ствами ОУ являются высокий (103–106) коэффици- |

|

ИМС, работа которых связана с обработкой анало- |

ент усиления, высокое входное и низкое выходное |

|

говых (непрерывных во времени) сигналов. Такими |

сопротивления, широкий диапазон рабочих частот. |

|

элементами являются усилители сигналов, генера- |

Операционный усилитель имеет два входа (рис. |

|

торы аналоговых сигналов, фильтры, перемножи- |

||

9.15.) прямой Uâõ1 и инверсный Uâõ2. Выходное |

||

тели сигналов и др. |

||

напряжение Uâûõ находится в фазе с входным на- |

||

В настоящее время широко распространены |

||

пряжением Uâõ1 и в противофазе с входным напря- |

||

операционные усилители (ОУ). Свое название ОУ |

||

жением Uâõ2. Питание ОУ осуществляется от двух |

||

получили благодаря возможности их использова- |

||

ния в различных функциональных схемах, за счет |

последовательно соединенных источников ±E ñ çà- |

|

применения обратных связей. Главными достоин- |

земленной средней точкой. Все входные и выход- |

254

§ 9.4. Линейные усилители и преобразователи аналоговых сигналов

Рис. 9.15. Операционный усилитель:

à – обозначение; á – передаточные характеристики

ные сигналы ОУ измеряются относительно средней точки (земли) источника питания. Благодаря организации такого питания ОУ имеет возможность усиливать двуполярные сигналы. Питание ОУ должно быть стабильным и симметричным относительно средней точки, как правило типовые схемы ОУ имеют питание ±5 В, ±12,6 В или ±15 В. Напряжение между входами ОУ равно разности Uâõ1 è Uâõ2, т. е. является дифференциальным. Учитывая высокие показатели ОУ, при рассмотрении схем их подключения принимают следующие допущения:

коэффициент усиления по постоянному току ÊÓ ® ¥; входное сопротивление Râõ ® ¥; выходное сопротивление Râûõ ® ¥; полоса частот пропускаемых ОУ от 0 до ¥. Работу ОУ можно пояснить с помощью схемы без обратных связей (рис. 9.15,à). Если входной сигнал на инверсном входе равен нулю, то связь между входным сигналом прямого входа и выходным сигналом определяется характеристикой, показанной на рис. 9.15,á сплошной линией, и наоборот, если на прямом входе сигнал равен нулю, то инверсный вход определяет выходной сигнал в соответствии с характеристикой, показанной штриховой линией. Если оба сигнала отличны от нуля, то их разность усиливается согласно характеристике, соответствующей большему по амплитуде сигналу. Наклон характеристик определяется собственным коэффициентом передачи, а предельное выходное напряжение определяется напряжением питания. Благодаря высоким коэффициентам усиления ОУ в схеме без обратных связей может усиливать только очень маленькие сигналы, не входя в так называемое насыщение”, когда выходное напряжение равно” напряжению питания со знаком ”+” èëè ”–”.

Контрольные вопросы и задачи

1.Сколько элементов может содержать ИМС с 4-й степенью интеграции?

2.Составьте таблицу истинности для логических элементов È è ÈËÈ с тремя входами.

3.Почему подача логических единиц на входы RS-триггера является запрещенной и к какому состоянию выходов это приведет?

4. Ïðè |

каком входном сигнале |

прямого входа |

ОУ наступит его насыщение, |

åñëè E = ±15 Â, |

|

ÊÓ = |

50 000? Сигнал на инверсном входе равен |

|

íóëþ. |

|

|

5. Решить задачу п.4 при Uâõ2 = 3,4 Â.

9.4.ЛИНЕЙНЫЕ УСИЛИТЕЛИ И ПРЕОБРАЗОВАТЕЛИ АНАЛОГОВЫХ СИГНАЛОВ

9.4.1.УСИЛИТЕЛИ СИГНАЛОВ

В системах управления широко используются усилители сигналов тока или напряжения с определенным коэффициентом усиления. Усилитель может быть выполнен на дискретных транзисторных элементах. Однако наиболее рациональным является применение схем усиления на основе ОУ (операционных усилителей).

На практике существует две базовые схемы усилителей на основе ОУ: инвертирующего и неинвертирующего. Рассмотрим каждую из них.

Название инвертирующий усилитель схема (рис. 9.16) получила благодаря ее свойству изменять полярность выходного сигнала относительно полярности входного сигнала. Полагая ОУ идеальным (т. е. принимая указанные в 9.3 допущения), можно считать, что разность между сигналами обоих вхо-

дов мала (иначе усилитель войдет в насыщение”). Действительно если Uâûõmax = 15  è”коэффициент

усиления KÓ = 104, то максимальное дифференциальное входное напряжение равно 1,5 мВ. Так как один вход заземлен, то потенциал второго входа близок к потенциалу земли. Поэтому можно счи- тать, что ко второму входу подходят токи

I1 » Uâõ ¤ R1; I2 » Uâûõ ¤ R2 . |

(9.11) |

Считая входное сопротивление достаточно большим, на основании закона Кирхгофа запишем:

(Uâõ ¤ R1) + (Uâûõ ¤ R2) = 0 |

(9.12) |

èëè |

|

Uâûõ = -UâõR2 ¤ R1 . |

(9.13) |

255

Гл. 9. Системы управления силовыми электронными аппаратами

Рис. 9.16. Схема инвертирующего усилителя на ОУ

Рис. 9.17. Схема неинвертирующего усилителя на ОУ

Таким образом коэффициент усиления инвертирующего усилителя определяется отношением сопротивлений резисторов R1 è R2. Номинальные значения резисторов в схемах с операционным усилителем, могут быть произвольными, однако необходимо учитывать следующее: с одной стороны, номинальные значения резисторов должны ограни- чивать входные и выходные токи операционного усилителя во избежание выхода его из строя. В паспортных данных операционного усилителя указы-

ваются максимальные значения входных и выходных токов схемы. С другой стороны номинальные значения резисторов не должны превышать единицы мегаом, так как при больших значениях возможна нестабильная работа усилителя из-за влияния токов утечек на корпус микросхемы через монтаж печатной платы и др. На практике сопротивление резисторов в схемах с операционным усилителем лежит в диапазоне от десятков килоом до единиц мегаом, что позволяет получить устойчивые устройства с большим входным сопротивлением.

В целях уменьшения ошибки, связанной с дрейфом входных параметров, стремятся, чтобы эквивалентные сопротивления подключенных к входам резисторов были равны. В схеме инвертирующего усилителя сопротивление R3 стремятся выбрать равным эквивалентному сопротивлению резисторов R1 è R2, соединенных параллельно.

Схема неинвертирующего усилителя (рис. 9.17) содержит сопротивление R2 в цепи отрицательной обратной связи, но входной сигнал подается на неинвертирующий вход. Его принцип действия аналогичен принципу действия инвертирующего усилителя. Нетрудно показать, что для этой схемы:

Uâûõ = Uâõ(1 + R2 ¤ R1) . |

(9.14) |

Стремятся, чтобы эквивалентное сопротивление, равное сопротивлению параллельно соединенных резисторов R1 è R2, было равно R3, и номинальные значения резисторов должны находиться в диапазоне 10¸1000 кОм.

9.4.2. ПРЕОБРАЗОВАТЕЛИ АНАЛОГОВЫХ СИГНАЛОВ

Помимо усиления в схемах управления часто возникает необходимость преобразовывать сигналы управления по определенным функциям, таким как суммирование, перемножение, интегрирование, дифференцирование и др. Как правило, такие преобразователи строятся на основе интегральных микросхем, в большинстве случаев – ОУ (рис. 9.18).

Примером может служить сумматор на основе ОУ. Напряжение на выходе при равных значениях входных сопротивлений R1 = R2 = R3...Rn = R

æR2öån U . (9.15)

Uâûõ = -ç ÷ âõi

è R ø

i = 1

Для получения частотно-зависимых передаточ- ных характеристик в цепи обратных связей вводятся реактивные элементы. Например, в схеме интегрирующего или дифференцирующего усилителя необходимо (см.рис. 9.16) заменить активные со-

противления R1 è R2 комплексными Z1(p) è Z2(p). Передаточная функция схемы на ОУ будет иметь вид

W(p) = |

Uâûõ(p) |

= - |

|

Z2(p) |

. |

(9.16) |

|||

|

|

|

|||||||

|

U |

âõ |

(p) |

|

Z (p) |

|

|||

|

|

|

|

|

1 |

|

|

||

Существуют интегрирующий усилитель |

(ðèñ. |

||||||||

9.19,à) с передаточной функцией |

|

|

|||||||

|

|

|

1 |

|

|

|

|

||

W(p) = − |

|

|

|

|

(9.17) |

||||

pR C |

|

|

|

||||||

|

|

|

1 |

|

|

|

|

||

и дифференцирующий усилитель (рис. 9.19,á) с передаточной функцией

W(p) = −pCR2 . |

(9.18) |

Подбирая различные значения Z1(p) è Z2(p), можно получать различные передаточные характеристики усилителя. Это свойство нашло широкое применение в системах автоматического регулирования в цепях коррекции динамических характеристик систем.

256

§ 9.4. Линейные усилители и преобразователи аналоговых сигналов

Рис. 9.18. Схема сумматора на ОУ

Рис. 9.21. Функциональные усилители:

à – логарифмирующий; á – антилогарифмирующий

Рис. 9.19. Схема интегрирующего (à) и дифференцирующего (á) |

Рис. 9.22. Схема умножителя |

усилителя |

|

Рис. 9.20. Гиратор |

Рис. 9.23. Умножитель на дискретных транзисторах |

Схемы интегрирующего и дифференцирующего усилителя могут использоваться как активные фильтры нижних и верхних частот. Усложняя передаточные функции Z1(p) è Z2(p), можно получать более сложные полосовые активные фильтры (в данном случае активными такие фильтры называют потому, что ОУ содержит источники питания и является активным элементом). Эти фильтры более эффективны, чем пассивные (на основе RLC- элементов), так как имеют повышенную доброт-

ность и практически произвольную передаточную функцию.

В системах управления нецелесообразно применять индуктивные элементы, так как они имеют повышенные массогабаритные и стоимостные показатели по сравнению с емкостными элементами, кроме того электромагнитное поле, возникающее в индуктивностях, может вызывать помехи в других элементах схемы. Для исключения из схем индуктивных элементов применяют схемы, преобразую-

257

Гл. 9. Системы управления силовыми электронными аппаратами

щие емкость конденсатора в индуктивность. Такая |

рованную степенным многочленом, дробно-рацио- |

|||||||

схема на ОУ называется гиратором (ðèñ. 9.20). |

нальным выражением или рядом экспонент [95]. |

|||||||

В этой схеме ток и напряжения на входе изменя- |

Логарифмирование |

è |

антилогарифмирование |

|||||

ются подобно току и напряжению в индуктивности. |

может |

осуществляться |

ñ |

помощью схем |

íà ÎÓ |

|||

Эквивалентные индуктивность и добротность дан- |

с диодом или транзистором в цепи обратной связи |

|||||||

ной схемы определяются |

|

|

(ðèñ. 9.21). |

|

|

|

|

|

2 |

2 2 |

(9.19) |

Для перемножения или деления двух сигналов |

|||||

L = CR1R2 ¤ (1 + w |

C R2) ; |

можно использовать схему (рис. 9.22), основанную |

||||||

Q = wC ¤ (1 + w2C 2R1R2) . |

|

|||||||

|

на известном правиле преобразования операции |

|||||||

Основным недостатком гираторов являются огра- |

умножения в операцию суммирования путем лога- |

|||||||

ниченность диапазона рабочих частот (десятки кило- |

рифмирования. |

Основным недостатком |

такой |

|||||

герц) и невозможность заземления выходной цепи. |

схемы является то, что все входные сигналы долж- |

|||||||

Для осуществления функциональных преобра- |

ны быть положительными и отличными от нуля. |

|||||||

зований (логарифмирование, антилогарифмирова- |

Более |

сложные |

схемы |

умножителей (рис. 9.23) |

||||

ние, умножение, деление) используются различные |

могут осуществлять умножение двухполярного сиг- |

|||||||

методы, как правило, построенные на нелинейных |

нала напряжения e1 и однополярного тока i2. Îòå- |

|||||||

ВАХ полупроводниковых приборов. Возможность |

чественной промышленностью выпускаются ин- |

|||||||

таких преобразований совместно с линейными пре- |

тегральные схемы умножителей аналоговых сигна- |

|||||||

образователями (усилителями и сумматорами) по- |

лов, позволяющие создавать более компактные |

|||||||

зволяет реализовать любую функцию, аппроксими- |

перемножители двухполярных сигналов. |

|

||||||

Контрольные вопросы и задачи

1.Рассчитайте значения сопротивлений в схеме неинвертирующего усилителя (см. рис. 9.17), если входной сигнал имеет амплитуду Uâõ max = 0,1 В, коэффициент усиления KÓ = 50, допустимые зна- чения входных и выходных токов Iâõ max = 10 ìÀ, Iâûõ max = = 20 мА. Определить так же минимально допустимое значение сопротивления нагрузки усилителя.

2.Рассчитайте параметры схемы сумматора трех аналоговых сигналов напряжения с максимальной амплитудой входных сигналов Uâõ max = 5 Â,

допустимые значения входных и выходных токов Iâõ max = 10 ìÀ, Iâûõ max = 20 мА. Суммирование должно производиться по закону: Uâûõ =

= 5Uâõ1 + 3Uâõ2 + 12Uâõ3.

3.Рассчитайте схему интегрирующего усилителя (см. рис. 9.19) с постоянной интегрирования равной 0,1, если входное напряжение имеет амплитуду Uâõ max = 5 В, допустимые значения вход-

ных и выходных токов Iâõ max = 15 ìÀ, Iâûõ max =

= 50 ìÀ.

4.Какова должна быть схема обратных связей ОУ, чтобы он имел

Z(p) = 1 + 0,0025p ?

1 + 0,00005 p2

5.Синтезируйте структурную схему возведения аналогового сигнала в третью степень, используя узлы логарифмирования, антилогарифмирования, суммирования и усиления.

9.5. ФОРМИРОВАТЕЛИ ИМПУЛЬСОВ УПРАВЛЕНИЯ

9.5.1. УПРАВЛЕНИЕ БИПОЛЯРНЫМ ТРАНЗИСТОРОМ

Формирователями импульсов управления (ФИУ) называется особый класс усилителей, предназна- ченных для усиления информационного сигнала управления до сигнала с параметрами, необходимыми для гарантированного включения и выклю- чения полупроводникового ключа. Помимо требований к мощности сигнала управления ключом, часто предъявляются требования к форме сигнала, поэтому иногда ФИУ называют усилителем-форми-

рователем импульсов управления. Схемотехника ФИУ в первую очередь зависит от типа управляемого прибора. Особенности схемотехники ФИУ определяются статическими и динамическими свойствами соответствующего типа прибора (см. гл. 7).

Основными требованиями, предъявляемыми к ключу на биполярном транзисторе, являются гарантированное насыщение транзистора током базы, обеспечивающее беспрепятственное протека-

258

§ 9.5. Формирователи импульсов управления

ние тока коллектора на интервале, когда транзистор должен быть включен, и снижения тока утечки на интервале, когда транзистор должен быть выклю- чен. Идеальная форма базового тока iB и напряжения база-эмиттер UBE биполярного транзистора представлены на рис. 9.24 [81].

При реализации такого импульса необходимо учитывать следующее:

–повышенная амплитуда тока базы при вклю- чении обеспечивает снижение времени задержки на включение;

–биполярный транзистор включается током, поэтому ФИУ должен соответствовать источнику

тока, а не источнику напряжения (это приводит

êснижению потерь на управление);

–после включения ток базы снижается, в результате чего накопленный в базе заряд уменьшается (это приводит к снижению времени для следующего выключения);

–импульс обратного тока базы при выключе- нии приводит к более быстрому спаду тока коллектора iC, т.е. к более быстрому выключению;

–после выключения обратное напряжение

база-эмиттер UBE обеспечивает повышение допустимого напряжения коллектор-эмиттер UCE и снижает ток утечки транзистора.

На практике необязательно осуществлять такое сложное управление, требующее дополнительных устройств в цепях ФИУ. Требования к сигналу управления определяются требованиями к быстродействию ключа (рабочая частота коммутаций)

и к потерям в нем. Проблема в создании ФИУ биполярных транзисторов состоит еще и в том, что не всегда возможно соединение ”земли” системы управления и эмиттера транзистора. Часто нагрузка подключается к эмиттеру транзистора (рис. 9.25). В этом случае необходимость гальванической развязки между цепями системы управления и силовой схемой является обязательной функцией ФИУ.

Рис. 9.24. Идеальный импульс управления биполярным транзистором

Рис. 9.25. Схема включения нагрузки транзистора в цепь эмиттера

Рис. 9.26. ФИУ биполярного транзистора: à – схема транзисторного усилителя; á – схема на парных транзисторах;

â – схема, контролирующая время включения и выключения

259

Гл. 9. Системы управления силовыми электронными аппаратами

Простейшая схема ФИУ биполярного транзистора представлена на рис. 9.26,à. В схеме реализован усилительный каскад с двумя дополнительными транзисторами для увеличения маломощного сигнала микросхемы до необходимого значения и источником отрицательного напряжения для создания в моменты паузы (когда ключ выключен) отрицательного смещения. Это способствует более полному и более надежному запиранию транзистора. Для уменьшения потребляемой ФИУ мощности применяют парные (комплементарные) транзисторы VT2, VT3, работающие попеременно (рис. 9.26,á). Когда импульс управления отсутствует (Uóïð = 0), транзистор VT4 открыт, и через его коллектор протекает отпирающий ток базы VT2. Силовой тран-

зистор VT1 открывается усиленным током коллектора транзистора VT2. Транзистор VT3 при этом заперт, так как его эмиттер имеет отрицательный потенциал относительно базы. Через конденсатор C1 проходит ток базы силового транзистора, обеспечивая бросок тока для его быстрого включения. В момент поступления импульса от микросхемы управления транзисторы VT4 è VT2 закрываются, а транзистор VT3 включается напряжением конденсатора C1, который разряжаясь обеспечивает запирающий базовый ток силового транзистора.

Реально схемы ФИУ биполярных транзисторов могут быть более сложными и обеспечивать условия контроля скорости включения и выключения силовых транзисторов (рис. 9.26,â).

9.5.2. УПРАВЛЕНИЕ ПОЛЕВЫМИ ТРАНЗИСТОРАМИ

Особенности управления полевым транзистором связаны, во-первых, с тем, что при постоянном напряжении затвор-исток UGS через затвор протекает незначительный ток (примерно несколько наноампер), во-вторых на процессы включения и выключения значительное влияние оказывает входная емкость транзистора, скорость перезаряда которой определяет время включения и выключе- ния транзистора. Управление БТИЗ аналогично полевому транзистору, так как конструктивно затвор БТИЗ аналогичен затвору МОП-транзистора.

Поэтому основные принципы управления полевым транзистором аналогичны принципам управления БТИЗ.

Полевым транзистором можно управлять выходным сигналом микросхемы системы управления, напряжением 5–15 В и током менее ста миллиампер (рис. 9.27,à). Однако для управления мощными транзисторами применяют усилители, схема которых соответствует схеме двухтактного эмиттерного повторителя на парных биполярных транзисторах (рис. 9.27,á). В этой схеме биполярные транзисторы

Рис. 9.27. ФИУ полевого транзистора:

à – управление от ИМС; á – усилитель на парных транзисторах; â – схема подключения специальной ИМС для управления полевым транзистором; ã – двухтактный ключ на МДП транзисторах; ä – схема с гальванической развязкой через импульсный трансформатор

260

§ 9.5. Формирователи импульсов управления

в активном режиме играют роль источников тока для более быстрого перезаряда входной емкости МОП-транзистора. Очень малые времена переклю- чения могут обеспечиваться специальной быстродействующей ключевой микросхемой (рис. 9.27,â), которая способна переключать ток около одного

ампера за десятки наносекунд. В этой схеме просто организуется и гальваническая развязка посредством оптопары. Кроме того, применяют более сложные ФИУ, например двухтактную схему (рис. 9.27,ã) или с использованием импульсного трансформатора (рис. 9.27,ä) [81].

9.5.3. УПРАВЛЕНИЕ ТИРИСТОРОМ

Схема управления тиристором подает на управляющий электрод импульсы только на включение. Подача импульса должна происходить тогда, когда напряжение анод-катод тиристора положительно, в противном случае включение не произойдет. Идеальный импульс на включение (рис. 9.28) должен иметь большую скорость нарастания тока при включении и повышенную амплитуду в начальный момент, что ускоряет процесс включения и снижает вероятность выхода его из строя из-за повышенной скорости нарастания анодного тока diA ¤ dt. После завершения процесса включения импульс управления желательно ”обнулить”, так как продолжительный импульс увели- чивает потери мощности в тиристоре. Однако необходимо учитывать, что при наличии в нагрузке индуктивной составляющей процесс включения затягивается, и в этом случае импульс должен иметь повышенную длительность для гарантированного включения.

Типовая схема управления тиристором, использующая импульсный трансформатор, представлена на рис. 9.29,à. Äèîä VD1 и стабилитрон VD2 обеспечивают перемагничивание трансформатора и предотвращают перенапряжение на транзисторе VT1. Резистор R1 ограничивает ток управляющего электрода тиристора VS1 и одновременно ток коллектора транзистора VT1. Резистор R2 защищает тиристор от самопроизвольного включения помехами, а диод VD3 предотвращает появление отрицательного напряжения на управляющем электроде тиристора VS1.

Запираемый тиристор выключается импульсом отрицательного тока управляющего электрода. Схема драйвера для двухоперационного тиристора значи- тельно сложнее, чем для однооперационного, и по топологии близка к схемам ФИУ биполярного транзистора (рис. 9.30).

Рис. 9.28. Идеальный импульс управления тиристором

Рис. 9.29. ФИУ обычного тиристора |

Рис. 9.30. ФИУ запираемого тиристора |

261

Гл. 9. Системы управления силовыми электронными аппаратами

Контрольные вопросы и задачи

1.Объясните, почему идеальный импульс управления биполярным транзистором имеет такую сложную форму, как на рис. 9.24?

2.Рассчитайте сопротивления в схеме рис. 9.26,à,

если коэффициенты усиления по току транзисторов VT1, VT2, VT3 равны β1 = 5, β2 = 15, β3 = 35 соответственно, источники напряжения E1 = 30 Â, E2 = −10 В, амплитуда импульсов управления Uó = 5 В, при максимальном токе 100 мА, ток нагрузки Ií = 30 À.

3.Рассчитайте сопротивления в схеме рис. 9.26,á, если коэффициенты усиления по току транзисторов VT1, VT2, VT3, VT4 равны β1 = 7, β2 = 10, β3 = 10 è β4 = 50 соответственно, источники напряжения E1 = 40 Â, E2 = −15 В, амплитуда импульсов управления UÓ = 15 В при максимальном

токе 20 мА. При включении необходимо создать бросок тока базы транзистора VT1 длительностью 5 мкс и превышающий номинальный ток в два раза; ток нагрузки Ií = 50 À.

4.Каким основным преимуществом обладают полевые транзисторы по сравнению с биполярными построения ФИУ?

5.Объясните принцип действия схемы на рис. 9.27,ã.

6.Рассчитайте параметры ФИУ тиристора (см. рис. 9.29), если ток управляющего электрода тиристо-

ðà IG = 15 А, напряжение источника питания E1 = 30 В, ток базы транзистора iB = 0,5 A, коэффициент усиления транзистора по току βVT1 = 10.

7.Объясните принцип действия схемы управления двухоперационным тиристором (см. рис. 9.30).

9.6.ГЕНЕРАТОРЫ И РАСПРЕДЕЛИТЕЛИ ИМПУЛЬСОВ

9.6.1.ГЕНЕРАТОРЫ СИГНАЛОВ

В схемах систем управления часто используются генераторы сигналов различного вида. Существуют специальные интегральные схемы генераторов прямоугольных сигналов, линейно изменяющихся сигналов, гармонических сигналов и т. д. Однако более традиционными являются схемы на основе ОУ и интегральных компараторов.

Рассмотрим схему и диаграммы напряжения генератора прямоугольных импульсов (называемого так же мультивибратором) на ОУ (рис. 9.31,à). Допустим, в первый момент конденсатор C разряжен, а выходное напряжение равно E (положительная обратная связь обеспечивает два устойчивых состояния E è −E) (ðèñ. 9.31,á). Конденсатор начи- нает заряжаться через резистор R1, напряжение конденсатора стремится к E, а напряжение на неинвертирующем входе ОУ определяется резистивным делителем R2, R3. В момент равенства напряжений на входах схема меняет состояние, и напряжение на выходе становится равным −E, а конденсатор начинает перезаряжаться до напряжения обратной полярности. Далее процессы переключения повторяются. Частота импульсов определяется постоян-

ной времени перезаряда |

конденсатора |

τ = R1C |

|||

и соотношением сопротивлений |

резисторов R1 |

||||

è R2 |

|

|

|

|

|

f = |

|

1 |

|

. |

(9.20) |

2R C ln(1 + 2R ¤ R ) |

|||||

1 |

3 |

2 |

|

|

|

Принцип работы мультивибратора на основе интегральной схемы компаратора (рис. 9.31,â) аналогичен работе генератора прямоугольных импульсов на ОУ.

Существуют так же схемы генераторов однополярных импульсов, генераторы с переменной частотой и с переменной скважностью [95].

Разновидностью генераторов импульсов является схема ждущего мультивибратора или одновибратора. Отличие от мультивибратора заключается в том, что такая схема (рис. 9.32) имеет одно устойчивое состояние. При поступлении на вход схемы короткого запускающего импульса Uçàï,

схема переходит в неустойчивое состояние (при этом формируется выходной сигнал) и остается в этом состоянии определенное параметрами схемы время. Затем схема возвращается в устойчивое состояние. Одновибраторы применяются для формирования импульсов управления определенной длительности.

Основой генераторов синусоидальных сигналов является так называемый мост (полумост) Вина (рис. 9.33,à), имеющий экстремум передаточной характеристики (рис. 9.33,á). Генератор на основе ОУ (рис. 9.33,â), содержащий полумост Вина, вырабатывает синусоидальный сигнал частотой

ω = Ö````````R R C C .

1 2 1 2

262