Экзамен микроэлектроника / Лекции / 5. Элементы цифровой схемотехники

.docxЭлементы цифровой схемотехники

Последовательное и параллельное соединение ключей. Захват тока. Нагрузочная способность.

Параллельное

соединение транзисторных ключей. На

практике зачастую один источник сигнала

может управлять несколькими ключами,

см. рис.

может управлять несколькими ключами,

см. рис.

В этом случае база-эмиттерные переходы транзисторов оказываются включенными параллельно. Очевидно, что общий ток от генератора делится между токами баз транзисторов:

.

.

Если транзисторы и их режимы идентичны, то общий ток поделится поровну:

.

.

Если же входные характеристики не идентичны, то при одном и том же значении напряжения на база-эмиттерном переходе токи могут существенно различаться.

Причиной различия входных характеристик может быть характер нагрузки. На рис. Видно, что при небольшом отклонении в характеристиках токи базы могут существенно отличаться. Видно, что ток базы первого транзистора в несколько раз больше тока базы другого транзистора. Это явление называется захватом тока. В какой-то степени компенсировать разницу входных характеристик можно, добавив резисторы в базовые цепи ТК, см. рис.

Последовательное включение ТК.

Отдельные ТК используются, как правило, в аналоговых схемах. В цифровых схемах используют цепочки ключей, см. рис.

Рассмотрим последовательную ключевую цепочку.

Если

транзистор Т1 открыт и насыщен, то

потенциал

и равный ему потенциал

и равный ему потенциал

близки к нулю, а значит транзистор Т2

заперт. Тогда в базу Т3 протекает ток от

источника

близки к нулю, а значит транзистор Т2

заперт. Тогда в базу Т3 протекает ток от

источника

через резистор

через резистор

,

и транзистор Т3 открыт. Таким образом,

в последовательной

ключевой цепочке характерно чередование

открытых и закрытых ключей.

,

и транзистор Т3 открыт. Таким образом,

в последовательной

ключевой цепочке характерно чередование

открытых и закрытых ключей.

Стоит

отметить, что в отличие от изолированного

ключа, напряжение на коллекторе запертого

ключа будет не

,

а

,

а

,

что обусловлено подключением коллектора

к базе следующего, открытого ключа.

,

что обусловлено подключением коллектора

к базе следующего, открытого ключа.

Нагрузочная способность ключа.

Типичным для ключевых схем является сочетание последовательного и параллельного соединений. А именно, в последовательной цепочке каждый транзистор может управлять не одним, а несколькими параллельно включенными транзисторами.

Нагрузочной

способностью называют количество

параллельно включенных ключей, которыми

способен управлять данный ключ.

Обозначим это количество через

.

.

Предположим,

что суммарный отпирающий ток делится

поровну между

базами; тогда в каждом из параллельно

включенных ключей

базами; тогда в каждом из параллельно

включенных ключей

В

этом случае

должен удовлетворять критерию насыщения

(

должен удовлетворять критерию насыщения

( ),

где коллекторный ток определяется

выражением:

),

где коллекторный ток определяется

выражением:

.

.

Из критерия насыщения нетрудно получить принципиальное ограничение на нагрузочную способность:

.

.

На

самом деле ограничение следует сделать

более жестким, поскольку нужно обеспечить

не просто насыщение ( ),

а минимальную степень насыщения:

),

а минимальную степень насыщения:

.

.

Схемотехника логических элементов

Логические уровни и помехоустойчивость.

Уровни

напряжений, соответствующие логической

единице на входе ЛЭ ( )

и выходе ЛЭ (

)

и выходе ЛЭ ( ),

а также соответствующие уровни логического

нуля –

),

а также соответствующие уровни логического

нуля –

и

и

обладают разбросами и температурными

зависимостями. Количественно это

оценивается такими параметрами ЛЭ, как

помехоустойчивость по логической

единице и помехоустойчивость логическому

нулю:

обладают разбросами и температурными

зависимостями. Количественно это

оценивается такими параметрами ЛЭ, как

помехоустойчивость по логической

единице и помехоустойчивость логическому

нулю:

Смысл приведенных уравнений заключается в следующем:

-

Помехоустойчивость по логической единице определяется как разница между минимальным напряжением логической единицы на выходе ЛЭ минимальным напряжением логической единицы на входе следующего ЛЭ.

-

Помехоустойчивость по логическому нулю определяется как разница между максимальным напряжением логического нуля на выходе ЛЭ и максимальным напряжением логического нуля на входе следующего ЛЭ.

Помехоустойчивость можно изобразить на передаточной характеристике ЛЭ:

Или более наглядно на диаграмме:

Логическим элементом называется электронная схема, выполняющая простейшие логические операции.

Логические функции.

Логические функции и операции над ними являются предметом алгебры логики или булевой алгебры.

В основе алгебры логики лежат логические величины, которые обозначают буквами A, B, C и т.д. логическая величина может принимать два значения: истина и ложь, которые удобно обозначать с помощью двоичного кода: 1 (истина) и 0 (ложь).

Перечислим кратко простейшие логические операции:

-

Отрицание или инверсия, или операция НЕ. Схему, которая выполняет операцию отрицания называют схемой НЕ.

Функция отрицания является функцией одного аргумента.

-

Логическое сложение или дизъюнкция, логическое ИЛИ – функция двух и более аргументов:

-

Логическое умножение или конъюнкция, логическое И.

-

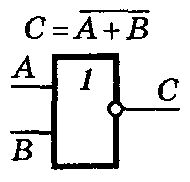

Логическое сложение с инверсией или «стрелка Пирса», 2ИЛИ-НЕ:

-

Логическое умножение с инверсией или «штрих Шеффера», 2И-НЕ.

-

Исключающее ИЛИ:

.

.

Функции 2И-НЕ и 2ИЛИ-НЕ одни из самых распространенных в интегральной схемотехнике.

В

схемах, реализующих логические функции

значения логической единицы ( )

и логического нуля (

)

и логического нуля ( )

представлены разными величинами

напряжений.

)

представлены разными величинами

напряжений.

Разность

называется логическим

перепадом.

Естественно, что логический перепад

должен быть достаточно большим, чтобы

единицы и нули четко отличались друг

от друга и случайные помехи не превращали

один уровень в другой.

называется логическим

перепадом.

Естественно, что логический перепад

должен быть достаточно большим, чтобы

единицы и нули четко отличались друг

от друга и случайные помехи не превращали

один уровень в другой.

Рассмотрим схемотехнику логических элементов.

-

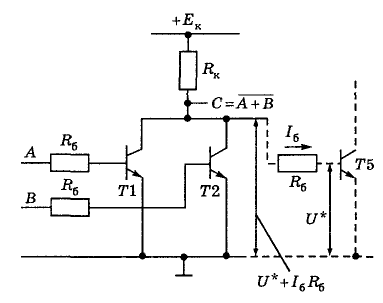

Резисторно-транзисторная логика (РТЛ) представляет собой параллельное соединение обычных транзисторных ключей с резисторами в базовых цепях.

Нетрудно убедится, что данная схема выполняет функцию 2ИЛИ-НЕ.

Резисторы в базовой цепи добавлены для снижения захвата тока. Схемы РТЛ использовались на первом этапе развития микроэлектроники. Однако, из-за наличия тех же резисторов, занимающих большую площадь на кристалле, оказались не перспективными для использования в ИМС с большой степенью интеграции. Кроме того РТЛ схемы также имели низкое быстродействие и низкую помехоустойчивость.

-

Диодно-транзисторная логика (ДТЛ). В ЛЭ типа РТЛ и РЕТЛ в качестве элементов связи использовались резисторы, в ТЛНС логике связь между ЛЭ была непосредственной. Первый этап в развитии элементной базы микроэлектроники завершился созданием ДТЛ схем логических элементов, где в качестве элементов связи использовались диоды.

Рассмотрим схему ДТЛ с двумя входом и простым инвертором.

Приведенный

ЛЭ содержит инвертор на транзисторе,

диоды связи

,

,

и диоды

и диоды

и

и

для увеличения входного порогового

напряжения инвертора. Резистор

для увеличения входного порогового

напряжения инвертора. Резистор

создает контур для протекания токов

создает контур для протекания токов

рассасывания носителей заряда при

переключении ЛЭ из режима логического

нуля в режим логической единицы.

рассасывания носителей заряда при

переключении ЛЭ из режима логического

нуля в режим логической единицы.

Представленная

схема реализует логическую функцию

2И-НЕ. Передаточная функция построена

для случая, когда

.

.

Прокомментируем

передаточную характеристику. Пусть на

входе

напряжение равно нулю. В этом случае

диод

напряжение равно нулю. В этом случае

диод

открыт и ток источника питания через

резистор

открыт и ток источника питания через

резистор

протекает во входную цепь, соответственно

транзистор инвертора заперт и напряжение

на выходе равно

протекает во входную цепь, соответственно

транзистор инвертора заперт и напряжение

на выходе равно

.

Повышаем входное напряжение до уровня

.

Повышаем входное напряжение до уровня

и напряжение на резисторе

и напряжение на резисторе

достигает уровня

достигает уровня

и транзистор переходит в активный режим

работы. Повышение входного напряжения

до уровня

и транзистор переходит в активный режим

работы. Повышение входного напряжения

до уровня

приводит транзистор в насыщенное

состояние.

приводит транзистор в насыщенное

состояние.

Помехоустойчивость ДТЛ ЛЭ определяется следующим образом:

К

преимуществам ДТЛ можно отнести более

высокую помехоустойчивость по сравнению

со схемами РТЛ и ТЛНС (для ТЛНС

,

для РТЛ

,

для РТЛ

).

Однако из-за наличия резисторов схема

по-прежнему занимает большую площадь

на кристалле, кроме того, требования к

резистору

).

Однако из-за наличия резисторов схема

по-прежнему занимает большую площадь

на кристалле, кроме того, требования к

резистору

весьма противоречивы: так при открытом

и насыщенном транзисторе через этот

резистор протекает дополнительный,

можно даже сказать, паразитный ток,

который обуславливает и потери в нем,

и здесь выгодно увеличить это сопротивление.

С другой стороны, при запирании

транзисторного ключа через этот резистор

протекает ток, обусловленный процессами

рассасывания зарядов в базе, и тут

выгодно уменьшить это сопротивление.

весьма противоречивы: так при открытом

и насыщенном транзисторе через этот

резистор протекает дополнительный,

можно даже сказать, паразитный ток,

который обуславливает и потери в нем,

и здесь выгодно увеличить это сопротивление.

С другой стороны, при запирании

транзисторного ключа через этот резистор

протекает ток, обусловленный процессами

рассасывания зарядов в базе, и тут

выгодно уменьшить это сопротивление.

Основные недостатки ДТЛ схемы решены в более совершенном варианте ЛЭ – ТТЛ схемах ЛЭ, которые применяются до сих пор в современных микросхемах.