Экзамен микроэлектроника / Лекции / 16а. Логические элементы типа БиКМОП

.docxЛогические элементы типа БиКМОП

КМОП схемотехника наиболее удобна для создания цифровых БИС сверхвысокой степени интеграции из-за небольшого уровня потребляемой мощности и высокой плотности упаковки. Однако, с ростом сложности цифровых БИС возникает проблема управления большими емкостями, образованными емкостями межсоединений большой протяженности и емкостями управляемых нагрузок на кристалле. Поскольку максимальный выходной ток МОП транзистора ограничен геометрическими размерами канала, то скорость перезаряда емкости нагрузки ограничена. При соответствующей ширине канала МОП транзисторы способны коммутировать большие токи. Однако при этом увеличивается входная емкость (емкость затвор-канал), что ограничивает быстродействие. Кроме того, МОП транзисторы вследствие невысокой крутизны усиления и низкой выходной проводимости малоэффективны при создании схем согласований, например КМОП-ЭСЛ и других.

С другой стороны, биполярные транзисторы вследствие экспоненциальной зависимости тока коллектора от напряжения на входе и высоких коэффициентов усиления дают возможность реализации более быстрых цифровых схем чем МОП транзисторы, даже при больших емкостях нагрузок.

Скоростью перезаряда емкости нагрузки можно управлять изменением тока коллектора. При этом, входная емкость биполярного транзистора зависит от его тока, в то время как у МОП транзистора остается постоянной.

Широкое применение СБИС на биполярных транзисторах сдерживается большим уровнем потребляемой мощности. В результате этого, сложилось направление элементной базы, в котором используются достоинства как БТ, так и МОП (БиКМОП).

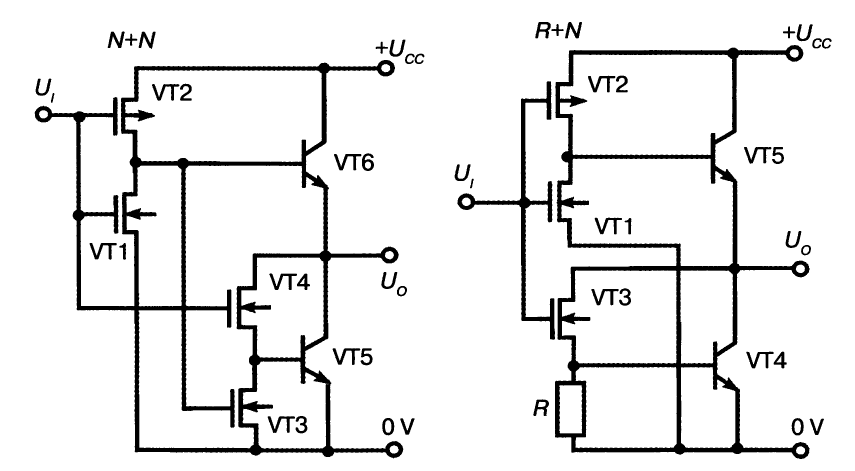

На

рисунке изображена схема простейшего

инвертора, построенного на основе

биполярных и МОП транзисторов. Схема

представляет собой двухкаскадный ЛЭ,

где логическая функция реализована

входным КМОП ключом

,

а разряд и заряд нагрузочной емкости

обеспечивает каскод на биполярных

транзисторах

,

а разряд и заряд нагрузочной емкости

обеспечивает каскод на биполярных

транзисторах

.

.

Однако данная схема не получила широкого распространения из-за большой разницы в характеристиках транзисторов p-n-p и n-p-n типов. Эта разница сказывается на различии времен фронта и среза. Кроме того, схема является технологически сложной вследствие наличия в ней транзисторов четырех типов и необходимости управления большим комплексом технологических параметров.

Более эффективна и получила широкое распространение схема с n-p-n транзисторами:

Транзистор VT4 предназначен для заряда емкости и формирования напряжения логической единицы. Транзистор VT3 предназначен для разряда емкости и формирования напряжения логического нуля.

Элементы Z1 и Z2 введены для рассасывания зарядов из баз биполярных транзисторов.

В качестве таких элементов могут использоваться резисторы (структура R+R типа), N-МОП транзисторы (N+N тип) или и то и другое (R+N) тип.

|

|

|

В статическом состоянии в структуре R+R токи через МОП транзисторы, и, соответственно резисторы малы, поэтому биполярные транзисторы VT3 и VT4 закрыты. Если на входе напряжение низкого логического уровня, то р-канальный транзистор VT2 открыт. На выходе инвертора будет высокий логический уровень, и конденсатор нагрузки будет заряжен. Если на вход подать высокий логический уровень, откроется n-канальный транзистор VT1 и начнется разряд емкости через резистор R1 и эмиттерный переход биполярного транзистора VT3. Часть разрядного тока откроет этот транзистор и будет происходить перезарядка емкости нагрузки.

Аналогично происходит процесс переключения при изменении входного напряжения от высокого логического уровня к низкому.

Рассмотрим работу схемы на примере структуры N+N.

При низком уровне входного напряжения N-МОП транзисторы VT1 и VT4 закрыты, VT3 открыт и удерживает в закрытом состоянии транзистор VT5. При этом открытый транзистор P-МОП транзистор VT2 удерживает в открытом состоянии выходной транзистор VT6, который формирует на выходе напряжение логической единицы:

.

.

При высоком уровне на входе схемы МОП-транзисторы VT2 и VT3 закрыты, вследствие чего выходной транзистор VT6 закрыт. Открытый N-МОП транзистор VT4 обеспечивает открытое состояние выходного транзистора VT5. При этом на выходе устанавливается низкое напряжение логического нуля:

.

.