Экзамен микроэлектроника / Лекции / 4. Способы повышения быстродействия ключей

.docxСпособы повышения быстродействия транзисторных ключей

Рассмотрим ряд схемотехнических решений, позволяющих улучшить быстродействие транзисторного ключа.

-

Включение ускоряющей емкости в цепь базы.

Как было показано ранее – время нарастания фронта зависит от тока базы в момент отпирания ключа. Включение ускоряющей цепочки позволяет сформировать скачок тока базы при подаче отпирающего импульса, который обеспечивает ускоренный перезаряд емкости эмиттерного перехода и накопление заряда неосновных носителей в базе.

Величина емкости выбирается так, чтобы ток базы к моменту подачи запирающего импульса успел уменьшиться до уровня, соответствующего границе насыщения с минимально необходимым запасом.

Заметим, что создаваемое на емкости отрицательное напряжение, как результат протекания отпирающего тока, способствует также и более быстрому выключению транзистора.

-

Включение дополнительного сопротивления в цепь эмиттер-база.

Дополнительное

сопротивление во входной цепи создает

контур для тока на этапе рассасывания

избыточного заряда в базе, увеличивая,

таким образом, скорость выключения ТК.

Однако при использовании этого

сопротивления напряжение на базе

уменьшается с коэффициентом деления

.

Поэтому этот способ требует повышения

напряжения генератора чтобы обеспечить

режим насыщения.

.

Поэтому этот способ требует повышения

напряжения генератора чтобы обеспечить

режим насыщения.

-

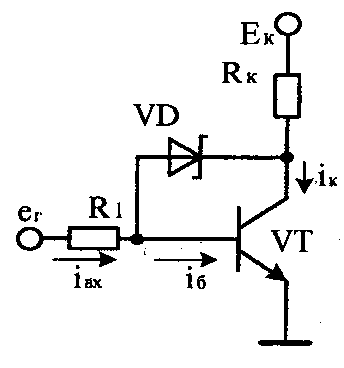

Использование нелинейной отрицательной обратной связи. Транзистор Шоттки.

В схеме на рисунке между базой и коллектором БТ включен диод Шоттки, роль которого заключается в следующем. Обладая односторонней проводимостью, этот диод открывается при небольшом прямом напряжении между анодом и катодом, которое для этого типа диода составляет 0,3-0,4В.

В результате отпирания диода создается цепь отрицательной обратной связи, резко уменьшающей коэффициент усиления транзистора по входному току. Это, в свою очередь, уменьшает величину накопленного заряда в базе и время рассасывания. Быстродействие транзисторного ключа повышается.

Очень часто многие быстродействующие транзисторы технологически изготавливают с диодом Шоттки уже на кристалле. Такие транзисторы называют транзисторами Шоттки.

-

Использование транзисторного переключателя тока.

Структурно

схема напоминает дифференциальный

усилитель, в эмиттерную цепь которого

включен источник тока

.

Параметры транзисторов и резисторов

предполагаются одинаковыми. На один

вход ключа подается управляющий сигнал

.

Параметры транзисторов и резисторов

предполагаются одинаковыми. На один

вход ключа подается управляющий сигнал

,

принимающий два значения: низкое

,

принимающий два значения: низкое

и высокое

и высокое

.

На второй вход подается постоянное

опорное напряжение величиной

.

На второй вход подается постоянное

опорное напряжение величиной

,

что позволяет при низком уровне входного

сигнала обеспечить запирание транзистора

,

что позволяет при низком уровне входного

сигнала обеспечить запирание транзистора

и направить весь ток источника в

коллекторную цепь

и направить весь ток источника в

коллекторную цепь

.

.

Потенциалы

коллекторов соответственно равны:

.

.

Повышение

уровня входного сигнала до величины

приводит к отпиранию транзистора

приводит к отпиранию транзистора

и запиранию транзистора

и запиранию транзистора

.

Теперь уже весь ток

.

Теперь уже весь ток

переходит в коллекторную цепь

переходит в коллекторную цепь

,

снижая потенциал его коллектора до

величины

,

снижая потенциал его коллектора до

величины

.

.

Повышенное быстродействие схемы объясняется следующими факторами:

- отсутствие насыщения;

-

возможностью использования малых

значений

что способствует быстрой перезарядке

емкости коллекторного перехода;

что способствует быстрой перезарядке

емкости коллекторного перехода;

-

постоянная времени процесса включения

и выключения здесь не

,

а

,

а

.

.

Элементы цифровой логики на биполярных транзисторах

В этом разделе будут рассмотрена схемотехника логических элементов, их классификация, характеристики и параметры. Рассмотренный ранее ключ на БТ представляет собой простейший логический элемент, выполняющий функцию логического отрицания, или инверсии. Поэтому в дальнейшем будем именовать его, как простой инвертор.

Большая часть теории в этом разделе будет основой для выполнения курсового проекта по данному курсу.

Построение передаточной характеристики простого инвертора по характерным точкам.

Рассмотрим

простой инвертор, работающий на

коллекторную нагрузку

.

.

Напряжение

на входе ЛЭ может меняться от 0 до

на входе ЛЭ может меняться от 0 до

.

Передаточная характеристика имеет

наклонный участок в окрестности точки

.

Передаточная характеристика имеет

наклонный участок в окрестности точки

.

Наклон этого участка определяется

малосигнальным коэффициентом усиления

БТ с нагрузкой

.

Наклон этого участка определяется

малосигнальным коэффициентом усиления

БТ с нагрузкой

:

:

В

стационарном состоянии ЛЭ реализует

один из двух крайних режимов: логическая

единица,

и логический ноль,

и логический ноль,

.

В нашем случае

.

В нашем случае

,

,

.

.

Поэтому

в цифровых ЛЭ достаточно аппроксимации

передаточной характеристики трех

участков прямых, соединяющих точки с

координатами

.

.

При

подключении дополнительной нагрузки

(см. рис.) напряжение логической единицы

снизится до уровня

(см. рис.) напряжение логической единицы

снизится до уровня

.

.

Явление «захвата» тока

Захват тока имеет место при параллельном соединении базовых цепей нескольких ЛЭ к выходу логического элемента.

Захват тока представляет собой неравномерное распределение токов в базах транзисторов , подключенных к общему ЛЭ. Это явление имеет место при существенных разбросах токов баз транзисторов.

Предположим

выход ЛЭ, к которому подключены транзисторы

находится в состоянии логической

единицы. Напряжение

находится в состоянии логической

единицы. Напряжение

приводит транзисторы

приводит транзисторы

в насыщенное состояние. Значения

в насыщенное состояние. Значения

для транзисторов примем равными

соответственно

для транзисторов примем равными

соответственно

.

Разброс значений напряжений

.

Разброс значений напряжений

является основной причиной захвата

тока.

является основной причиной захвата

тока.

Для

расчетов токов баз транзисторов

воспользуемся эквивалентной схемой,

где напряжения

представим в виде эквивалентных ЭДС,

замещающими база-эмиттерные цепи

транзисторов

представим в виде эквивалентных ЭДС,

замещающими база-эмиттерные цепи

транзисторов

.

Внутренние сопротивления переходов

представим в виде резисторов

.

Внутренние сопротивления переходов

представим в виде резисторов

.

.

Тогда токи баз буду равны соответственно:

;

;

…

Из

полученных соотношений видно, что

разница токов

зависит не только от разброса

зависит не только от разброса

,

но и от разброса сопротивлений баз.

,

но и от разброса сопротивлений баз.

Для

понимания насколько важным является

захват тока приведем пример:

,

,

,

,

Сопротивления баз примем равными 20Ом.

Из формул выше находим:

Сопротивления баз примем равными 20Ом.

Из формул выше находим:

Из

приведенного примера видно, что транзистор

захватил 57% тока

захватил 57% тока

,

а на долю

,

а на долю

пришлось всего 10% того же тока.

пришлось всего 10% того же тока.

Следствием

захвата тока могут являться нарушения

работоспособности аппаратуры из-за

снижения запасов от помех и неправильных

режимов ( ).

).

Некоторое

подавление захвата тока возможно при

последовательном включении внешних

резисторов в базовые цепи. В этом случае

величина

увеличивается,

что уменьшает влияние разбросов

увеличивается,

что уменьшает влияние разбросов

и

и

и повышает помехоустойчивость цепи.

и повышает помехоустойчивость цепи.