- •Основы

- •История развития

- •История развития

- •История развития

- •История развития

- •История развития

- •История развития

- •История развития

- •История развития

- •История развития

- •История развития

- •История развития

- •Архитектура

- •Архитектура

- •Архитектура

- •Архитектура

- •Архитектура

- •Архитектура

- •Архитектура

- •Архитектура

- •Архитектура

- •Архитектура

- •Архитектура

- •Архитектура

- •Структура MCS51

- •Структура MCS51

- •Структура MCS51

Архитектура

микроконтроллера

RISC архитектура (reduced instruction set computing)

архитектура процессора, в которой быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. Первые RISCпроцессоры даже не имели инструкций умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание инструкций между несколькими исполнительными блоками).

21

21

Архитектура

микроконтроллера

VLIW архитектура (very long instruction word)

Архитектура процессоров с несколькими вычислительными устройствами. Характеризуется тем, что одна инструкция процессора содержит несколько операций, которые должны выполняться параллельно. Фактически это «видимое программисту» микропрограммное управление, когда машинный код представляет собой лишь немного свёрнутый микрокод для непосредственного управления аппаратурой.

В суперскалярных процессорах также есть несколько вычислительных модулей, но задача распределения между ними работы решается аппаратно. Это сильно усложняет устройство процессора, и может быть чревато ошибками. В процессорах VLIW задача распределения решается во время компиляции и в инструкциях явно указано, какое вычислительное устройство должно выполнять какую команду.

22

22

Архитектура

микроконтроллера

Гарвардская архитектура — архитектура ЭВМ, отличительными признаками которой являются:

1.Хранилище инструкций и хранилище данных представляют собой разные физические устройства.

2.Канал инструкций и канал данных также физически разделены.

Гарвардская архитектура отличается от архитектуры фон Неймана тем, что программный код и данные хранятся в разной памяти. В такой архитектуре невозможны многие методы программирования (например, программа не может во время выполнения менять свой код; невозможно динамически перераспределять память между программным кодом и данными); зато гарвардская архитектура позволяет более эффективно выполнять работу в случае ограниченных ресурсов, поэтому она часто применяется во встраиваемых системах.

23

23

Архитектура

микроконтроллера

Гарвардская архитектура

Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий:

•выборку двух операндов,

•выбор инструкции и её выполнение,

•сохранение результата.

Идея, заключается в физическом разделении линий передачи команд и данных. В первом компьютере Эйкена «Марк I» для хранения инструкций использовалась перфорированная лента, а для работы с данными — электромеханические регистры. Это позволяло одновременно пересылать и обрабатывать команды и данные, благодаря чему значительно повышалось общее быстродействие компьютера.

24

24

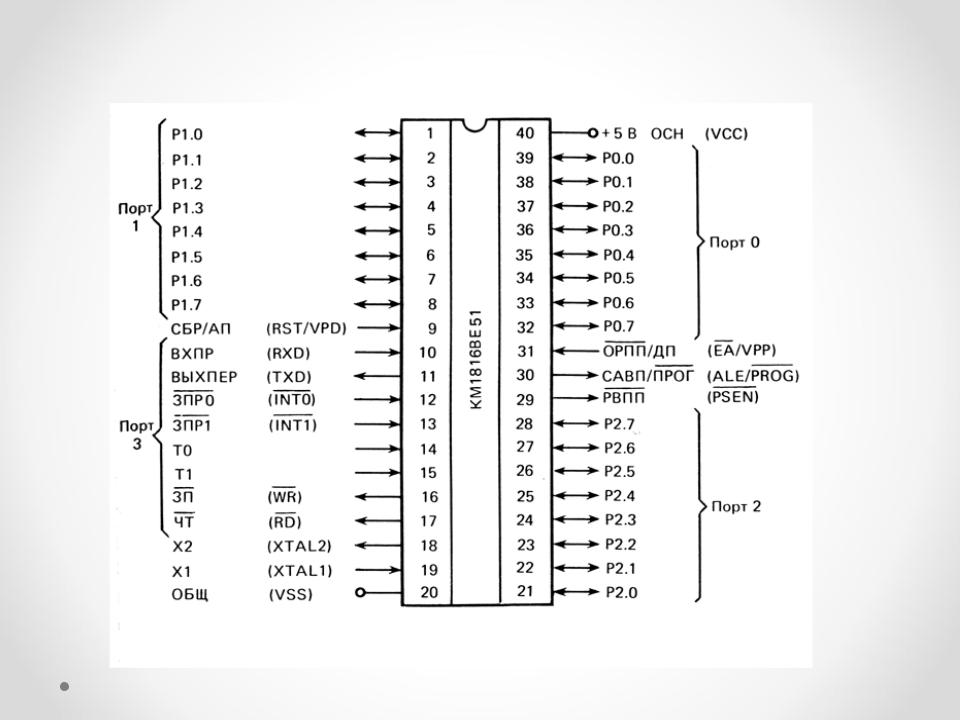

Структура MCS51

Микроконтроллер выполнен на основе высокоуровневой nМОП технологии и выпускается в корпусе БИС, имеющем 40 внешних выводов. Для работы МК51 требуется один источник электропитания +5 В. Через четыре программируемых восьмиразрядных порта ввода/вывода МК51 взаимодействует со средой в стандарте ТТЛ схем с тремя состояниями выхода (нагрузочная способность выходов – 2 мА).

Корпус МК51 имеет два вывода для подключения кварцевого резонатора, четыре вывода для сигналов, управляющих режимом работы МК, и восемь линий порта 3, которые могут быть запрограммированы пользователем на выполнение специализированных (альтернативных) функций обмена информацией со средой.

25

25

Структура MCS51

26

26

Структура MCS51

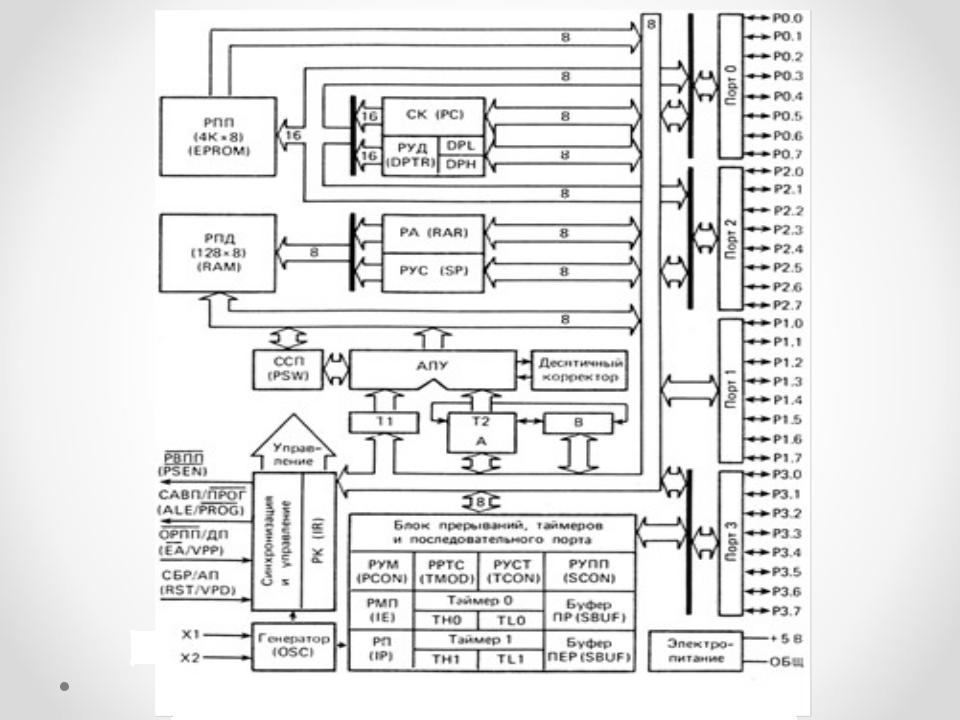

Основу структурной схемы МК51 образует внутренняя двунаправленная 8битная шина, которая связывает между собой все основные узлы и устройства: резидентную память, АЛУ, блок регистров специальных функций, устройство управления и порты ввода/вывода.

27

27

28

28