Лабораторная работа №2 Графический режим.

В этой лабораторной работе представлены основы управления пикселами: чтение и установка значения пиксела в видеобуфере, инициализация области видеобуфера по заданному образцу.

Программирование битовых плоскостей

Между программированием видеоадаптеров, видеопамять которых организована как параллельные битовые плоскости (адаптеры EGA и VGA). и остальных видеоподсистем фирмы IBM имеется существенное различие. В адаптерах CGA, MCGA и монохромных адаптерах программа имеет доступ к пикселам, прямо считывая и записывая байты в видеопамять. В графических режимах адаптеров EGA и VGA программа не имеет непосредственного доступа к видеопамяти. Вместо прямого доступа для управления содержимым битовых плоскостей в этих адаптерах применяются специальные схемы.

Битовые плоскости графического режима адаптеров EGA и VGA адресуются параллельно. Другими словами, когда процессор выполняет операции чтения или записи содержимого видеобуфера по конкретному адресу, этот адрес относится не к одному, а к четырем байтам, каждый из которых располагается в своей битовой плоскости.

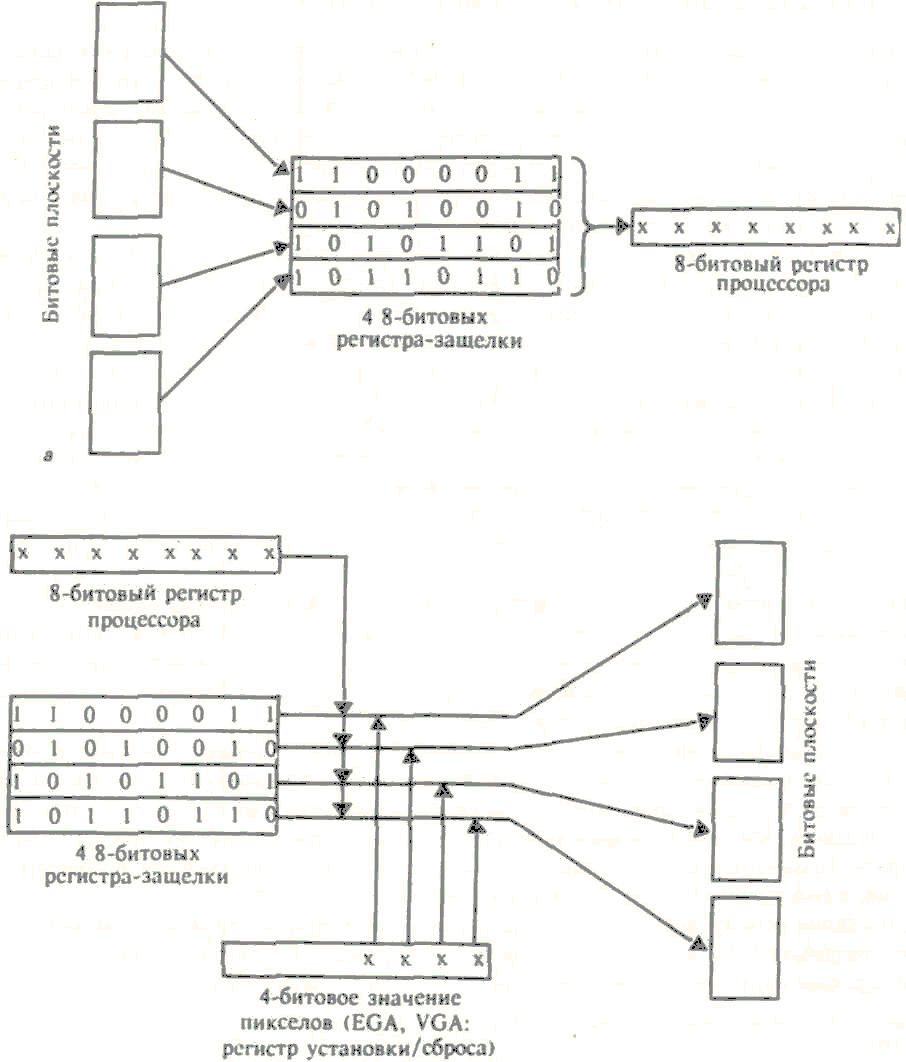

Когда, обращаясь к видеобуферу, процессор 80х86 выполняет операцию чтения по адресу видеобуфера, из него на самом деле пересылается не один, а четыре байта данных. Однако данные пересылаются не прямо в процессор, а в четыре 8-битовых регистра-защелки. Каждый из этих регистров соответствует своей битовой плоскости. Таким образом, выполнение процессором 8-битовой команды чтения по адресу видеобуфера влечет за собой пересылку из видеобуфера в эти регистры 4 байтов (32 битов) (рис. 1,а). Команды типа MOV reg.mem и LODS или СМР reg.mem заставляют процессор выполнять команды чтения, а это приводит к обновлению содержимого регистров-.защелок.

Аналогично команды типа MOV mem,reg и STOS или XOR mem,reg заставляют процессор выполнить команды записи; в этом случае все четыре битовые плоскости могут изменяться параллельно с использованием комбинации данных, состоящей из содержимого регистров-защелок, байт данных пересылаемого процессором и предопределенного значения пиксела, хранящегося в регистре графического контроллера (рис. 1).

Некоторые команды процессора требуют и чтения, и записи. (Процессор считывает значение из памяти, выполняет над ним действие и записывает результат снова в память.) Типичным примером является команда MOVS, но команды OR mem.reg и AND mem,reg или XOR mem,reg тоже вызывают чтетение, и запись. Когда такая команда обращается по входящему в адресное пространство видеобуфера адресу, содержимое регистров-защелок обновляется во время выполнения процессором операции чтения, а содержимое битовых плоскостей — операции записи.

Использование регистров-защелок для параллельной обработки содержимого битовых плоскостей позволяет разработать на первый взгляд простые программы. Рассмотрим, например, следующий фрагмент программы, копирующий второй байт пикселов из видеобуфера в первый.

mov ax.VideoBufrerSegment

mov ds,ax

mov es,ax

mov si.,1 ' ; DS:SI второй байт

mov di,0 ; ES;DI первый байт

movsb

Этот фрагмент кажется простым. Команда MOVSB копирует один байт из ячейки памяти по адресу DS:SI в ячейку с адресом ES:DI. В действительности в графических режимах, использующих •битовые плоскости, в видеобуфере адаптеров EGA и VGA происходят другие события.

На самом деле по команде MOVSB процессор выполняет операцию чтения, а затем - операцию записи. Поскольку процессор производит чтение из видеобуфера, в каждый регистр-защелку записывается по байту из соответствующей битовой плоскости. Затем, так как запись тоже производится в видеобуфер, содержимое регистров-защелок переписывается в соответствующие битовые плоскости по указанному адресу. Таким образом, в результате выполнения команды MOVSB вместо одного байта пересылаются четыре.

Рис. 1. Последовательность обработки данных в-графическом режиме адаптеров EGA и VGA во время выполнения процессором операций чтения (а) и записи (б)

Примечание. Смысл этого примера намного глубже, чем кажется на первый взгляд. Рассмотрим, что получится, если заменить команду MOVSB на MOVSW. Без битовых плоскостей и регистров-защелок вместо одного байта будут скопированы два. Но в адаптерах EGA и VGA будет потеряна половина значений пикселов. Причина заключается в том, что при выполнении команды MOVSW выполняются сначала две 8-битовые команды чтения, а за ними — две 8-битовые операции записи. При этом вторая операция записи обновляет содержимое регистров-защелок еще до того, как байты, помеченные первой командой чтения, будут записаны в битовые плоскости. В силу этого при доступе к видеобуферам адаптеров EGA и VGA надо пользоваться осторожно 16-битовыми командами процессора 80х86. Команды типа OR mem.reg, AND mem,reg и XOR mem.reg с .16-битовыми данными действуют неверно.

Регисты-защелки улучшают эффективность пересылки данных в видеобуфер и из него, но при пересылке данных между регистрами-защелками и процессором возникают определенные сложности. Сложности эти заключаются в том, что регистры-защелки содержат 32 бита, а байтовый регистр процессора всего 8 битов, поэтому во время выполнения операции чтения требуется битовое сжатие данных. При пересылке же данных из регистра процессора в битовые плоскости 8-битовое содержимое регистра процессора и всех четырех регистров-защелок можно комбинировать множеством способов. Ключом к программированию адаптеров EGA и VGA в графическом режиме является преобразование данных с привлечением как процессора, так и регистров-защелок.

Адаптеры EGA и VGA

Графический контроллер адаптеров EGA и VGA управляет всеми пересылками данных между процессором, регистрами-защелками и видеобуфером. Графический контроллер адаптера EGA состоит из двух БИС. Графический контроллер адаптера VGA является частью микросхемы "графическая видеоматрица" (Video Graphics Array). Графический контроллер имеет 9 доступных через порт 3CFH регистров, адресация которых проводится через порт ЗСЕН. Содержимое регистров определяет способ, которым во время выполнения процессором операций чтения и записи графический контроллер обрабатывает содержимое регистров-защелок.

Графический контроллер позволяет манипулировать содержимым регистров-защелок (т.е. значениями пикселов) в двух направлениях. Часть операций в качестве операнда имеют байт, т.е. они воздействуют отдельно на каждый регистр.

Другие операции в качестве операнда имеют пиксел, т.е. содержимое регистров-защелок рассматривается как набор восьми значений пикселов; такие операции воздействуют на значение каждого пиксела в отдельности.

Над содержимым регистров-защелок графический контроллер может производить три различные байтовые операции. Он может скопировать содержимое регистров-защелок в видеобуфер и наоборот; действие это происходит неявно при выполнении операции чтения или записи. Во время выполнения процессором операции чтения контроллер может передать содержимое одного из регистров-защелок регистр процессора. В операции записи процессора контроллер может объединить байт из регистра процессора с байтами из любого или всех регистров-защелок.

Кроме того, графический контроллер обрабатывает данные, содержащиеся в регистрах-защелках, пиксел за пикселом. В операции чтения процессора графический контроллер может сравнить каждое содержащееся в регистре-защелке значение пиксела с предопределенным значением и возвратить результат сравнения в регистр процессора

В операции записи процессора контроллер может объединить 4-битовое значение процессора с любым или со всеми значениями пикселов, содержащимися в регистрах-защелках; использовать передаваемое процессором 8-битовое значение как маску, указывающую, какое из восьми значений пикселов в регистрах-защелках переписать обратно в битовые матрицы; объединить значения пикселов, содержащиеся в регистрах-защелках, с предопределенным 4-битовым значением.

Использование одного из двух видов операций (с байтами или с пикселами) определяется выбором режима записи или режима чтения. Каждый режим записи формирует определенную последовательность байтовых или пиксельных операций, производящихся при выполнении процессором операции записи. Аналогично каждый режим чтения определяет производимую при выполнении процессором операции чтения последовательность действий. В адаптере EGAимеются :три режима записи и два режима чтения, а адаптер VGAв дополнении к этим пяти имеет еще одиндополннтельный режим записи.

Пока вы не ознакомитесь с каждым режимом чтения и записи графического контроллера, их смысл может показаться несколько неясным. Однако в определенных ситуациях каждый режим имеет свои практические преимущества.

Регистр режима графического контроллера (05Н) содержит два битовых поля, значения которых определяют упомянутые режимы чтения и записи. Например, для задания режима чтения 1 нужно установить бит 3 регистра режима в 1, а для задания режима записи 2 в биты 0 - 1 этого же регистра надо записать значение 2 (10В) (листинг 1).

mov ax,0105h АН := 1(значемие для регистра 5Н)

бит 3 := 0 (режим чтения 0)

биты 0-1 := 1 (режим записи 1) AL := номер регистра

mov dx,3CEh DL := порт графического контроллера

out dx, ax

Листинг 1. Задание режимов чтения и записи графического контроллера. В этом примере для 16-цветного режима 640х350 задается режим чтения 0 и режим записи 1

Примечание. В табл..1 приведены значения, устанавливаемые по умолчанию системой BIOS для регистра режима и других регистров графического контроллера. Целесообразно восстанавливать значения регистров графического контроллера, принимаемые по умолчанию, после его изменения вашей программой.

Таблица 1. Значения регистров графического контроллера адаптеров EGA и VGA, принимаемые по умолчанию системой BIOS

|

Регистр |

Функция |

Значение |

|

0 |

Установка/Сброс |

0 |

|

1 |

Разрешение установки/сброса |

0 |

|

2 |

Сравнение цвета |

0 |

|

3 |

Циклический сдвиг данных |

0 |

|

4 |

Выбор читаемой карты |

0 |

|

5 |

Выбор режима |

Биты 0-3 всегда равны 0 |

|

6 |

Смешанный вывод |

(зависит от видеорежима) |

|

7 |

Безразличие цвета |

0FH (16-цветные режимы) 01Н (2-цветный режим 640х480)

|

|

8 |

Битовая маска |

FFH |