- •8. Процессор

- •8.1. Базовые концепции

- •Ir← [[pc]]

- •8.2. Пересылка данных между регистрами

- •8.3. Выполнение арифметической или логической операции

- •8.4. Выборка слова из памяти

- •8.5. Сохранение слова в памяти

- •9. Конвейерная обработка команд

- •9.1. Базовые концепции

- •9.1.1. Роль кэш-памяти

- •9.1.2. Производительность конвейерной обработки команд

- •9.2. Очередь команд и упреждающая выборка

- •9.3. Конвейерная обработка и система команд

- •9.3.1. Режимы адресации

- •9.3.2. Коды условий

- •9.4. Тракты данных и управление

9.3.2. Коды условий

Во многих процессорах, включая описанные в разделе 4, флаги условий хранятся в регистре состояния процессора. Они устанавливаются и очищаются многими командами. В результате их можно проверить в последующих командах условного перехода для изменения потока выполнения программы. Оптимизирующий компилятор конвейерного процессора старается реорганизовать команды программы таким образом, чтобы по возможности избегать остановов конвейера из-за переходов или зависимостей между данными последовательных команд. Компилятор должен гарантировать, что реорганизация команд не приведет к изменению результатов вычислений. Зависимости, связанные с использованием флагов условий, мешают компилятору реорганизовывать команды.

В качестве примера рассмотрим последовательность команд, приведенную на рис. 9.7, а. Предположим, что команды Compare и Branch = 0 выполняются так, как показано на рис. 9.4. Решение о переходе принимается не на шаге D2 а на шаге Е2, поскольку для него нужны результаты обработки команды Compare. Время, необходимое команде перехода, можно сократить, поменяв местами команды Add и Compare (рис. 9.7, 6). В результате во время декодирования команды Branch уже будут доступны результаты выполнения команды сравнения, что позволит сразу принять решение о переходе без предсказаний. Важный момент заключается в том, что команды сложения и сравнения можно поменять местами только в том случае, если команда сложения не воздействует на флаги условий.

Add R1,R2

Compare R3,R4

Branch = 0

a

Compare R3,R4

Add R1,R2

Branch = 0

б

Рис. 9.7. Изменение порядка следования команд: фрагмент программы (а);

команды после переупорядочения (б)

Проанализировав пример, можно сделать два важных вывода относительно обработки флагов условий. Во-первых, для обеспечения гибкой реорганизации команд флаги условий должны изменяться как можно меньшим количеством команд. Во-вторых, нужно, чтобы компилятор указывал, в каких командах флаги условий модифицируются, а в каких нет. Системы команд, разрабатываемые с учетом конвейеризации, обычно отвечают этим требованиям. Реорганизация команд, представленная на рис. 9.7, б, может быть выполнена лишь при условии, что флаги обрабатываются только в том случае, когда это явно указано в коде операции. Такую возможность поддерживают архитектуры SPARC и ARM.

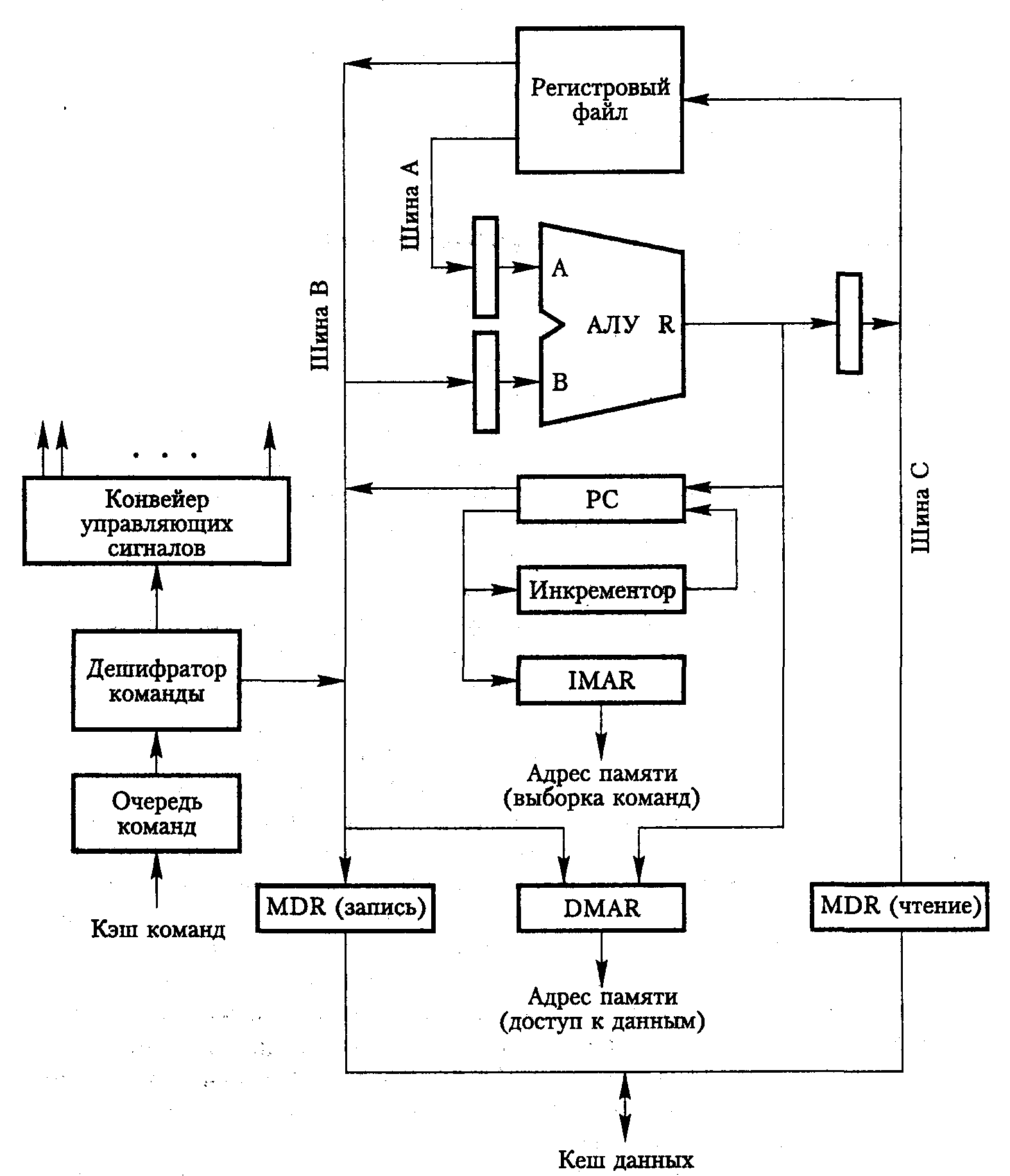

9.4. Тракты данных и управление

С общими принципами организации тракта данных процессора мы познакомились в разделе 8. Давайте рассмотрим трех-шинную структуру, но приспособим эту структуру к конвейерному выполнению команд, как показано на рис. 9.8. На рисунке вы видите структуру для 4-ступенчатого конвейера. Обращения к кэшу данных могут выполняться на ступени E или на более поздних ступенях, что зависит от режима адресации и особенностей процессора. Рассмотрим важнейшие изменения, внесенные в схему.

1. Отдельные кэши команд и данных, которые имеют отдельные соединения с процессором для передачи адреса и данных. В этом случае используются две версии регистра MAR: IMAR обеспечивает доступ к кэшу команд, a DMAR — к кэшу данных.

2. Регистр PC соединен непосредственно с регистром IMAR, так что его содержимое может быть переслано в IMAR одновременно с выполнением другой операции в АЛУ.

3. Для использования косвенной регистровой и индексной адресации адрес данных, хранящийся в регистре DMAR, можно получить прямо из регистрового файла или из АЛУ.

4. Операциям чтения и записи выделены раздельные регистры MDR. В ходе загрузки и сохранения возможен непосредственный обмен данными между регистрами и регистровым файлом без пропуска через АЛУ.

5. На входах и выходах АЛУ имеются буферные регистры SRC1, SRC2 и RSLT. Соединения для продвижения данных на рис. 9.8 не показаны.

6. Регистр команд заменен очередью команд, загружаемых из кэша.

7. Выход дешифратора команды соединен с конвейером управляющих сигналов. О необходимости буферизации управляющих сигналов и пересылки их от одной ступени к другой вместе с командами рассказывалось в разделе 9.1. Этот конвейер сохраняет управляющие сигналы в буферах В2 и ВЗ (рис. 9.2, а).

Рис. 9.8. Тракт данных, модифицированный для конвейерного выполнения с промежуточными буферами на входе и выходе АЛУ

Процессор (рис. 9.8), может независимо выполнять следующие операции:

считывать команды из кэша команд;

производить приращение значений регистра PC;

декодировать команды;

считывать из кэша и записывать в кэш данные;

считывать содержимое двух регистров из регистрового файла;

осуществлять запись в один регистр регистрового файла;

выполнять операции АЛУ.

Поскольку в перечисленных операциях не задействованы общие ресурсы, их можно выполнять одновременно в любых сочетаниях. Это обеспечивает гибкость, необходимую для реализации 4-ступенчатого конвейера. В качестве примера возьмем последовательность из четырех команд: I1, I2, I3, и I4. Как показано на рис. 9.2, а, на такте 4 производятся следующие действия:

запись результата команды I1 в регистровый файл;

чтение операндов команды I2 из регистрового файла;

декодирование команды I3;

выборка команды I4 и приращение значения регистра PC.

Выводы

В этой главе рассматривалась внутренняя организация центрального процессорного устройства компьютера. В современных машинах применяются самые разные вариации описанной здесь архитектуры. При выборе конкретного решения конструкторы стараются найти оптимальное соотношение между скоростью выполнения программ и стоимостью реализации процессора. Кроме того, учитываются особенности выбранной технологии, гибкость системы с точки зрения модификации и потребность в специальных возможностях системы команд компьютера.

Мы рассмотрели два подхода к реализации управляющего блока процессора — аппаратное управление и микропрограммное управление. Аппаратное решение выбирают в том случае, если на первом плане стоит скорость функционирования компьютера. Если же более важным критерием является гибкость реализации системы команд, то предпочтение отдают микропрограммному управлению.