Лабораторная №2

.pdfМинистерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

СИСТЕМА КОМАНД МИКРОПРОЦЕССОРОВ СЕМЕЙСТВА INTEL

MCS-51

Отчет по лабораторной работе №2 по дисциплине «ОЭВМиВС»

Студенты гр. 723-1

______ Е.М. Лысенко

______ Д.А. Софрин

18.10.2023

Принял

Преподаватель кафедры КИБЭВС

______ О.В. Пехов

10.11.2023

Томск 2023

Введение

Цель работы: Изучение принципов работы и системы команд микропроцессора на примере микропроцессоров семейства Intel mcs-51.

2

1 Теоретическая часть

Базис микропроцессора основан на логических схемах, которые спроектированы для работы с данными и выполнения вычислений. Поведение микропроцессора определяется исполняемой программой. Микропроцессор выполняет только две функции это – управление и обработка данных. Под термином «обработка» подразумевается перемещение данных и выполнение операций над ними. Термин «управление» определяет поведение аппаратных блоков процессора в определенный момент времени. Работа микропроцессора состоит из нескольких шагов: сначала из памяти извлекается команда, затем логическая схема управления ее декодирует и синхронизирует работу исполнительных схем, тем самым исполняя эту команду. Эти шаги можно назвать циклом «выборка-исполнение». Для каждой команды, выполняется один такой цикл. Команда - это слово, которое извлекается микропроцессором из памяти программ, декодируется и им исполняется, таким образом, трансформируясь из информации в действие. Так, команды осуществляют пересылку данных, их обработку, а так же управляют аппаратными средствами микропроцессора во время всей его работы. Система команд определяет не только список команд, поддерживаемых микропроцессором, но и методы адресации к данным

Система команд МП MCS - 51 включает в себя 111 команд. Большинство команд выполняются за один или два машинных цикла «выборкаисполнение», за исключением команд умножения и деления, которые выполняются за четыре машинных цикла. В качестве операндов команд микропроцессора могут использоваться биты, четырехбитные цифры (ниблы), байты и двухбайтные слова.

3

2 Задание

Вариант 5. Используя систему команд процессора 8051, составьте алгоритм и напишите программу циклического перебора значения от 0 до 99. Единицы выводить в порт P1, десятки в порт P0. Оцените период выполнения цикла. Проверьте правильность работы программы на симуляторе.

3 Вариант решения (алгоритм, код)

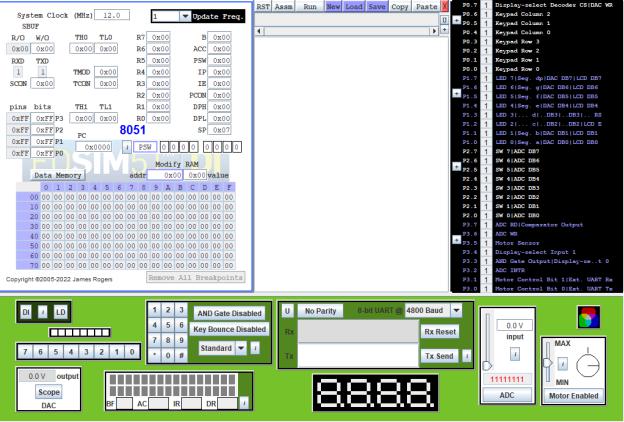

Симулятор «edsim51» предназначен для написания и отладки программ для микропроцессоров семейства intel mcs-51 (рисунок 3.1).

Рисунок 3.1 — Программа edsim51

Программирование процессора осуществляется при помощи построения программы на языке ассемблер.

4

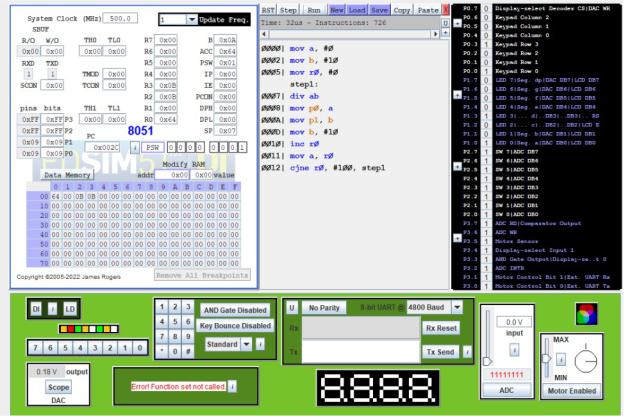

На рисунке 3.2 представлен результат работы программы и решение нашего задания.

В порте P0 мы получаем 9 единиц и в порте P1 получаем 9 десятков. R0 достигла 64 в 16-ричной системе или же 100 в десятичной. Программа работала 328us и исполнила 726 строк.

Рисунок 3.2 – Результат работы в симуляторе.

Программа:

mov a, #0 — создаёт переменную a с начальным значением 0

mov b, #10 — создаёт переменную b с начальным значением 10

mov r0, #0 — создаёт переменную r0 с начальным значением 0

step1: — начало алгоритма

div ab — производим целочисленное деление и деление с остатком a на

b

mov p0, a — выводим значение a в порт 0

5

mov p1, b — выводим значение b в порт 1

mov b, #10 — обновляем значение переменной b на 10 inc r0 — добавляем единицу переменной r0

mov a, r0 — обновляем значение переменной a на r0

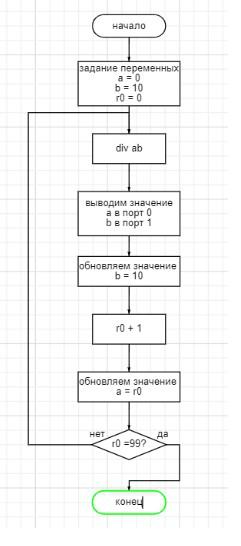

cjne r0, #100, step1 — проверяем переменную r0 на равенство 100 На рисунке 3.3 представлен алгоритм работы программы.

Рисунок 3.3 — Алгоритм программы

6

Заключение

Мы изучили принципы работы и системы команд микропроцессора на примере микропроцессоров семейства Intel mcs-51 и на базе полученных знаний составили алгоритм циклического перебора значений от 0 до 99 с выводом единиц в порт P1, а десятков в порт P0.

7