2.1. Выходные вах транзистора n- и p-типа.

Параметры, подставляемые в SPICE-модель, необходимо рассчитать по формулам:

KP = UO ox/TOX (4)

GAMMA = (TOX /ox)∙((2SiqNSUB))1/2 (5)

PHI = 2(KT/q)ln(NSUB/Ni) (6)

COX = OX/TOX (7)

СJ S = [qSiNSUB/(2 PB)]1/2 (8)

LD = (LDRAW – LEFF)/2 (9)

где q – заряд электрона (q = 1.6·10–19 K ); Si – абсолютная диэлектрическая проницаемость кремния (Si = 1.04·10–10 Ф/м); ох - абсолютная диэлектрическая проницаемость окисла ( ох = 34.554·10–12 Ф/м); NSUB – уровень легирования подложки; PB=0.8 - встроенный потенциал p-n-перехода (built–in junction potential)

Определить параметры электрических схем замещения и зафиксировать их в табл.2

Таблица 2 Параметры электрических схем замещения

Параметр |

Значение |

GAMMAP, B1/2 |

|

GAMMAN, B1/2 |

|

PHIP, В |

|

PHIN, В |

|

Cox= Eox/Tox, Ф/м2 |

|

KPP=UOP·Cox, A/B2 |

|

KPN=UON·Cox, A/B2 |

|

Полученные с помощью программы ВАХ имеют следующий вид:

Рисунок 1 - ВАХ транзистора p-типа при вариации технологических параметров ТП от 550 нм до 70 нм.

Рисунок 2 - ВАХ транзистора n-типа при вариации технологических параметров ТП от 550 нм до 70 нм.

2.2. Определить время задержки для схемы

на рис.4. Сn = Cn+1

=

= 3,1994 ∗

= 3,1994 ∗

Ф

Ф

Описание инверторов в схеме задать с помощью макромодели (директива .SUBCKT).

МОП-транзистор описывается предложением

M xxx < узел стока > < узел затвора> < узел истока >

+ < узел подложки> <имя модели> [L=<значение>]

+ [W=<значение>] [AD=<значение>] [AS=<значение>]

+ [PD=<значение>] [PS=<значение>] [NRD=<значение>]

+ [NRS=<значение>] [NRG=<значение>] [NRB=<значение>]

+ [M=<значение>]

Макромодели. Отдельные фрагменты цепи или схемы замещения компонентов имеет смысл оформлять в виде макромоделей (подсхем). Описание макромодели начинается директивой .SUBCKT и заканчивается директивой .ENDS. Между ними помещаются описания компонентов, входящих в состав макромодели:

.SUBCKT < имя макромодели> <список узлов>

+ [PARAMS:<имя параметра>=<значение>]

{ описание компонентов }

.ENDS [имя макромодели]

Кусочно-линейная функция задается списком параметров:

PWL (t1 y1 t2 y2 ... tn yn)

Здесь (t1, y1), (t2, y2),... - координаты точек, через которые проходит функция y(t).

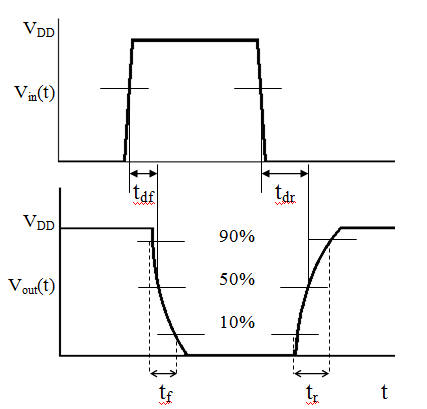

Рис. 3. Временные интервалы, связанные с переключением

логического вентиля

tr – rise time – время нарастания выходного сигнала от уровня 10% до 90% напряжения источника питания (VDD);

tf – fall time – время спада выходного сигнала от уровня 90% до 10% VDD;

td – delay time – время задержки – время между переключением входа (50%) и 50–процентным уровнем выходного сигнала (или принятом в данном аналитическом рассмотрении уровне).

Различают время задержки tdf и tdr. Первый параметр равен интервалу времени между входным и выходным импульсами при переходе напряжения на выходе от «1» к «0», измеренному на уровне 0.5VDD или на заданных уровнях напряжения, например Vinv. Второй параметр определяется таким же образом, но при переходе напряжения на выходе от «0» к «1».