Министерство науки и высшего образования Российской Федерации Федеральное государственное автономное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОННИКИ (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

КОМБИНАЦИОННЫЕ УСТРОЙСТВА Отчет по лабораторной работе №2

по дисциплине «Электроника и схемотехника» Вариант №3

Студент гр. 712-2

___________ Л.С. Болтушкин

18.05.2024

Руководитель Старший преподаватель кафедры КИБЭВС

_______ __________ А.С. Семенов

18.05.2024

Томск 2024

Введение

Целью данной лабораторной работы является изучение правильного

применения мультиплексора, шифратора и дешифратора.

Задачи:

1.Из таблицы вариантов лабораторной работы №1 взять 4 функции: свой вариант и еще три варианта на одну, две и три строки выше по таблице;

2.Собрать схему на холсте .bdf, согласно полученным формулам. Одна из функций обязательно должна быть реализована на дешифраторе (если в результате функции нулей меньше, чем единиц, то «по нулям», иначе «по единицам»), еще одна из функций должна быть реализована на мультиплексоре (MUX или lpm_mux – на выбор), еще одна функция должна быть реализована через формулы СДНФ/СКНФ (если в результате функции нулей меньше, чем единиц, то СКНФ) по таблице истинности и оставшаяся функция реализуется по заданной в таблице формуле. Выход схемы должен быть один, согласно варианту, «схема» из таблицы 3 первой части.

3.Промоделировать работу схемы в двух режимах. При моделировании на каждую функцию подайте две разные комбинации входных сигналов (x, y, z, w). В итоге для 4х функций должно быть минимум 8 разных комбинаций входных сигналов из таблицы истинности (x, y, z, w) таким образом, чтобы в результате не было только одни единицы или одни нули. Сделать предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему;

4.Сверить результаты моделирования с составленными таблицами истинности;

5.Повторить пункты 2-4, только для описания устройств вместо схем на холстах .bdf использовать заданный вариантом HDL и версию описания v1 или

v2, согласно разделу 9;

6. Построить таблицу истинности для приоритетного шифратора 4-2.

Составить формулы для каждого выхода, согласно закону де Моргана

2

преобразовать формулы в базис, заданный в варианте;

7.Собрать схему приоритетного шифратора на холсте .bdf согласно полученным формулам в базисе, заданном в варианте. Промоделируйте работу схемы. Если моделирование совпадает с таблицей истинности, то создайте символ, для его использования в другой схеме, иначе исправить схему, пока не будет достигнут правильный результат;

8.Собрать схему на холсте .bdf, согласно полученным формулам в пункте 7. Одна из функций обязательно должна быть реализована на дешифраторе (е если в результате функции нулей меньше, чем единиц, то «по нулям», иначе «по единицам»), ещё одна из функций должна быть реализована на мультиплексоре (MUX или lpm_mux – на выбор), ещё одна функция должна быть реализована через формулы СДНФ/СКНФ (если в результате функции нулей меньше, чем единиц, то СКНФ) по таблице истинности и оставшаяся функция реализуется по заданной в таблице формуле. Выход схемы должен быть один, согласно варианту, «схема» из табл. 3 второй части («выбор не двоичным кодом»);

9.Промоделировать работу схемы в двух режимах. При моделировании на каждую функцию подайте две разные комбинации входных сигналов (x, y, z, w). В итоге для 4х функций должно быть минимум 8 разных комбинаций входных сигналов из таблицы истинности (x, y, z, w). Выбирайте комбинации входных сигналов (x, y, z, w) таким образом, чтобы в результате не было только одни единицы или одни нули. Сделать предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему.

10.Сверить результаты моделирования с составленной таблицей истинности;

11.Повторить пункты 7-11, только для описания устройств вместо схем

на холстах .bdf использовать заданный вариантом HDL и версию описания v1

или v2, согласно разделу 9;

12. Написать выводы о проделанной работе.

3

1 Ход работы

1.1 Работа с первыми четырьмя функциями

|

|

|

|

|

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

|

|

|||||

|

Вариант 24 – F23 = A ( ( ∩ )) – По формуле; |

||||||||||||

|

Вариант 3 – F3 = A B C ∩ D – Дешифратор. Так как нулей меньше, |

||||||||||||

чем единиц, то реализация будет осуществляться по нулям; |

|||||||||||||

|

Вариант 2 – F2 = ∩ D – СКНФ: (A B C D) ∩ (A B |

||||||||||||

̅ |

̅ |

|

|

|

|

|

|

|

|

|

|

|

|

D) ∩ (A C D); |

|

|

|

|

|

|

|

|

|

|

|||

|

Вариант 1 – F1 = A ∩ B D – Мультиплекор. |

|

|

||||||||||

|

Таблица 1.1 – Таблица истинности для 4 первых функций. |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x |

y |

z |

|

w |

|

|

F24 |

F3 |

F2 |

F1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

0 |

|

|

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

1 |

|

|

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

0 |

|

|

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

1 |

|

|

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

0 |

|

|

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

1 |

|

|

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

0 |

|

|

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

1 |

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

0 |

|

|

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

1 |

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

0 |

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

1 |

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

0 |

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

1 |

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

|

0 |

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

|

1 |

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

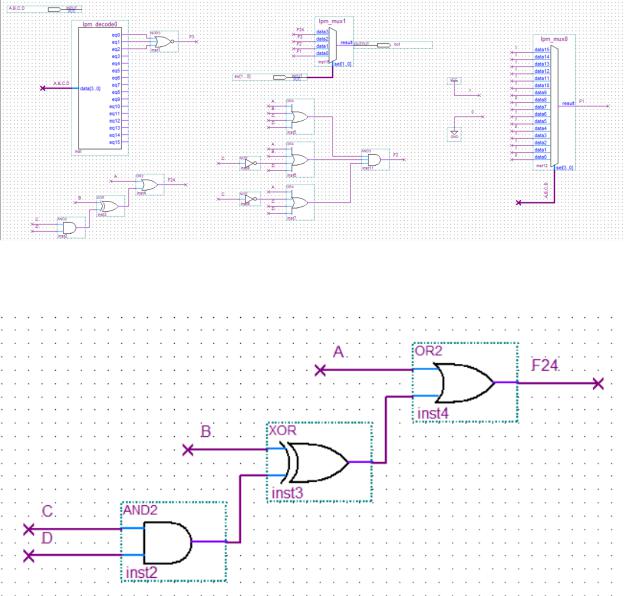

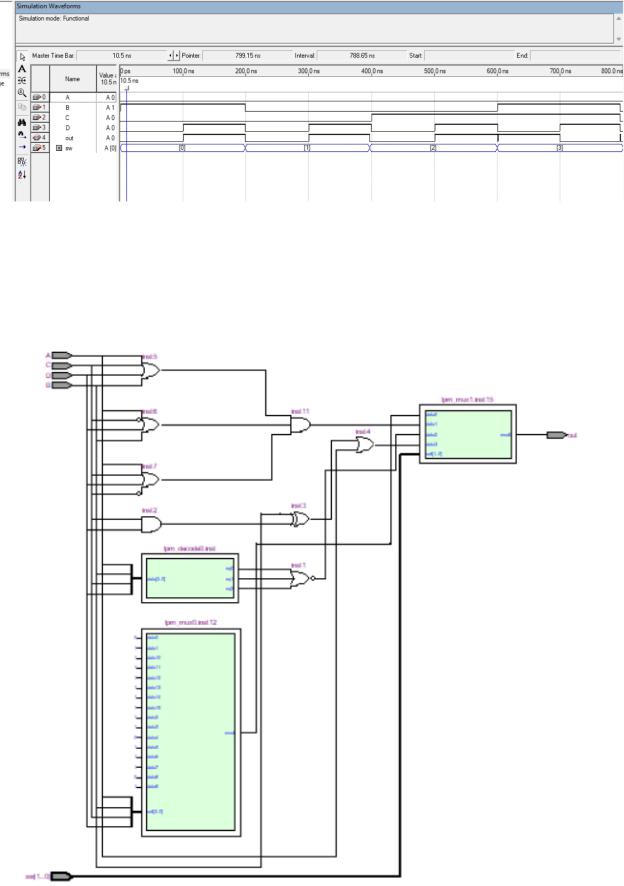

На рисунке 1.1 представлена общая функциональная схема для функций

F24, F3, F2, F1. И на рисунках 1.2 – 1.5 каждая схема изображена по отдельности.

Рисунок 1.1 – Функциональная схема

Рисунок 1.2 – Обычная функция

5

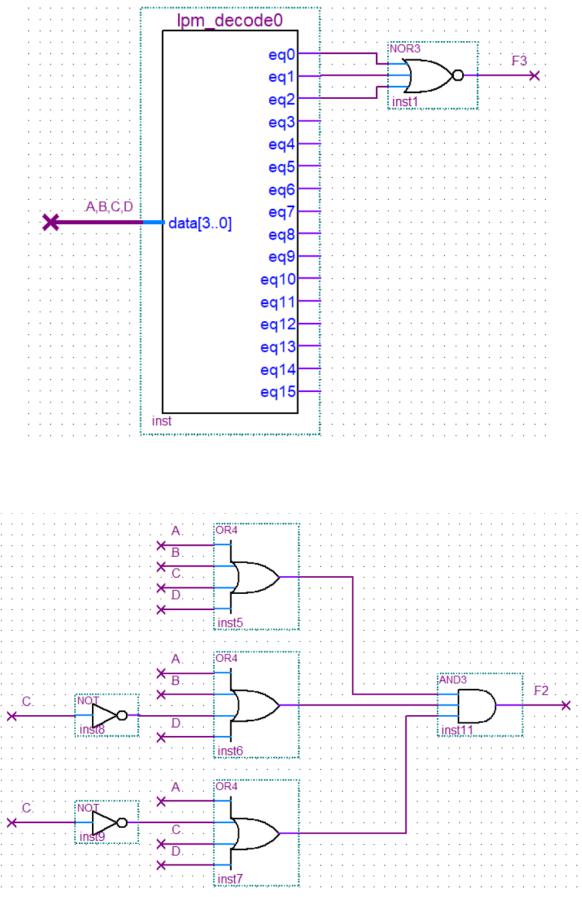

Рисунок 1.3 – Дешифратор

Рисунок 1.4 – СКНФ

6

Рисунок 1.5 – Мультиплексор

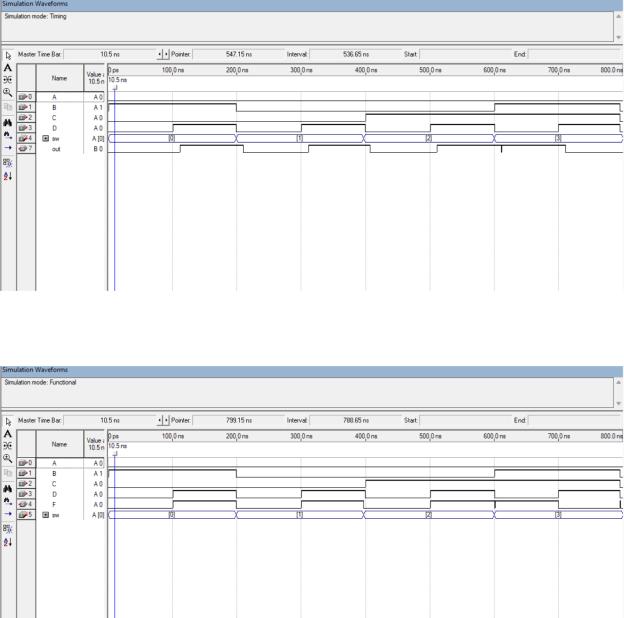

Результат моделирования схемы в двух режимах представлен на рисунках 1.6 – 1.7.

7

Рисунок 1.6 – Моделирование схемы в режиме Timing

Рисунок 1.7 – Моделирование схемы в режиме Functional

Проанализировав значения в таблице истинности с результатами моделирования можно сделать вывод, что результаты идентично совпадают.

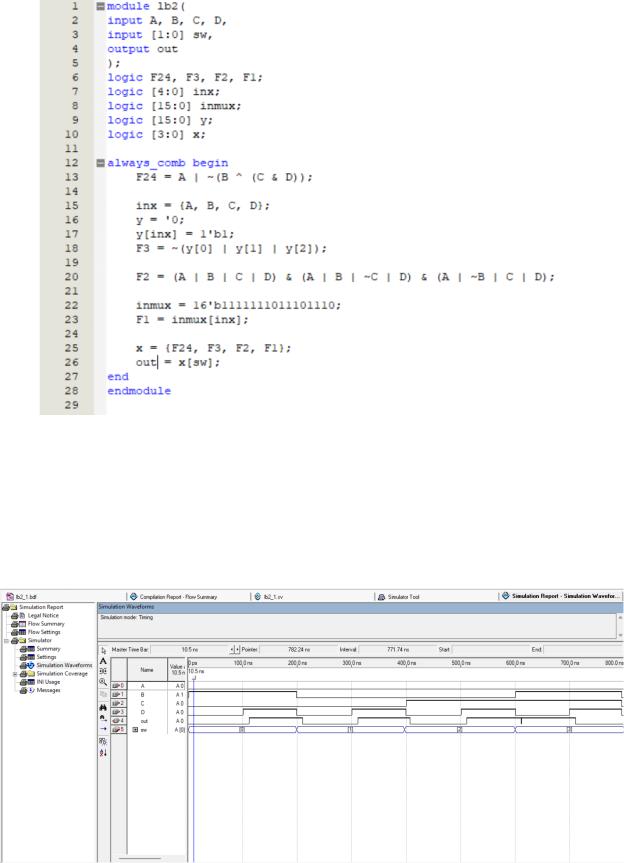

Код на System Verilog представлен на рисунке 1.8.

8

Рисунок 1.8 – Описание устройства на System Vertilog

Работа схемы, описанной в виде кода, также была промоделирована в двух режимах. Комбинации входных данных аналогичны тем, что и использовались в прошлом моделировании (рисунок 1.9 – 1.10).

Рисунок 1.9 – Моделирование кода в режиме Timing

9

Рисунок 1.10 – Моделирование кода в режиме Functional

По коду было построено схемотехническое представление при помощи инструмента RTL Viewer (рисунок 1.11).

Рисунок 1.11 – Схема по коду в RTL Viewer

10