Болтушкин, группа 712-2, отчёт по лабораторной работе 4

.pdfМинистерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение

высшего образования ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ

УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ СТРУКТУРНОЙ ОРГАНИЗАЦИИ БАЗОВОЙ УЧЕБНОЙ ЭВМ (БУ ЭВМ)

Лабораторная работа №4 по дисциплине «Организация ЭВМ и вычислительных систем»

Студент гр. 712-2

___________ Л.С. Болтушкин

___________

Руководитель

Преподаватель кафедры КИБЭВС

_______ __________ А.С. Семенов

__________

Томск, 2022

Введение

Целью работы является изучение структурной и функциональной

организации процессора на примере базовой учебной ЭВМ.

1 Ход выполнения работы

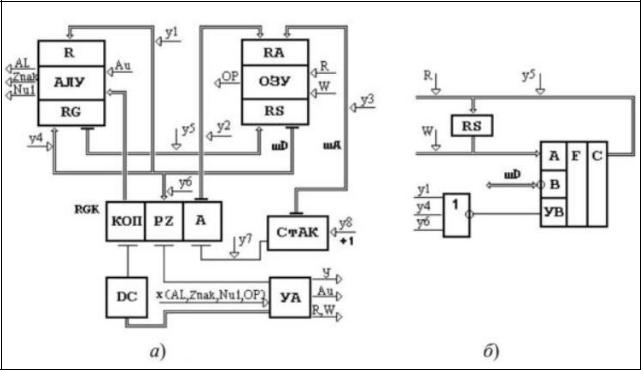

Базовая учебная машина (БУ ЭВМ) - устройство, выполняющее заданные программой преобразования информации и осуществляющее управление всем вычислительным процессом. БУ ЭВМ дешифрирует и выполняет последовательно команды программы. БУ ЭВМ содержит:

арифметико-логическое устройство (АЛУ), центральное устройство управления (ЦУУ), а также оперативное запоминающее устройство (ОЗУ)

небольшой емкости (рисунок 1.1).

Рисунок 1.1 – Структура процессора (а) и фрагмент ОЗУ (б)

АЛУ базовой учебной ЭВМ может совершать операции над двумя операндами, один операнд находится в аккумуляторе АКК, а второй извлекается командой из памяти. Результат выполнения операции остается в АКК и RG.

Запуск

выполнение

формируются

признак результата; сигнал АL - если устройство работает. OЗУ в соответствии с сигналами R и W выполняет чтение или запись слова по определенному адресу и вырабатывает сигнал ОР, говорящий о том, что ОЗУ занято. ОЗУ содержит 94 ячейки памяти, причем ячейки с 1 по 70 хранят команды, с 71 по

94- данные.

УУсостоит из управляющего автомата (УА), регистра команд (RGK),

дешифратора (DC) и счетчика адресов команд (CТAK).

По существу, вся БУ ЭВМ представляет собой набор различных регистров. В зависимости от того, в каком регистре находится группа бит,

изменяется смысл содержащейся в нем информации. Те слова, которые находятся в памяти или в процессе передачи между регистрами, еще не обладают определенным смысловым значением. В памяти могут находиться команды, а также операнды или данные, то есть исходная информация,

подлежащая обработке. Отделение команд от данных осуществляется именно центральным процессором. Для этого команды направляются в один из регистров - регистр команд (RGK), а данные направляются в другой регистр,

регистр данных (RG).

Регистр команд функционально входит в состав устройства управления,

а регистр данных — это практически один из регистров АЛУ. АЛУ служит для выполнения арифметических и логических преобразований информации. В

нем производятся операции сложения, вычитания, умножения и деления.

Шина адреса (шА) подключена ко входу регистру адреса (RA) памяти ОЗУ и соединена с выходом мультиплексора отсылок и пультовым терминалом шА загружают отсылкой (В, С) с выхода мультиплексора отсылок по команде «Р» (продолжить), которая формируется с пультового терминала.

Шина данных (шD) связывает ОЗУ с регистром RGK команд и терминалом. ОЗУ имеет порт ввода-вывода RS (регистр слова). Передача слова из порта RS на RGK возможна при условии, что клавиша Р (продолжить)

не нажата, другими словами, команда «Р» пультового терминала не введена, и

был произведен запуск программы («ПУСК»). Через порт RS в память по шине шD данные вводятся с пультового терминала (управляющий сигнал «W»).

По шине управления передаются сигналы, определяющие характер обмена информацией (считывание или запись информации из памяти) по магистрали. Эта шина не имеет такой же четкой структуры, как шина данных или шина адреса. В шину управления условно объединяют набор линий,

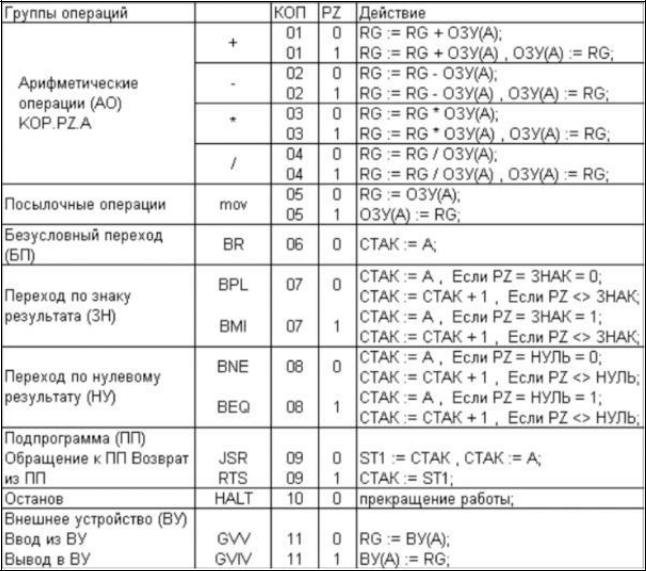

передающих различные управляющие сигналы от процессора на все периферийные устройства и обратно (рисунок 1.2).

Рисунок 1.2 – Система команд

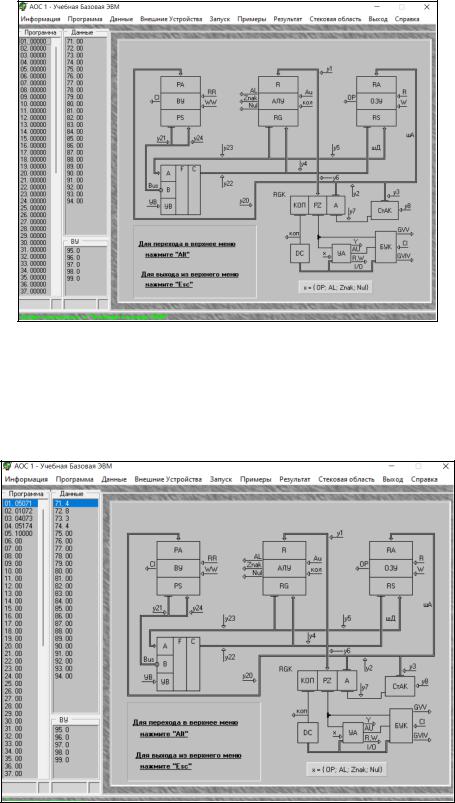

В данной лабораторной работе стояла задача – используя АОС 1 базовой учебной ЭВМ вычислить данное уравнение – (4+8)/3

Для выполнения лабораторной работы была запущена программа «АОС

1 – Учебная Базовая ЭВМ» (рисунок 1.3).

Рисунок 1.3 – Запуск АОС 1 – Учебная Базовая ЭВМ

Изучив методическое пособие и информацию о командах в программе

«АОС 1 – Учебная Базовая ЭВМ» была написана программа (рисунок 1.4).

Рисунок 1.4 – Рабочая программа

Алгоритм:

1)05071 – Присвоение значения регистру 71

2)01072 – Сложение значения регистра 71 с значением регистра 72

3)04073 – Нахождение частного от деления сложения 71 и 72 регистра на значение 73 регистра

4)05174 – Вывод значения из ОЗУ в 74 регистр

5)10000 – Остановка программы

Заключение

В данной лабораторной работе были изучены структурные и

функциональные организации процессора на примере базовой учебной ЭВМ.