- •Пояснительная записка к курсовому проекту

- •Введение

- •Анализ технического задания

- •Анализ существующих схем памяти

- •3 Выбор элементной базы памяти озу и пзу

- •4 Алгоритм увеличения разрядности чисел в памяти

- •5 Алгоритм увеличения информационного объема памяти

- •6 Разработка схемы, начертания интегральной схемы Пзу

- •7 Разработка схемы, начертание интегральное схемы озу

- •8 Карта памяти синтезированной схемы памяти

- •9 Разработка схемы дешифрации памяти

- •10 Синтез схемы памяти заданного объёма

- •11 Подбор имс памяти

- •12 Расчеты быстродействия, надежности, помехоустойчивости, потребляемой мощности и других параметров интегральных микросхем

- •13 Разработка платы

- •Заключение

- •Список используемых источников

6 Разработка схемы, начертания интегральной схемы Пзу

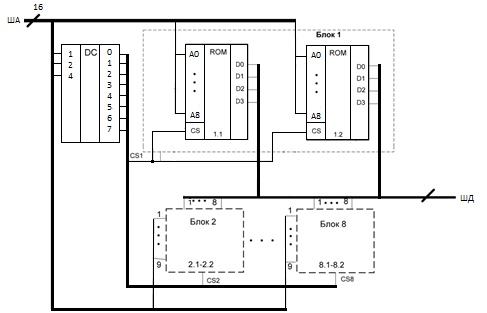

В соответствии с техническим задание необходимо разработать схему памяти ПЗУ, информационным объемом 4К и разрядностью 8 на базе имеющихся ИМС 512×8. Таким образом, для реализации такой схемы понадобятся 8 блоков заданные ИМС, соединенные по схеме наращивания объема памяти. Схема представлена на рисунке 6.1.

Рисунок 6.1 – Синтезированная схема ПЗУ

На схеме, изображенной на рисунке 6.1, можно видеть, что она состоит из 2 ИМС памяти и дешифратора. С правилами наращивания информационного объема памяти, младшие 9 разрядов адреса параллельно подключены к обеим ИМС. Так же, параллельно подключены и 4 разряда данных. Дешифратор в схеме используется для выбора кристалла. В зависимости от сигнала на его входе, будет работать первая или вторая ИМС. Сигнал на входе дешифратора – это старший разряд адреса. Таким образом, синтезирована схема памяти ПЗУ 4К×8.

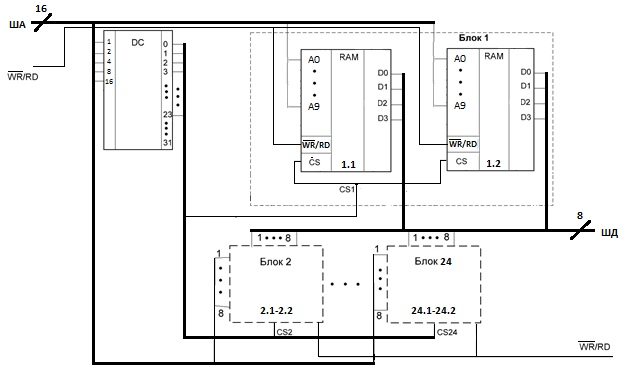

7 Разработка схемы, начертание интегральное схемы озу

Схема ОЗУ, в отличие от схемы ПЗУ, требует наращивания не только информационного объема, но и разрядности. Необходимо синтезировать схему ОЗУ информационным объемом 23,25К и разрядностью 8 на базе ИМС 1К×4. Согласно алгоритмам увеличения информационного объёма при фиксированной разрядности данных и увеличение чисел в памяти необходимо объединить данные ИМС в блоки. Таким образом в одном блоке ОЗУ объедено по две ИМС 1К×4. Получается, что в схеме памяти используется 24 блока. Схема представлена на рисунке 7.1

Рисунок 7.1 – Синтезированная схема ОЗУ

Схема дешифрации представляет собой дешифратор, имеющий 5 входа и 32 выхода. Он позволит выработать сигналы выбора ИМС для 24 блоков. Так как в каждом блоке содержится по 2 ИМС, которые содержат по одному разряду 4-разрядного слова, то работать они все должны одновременно. Значит, сигналы выбора ИМС в каждом блоке активируют одновременно все ИМС, т.е. подключаются параллельно.

Работает схема следующим образом. При подаче на шину адреса 16-разрядного адресного кода младшие 10 разрядов поступают одновременно на все ИМС, а старшие 6 – на дешифратор. Дешифратор в соответствии с полученным кодом активирует один из своих выходов, сигнал с которого поступает на определенный блок. В рамках выбранного блока этот сигнал поступает на все ИМС на разрешающие входы, тем самым активируя их. В результате 48 активных ИМС выдают на шину данных по четыре разряду, образуя одно 8-разрядное слово. Так же можно организовать и процесс записи в память, если выбранные ИМС имеют такую возможность, т. е. входы записи/считывания.

Таким образом, синтезирована схема памяти ОЗУ информационным объемом 23,25К и разрядностью 8 на базе ИМС 1К×4.

8 Карта памяти синтезированной схемы памяти

Начальный адрес всего блока памяти составляет 0000 0000 0000 00002=000016.

Таблица 8.1 – Карта памяти синтезированной схемы памяти

Двоичный код |

Шестнадцатиричный код |

Элемент |

1 |

2 |

3 |

0000 0000 0000 0000 |

0000 |

ПЗУ-1 |

0000 0001 1111 1111 |

01FF |

|

0000 0010 0000 0000 |

0200 |

ПЗУ-2 |

0000 0011 1111 1111 |

03FF |

|

0000 0100 0000 0000 |

0400 |

ПЗУ -3 |

0000 0101 1111 1111 |

05FF |

|

0000 0110 0000 0000 |

0600 |

ПЗУ-4 |

0000 0111 1111 1111 |

07FF |

|

0000 1000 0000 0000 |

0800 |

ПЗУ -5 |

0000 1001 1111 1111 |

09FF |

|

0000 1010 0000 0000 |

0A00 |

ПЗУ -6 |

0000 1011 1111 1111 |

0BFF |

|

0000 1100 0000 0000 |

0C00 |

ПЗУ -7 |

0000 1101 1111 1111 |

0DFF |

|

0000 1110 0000 0000 |

0E00 |

ПЗУ -8 |

0000 1111 1111 1111 |

0FFF |

|

0001 0000 0000 0000 |

1000 |

ОЗУ - 1 |

0001 0011 1111 1111 |

13FF |

|

0001 0100 0000 0000 |

1400 |

ОЗУ - 2 |

0001 0111 1111 1111 |

15FF |

|

0001 1000 0000 0000 |

1800 |

ОЗУ - 3 |

0001 1011 1111 1111 |

1BFF |

|

0001 1100 0000 0000 |

1C00 |

ОЗУ - 4 |

0001 1111 1111 1111 |

1FFF |

|

0010 0000 0000 0000 |

2000 |

ОЗУ - 5 |

0010 0011 1111 1111 |

33FF |

|

0010 0100 0000 0000 |

2400 |

ОЗУ - 6 |

0010 0111 1111 1111 |

27FF |

|

0010 1000 0000 0000 |

2800 |

ОЗУ - 7 |

0010 1011 1111 1111 |

2BFF |

|

0010 1100 0000 0000 |

2C00 |

ОЗУ - 8 |

0010 1111 1111 1111 |

2FFF |

|

0011 0000 0000 0000 |

3000 |

ОЗУ - 9 |

0011 0011 1111 1111 |

33FF |

|

0011 0100 0000 0000 |

3400 |

ОЗУ - 10 |

0011 0111 1111 1111 |

37FF |

1 |

2 |

3 |

0011 1000 0000 0000 |

3800 |

ОЗУ - 11 |

0011 1011 1111 1111 |

3BFF |

|

0011 1100 0000 0000 |

3C00 |

ОЗУ - 12 |

0011 1111 1111 1111 |

3FFF |

|

0100 0000 0000 0000 |

4000 |

ОЗУ - 13 |

0100 0011 1111 1111 |

43FF |

|

0100 0100 0000 0000 |

4400 |

ОЗУ - 14 |

0100 0111 1111 1111 |

47FF |

|

0100 1000 0000 0000 |

4800 |

ОЗУ - 15 |

0100 1011 1111 1111 |

4BFF |

|

0100 1100 0000 0000 |

4C00 |

ОЗУ - 16 |

0100 1111 1111 1111 |

4FFF |

|

0101 0000 0000 0000 |

5000 |

ОЗУ - 17 |

0101 0011 1111 1111 |

53FF |

|

0101 0100 0000 0000 |

5400 |

ОЗУ - 18 |

0101 0111 1111 1111 |

57FF |

|

0101 1000 0000 0000 |

5800 |

ОЗУ - 19 |

0101 1011 1111 1111 |

5BFF |

|

0110 0000 0000 0000 |

6000 |

ОЗУ - 20 |

0110 0011 1111 1111 |

63FF |

|

0110 0100 0000 0000 |

6400 |

ОЗУ - 21 |

0110 0111 1111 1111 |

67FF |

|

0110 1000 0000 0000 |

6800 |

ОЗУ – 22 |

0111 1011 1111 1111 |

6BFF |

|

0110 1100 0000 0000 |

6C00 |

ОЗУ – 23 |

0110 1111 1111 1111 |

6FFF |

|

0111 0000 0000 0000 |

7000 |

ОЗУ - 24 |

0111 0011 1111 1111 |

73FF |

Окончание таблицы 8.1