ЭБНЭ_Л4_Цуканова_0363

.pdfМИНОБРНАУКИ РОССИИ САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ «ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА) Кафедра микро- и наноэлектроники

ОТЧЕТ по лабораторной работе №4

по дисциплине «Элементная база наноэлектроники» Тема: Исследование работы логических схем 2ИЛИ и 2ИЛИ-НЕ

Студент гр. 0363 |

Цуканова П.А. |

Преподаватель |

Усикова М.А. |

Санкт-Петербург

2022

Цель работы:

Исследование работы логических схем 2ИЛИ и 2ИЛИ-НЕ с помощью программы Multisim.

Теоретическая часть:

КМОП (комплементарная структура металл-оксид-полупроводник, англ.

CMOS, complementary metal-oxide-semiconductor) — набор полупроводниковых технологий построения интегральных микросхем и соответствующая ей схемотехника микросхем. Подавляющее большинство современных цифровых микросхем — КМОП.

В технологии КМОП используются полевые транзисторы с изолированным затвором с каналами разной проводимости. Отличительной особенностью схем КМОП по сравнению с биполярными технологиями является очень малое энергопотребление в статическом режиме (в большинстве случаев можно считать, что энергия потребляется только во время переключения логических состояний). Отличительной особенностью структуры КМОП по сравнению с другими МОП-структурами (N-МОП, P-МОП) является наличие как n-, так и p-

канальных полевых транзисторов локализованных в одном месте. Вследствие меньшего расстояния между элементами КМОП-схемы обладают большим быстродействием и меньшим энергопотреблением, однако, при этом характеризуются более сложным технологическим процессом изготовления и меньшей плотностью упаковки на поверхности кристалла. По аналогичной технологии выпускаются дискретные полевые транзисторы с изолированным затвором (MOSFET).

Логическими схемами 2ИЛИ и 2ИЛИ-НЕ являются схемы, реализующие простые логические операции ИЛИ и ИЛИ-НЕ соответственно, получая на вход ровно два значения. Более подробно рассмотрим эти логические схемы ниже.

Экспериментальная часть:

1. Собрать схемы 2ИЛИ и 2ИЛИ-НЕ на КМОП-транзисторах.

2

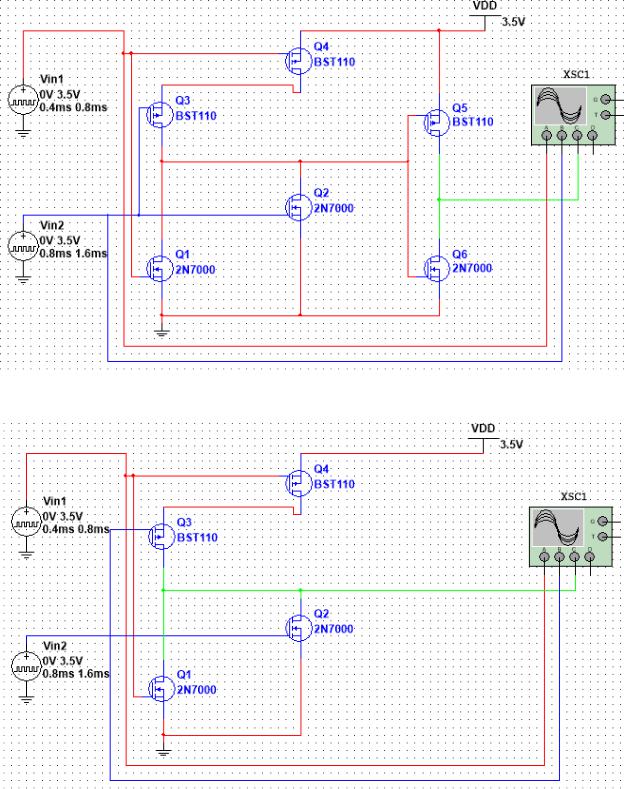

Полученная схема логического элемента 2ИЛИ приведена на рисунке 1.

Схема логического элемента 2ИЛИ-НЕ показана на рисунке 2.

Рисунок 1 — Реализованная схема 2ИЛИ

Рисунок 2 — Реализованная схема 2ИЛИ-НЕ

3

2. Представить условное графическое изображение Условное графическое изображение схемы 2ИЛИ показано на рисунке 3.

Рисунок 3 — Условное графическое изображение схемы 2ИЛИ Условное графическое изображение схемы 2ИЛИ-НЕ показано на рисунке

4.

Рисунок 4 — Условное графическое изображение схемы 2ИЛИ-НЕ

3. Привести таблицу истинности На таблице 1 представлена таблица истинности

вх1 |

вх2 |

(2ИЛИ) |

(2ИЛИ − НЕ) |

|

|

вых |

вых |

0 В |

0 В |

0 В |

3.5 В |

|

|

|

|

0 В |

3.5 В |

3.5 В |

0 В |

|

|

|

|

3.5 В |

0 В |

3.5 В |

0 В |

|

|

|

|

3.5 В |

3.5 В |

3.5 В |

0 В |

|

|

|

|

Таблица 1 — Таблица истинности

4. Построить графики функционирования (временная зависимость напряжения на входе/выходе).

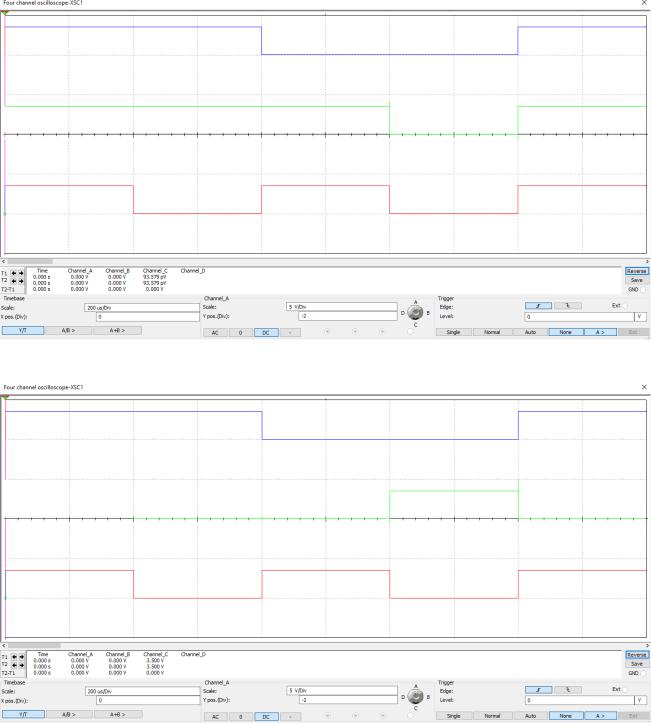

На рисунках 5 и 6 показаны графики функционирования для схем 2ИЛИ и

2ИЛИ-НЕ соответственно. Здесь, красный график – сигнал на входе 1, синий график – сигнал на входе 2, зеленый – сигнал на выходе.

4

Рисунок 5 — Графики функционирования для схемы 2ИЛИ

Рисунок 6 — Графики функционирования для схемы 2ИЛИ-НЕ

Вывод:

В ходе данной лабораторной работы были изучены логические схемы

2ИЛИ и 2ИЛИ-НЕ, а также реализация данных схем на КМОП-транзисторах.

5