билеты_41_81

.pdf

Билет 71.

Шифраторы и дешифраторы. Арифметические цифровые устройства

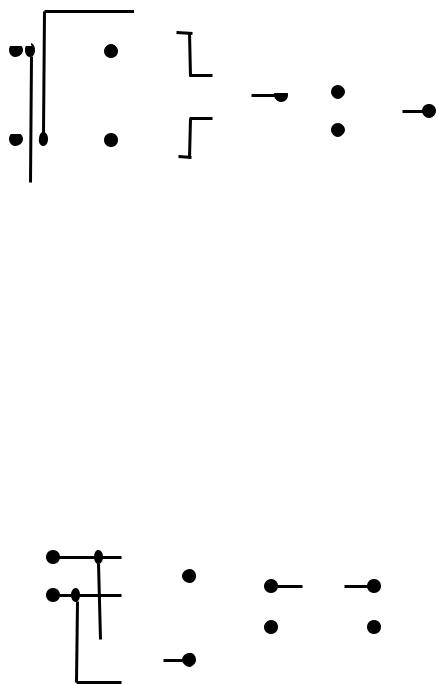

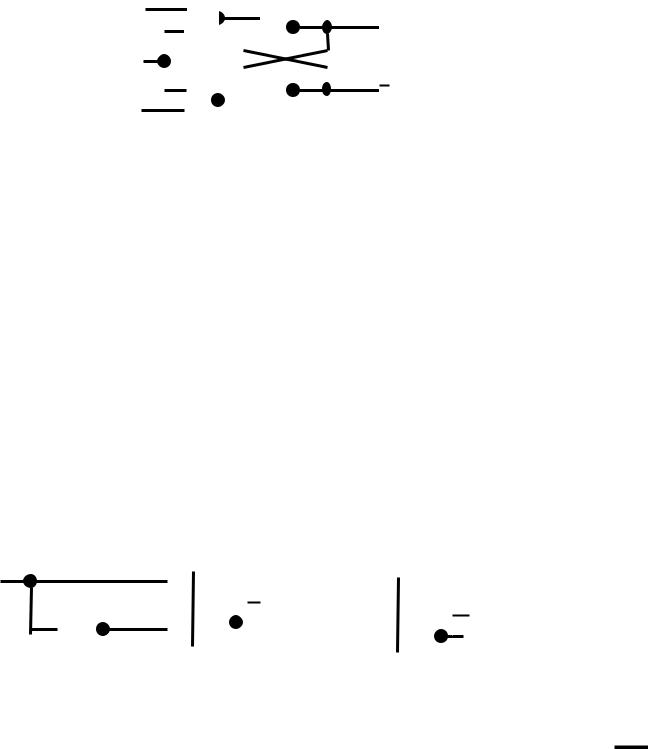

Шифраторы выполняют операцию преобразования кодов. Например, преобразование десятичного числа в его двоично-десятичный аналог. Структурная схема такого шифратора приведена на рис.7.3.4.

0 |

|

|

|

|

|

|

|

|

|

|

1 |

8 |

Y4 |

|

|

|

|

Y4 |

||

|

|

|

|

|

|

|

|

|

|

|

0 |

CD |

|

|||||||

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

||||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

4 |

|

|

2 |

|

|

Y3 |

|||

3 |

|

|

|

|

|

|

|

|

Y3 |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

4 |

|||||

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

Y2 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

5 |

|

|

|

|

|

|

|

|

|

|

|

5 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

1 |

2 |

Y2 |

|

2 |

||||||

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

Y4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

|

||

8 |

|

|

|

|

|

|

|

|

|

|

1 |

1 |

Y1 |

|

1 |

|||||

|

|

|

|

|

|

|

|

|

|

|

9 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а) |

|

|

|

|

|

|

б) |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||

Рис.7.3.4. Структурная схема шифратора (а) и его условное обозначение (б).

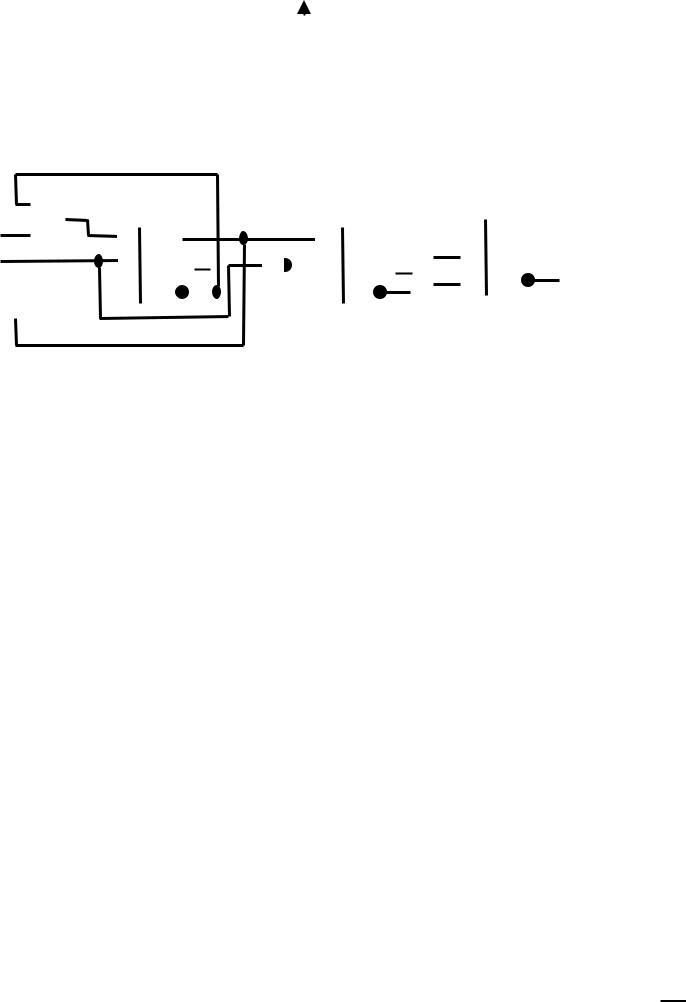

Дешифратор выполняет обратную операцию преобразования кодов. Например, преобразование двоично-десятичного кода в десятичный аналог. Структурная схема такого дешифратора приведена на рис.7.3.5.

Y4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

В |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y4 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

DС |

0 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Х Y3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y3 |

|

|

2 |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

3 |

|

|||

О Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

|

||||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Д Y1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

6 |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y1 |

|

|

8 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

… |

|

|

|

|

|

|

|

|

|

|

1 |

|

9 |

|

||

a) |

|

& |

|

& |

|

|

|

& |

|

|

& |

|

|

|

б) |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

0 |

1 |

|

|

8 |

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

В Ы Х О Д |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

Рис.7.3.5. Структурная схема дешифратора (а) и его условное обозначение (б).

7.3.2. Арифметические цифровые устройства

Рассмотрим одноразрядное сложение двоичных чисел.

0 |

1 |

0 |

1 |

|

|

|

+ 0 |

+0 |

+1 |

+1 |

|

|

|

|

|

1 |

1 |

|

|

|

|

0 |

0 и перенос единицы в следующий разряд. |

||||

а). Арифметическое устройство сложения по модулю 2 (исключительное “ИЛИ”)

Устройством сложения по модулю 2 называется логический элемент, имеющий 2 (два) входа и 1 (один выход), функциональная характеристика которого описывается таблицей истинности, изображенной на рис.7.3.6.

x1x2Y000011101 x1 |

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

110 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y |

x1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

Y |

|||

|

x2 |

|

|

|

|

|

|

|

1= |

|

||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||

а) |

|

|

|

|

|

|

|

|

|

|

|

|

|

x2 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

||||||

0110 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б) |

|

|

|

|

|

|

в) |

|

|

|

|

г) |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

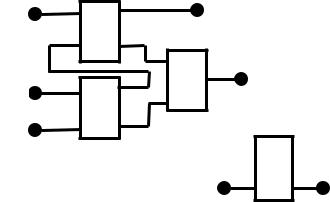

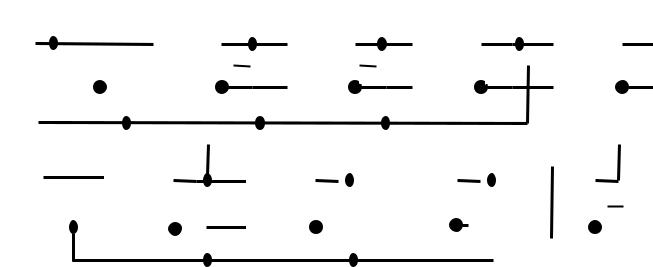

Рис.7.3.6. Таблица истинности (а), карта Карно (б), структурная схема (в) и |

||||||||||||||||||||||

условное обозначение (г) логического устройства сложения по модулю 2. |

|

|||||||||||||||||||||

В соответствии с картой Карно (рис.7.3.6,б) структурная формула |

||||||||||||||||||||||

исключительного “ИЛИ” принимает вид |

|

|

|

|

|

|

|

|||||||||||||||

Y = x1 × x2 |

+ x1 × x2 |

или |

|

|

в сокращенной записи |

|

|

|

|

|

|

|||||||||||

Y = x1 Å x2 |

, |

|

|

|

|

|

|

|

|

|

|

|

|

|

(7.3.1) |

|

|

|||||

а структурная схема вид, изображенный на рис.7.3.6,в. Для сокращения формата структурных схем, содержащих исключительные “ИЛИ”, используется условное обозначение логического устройства сложения по модулю 2, приведенное на рис.7.3.6,г.

б). Одноразрядный полусумматор

Полусумматором называется арифметическое устройство, имеющее два входа и два выхода, один из которых служит для вывода результата суммы значений одного

разряда слагаемых Y1, а второй – для переноса единицы в следующий разряд Yi. Таблица истинности полусумматора приведена на рис.7.3.7,а.

|

|

|

x1 |

|

|

|

|

|

|

|

|

|

а) |

x1x2Y1Yi0000011 |

1= |

Y1 |

x1 |

|

|

Y1 |

|||||

x2 |

|

|

||||||||||

|

|

|

pS |

|

||||||||

|

|

|

|

|||||||||

|

|

|

|

|

|

|||||||

|

|

010101101 |

|

|

|

|

|

x2 |

|

|

|

Yi |

|

|

|

г) |

|

|

Yi |

|

|

|

|||

|

|

|

|

& |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

0110 |

0001 |

|

|

|

д) |

|

|

|||||

|

|

|

|

|

|

|

||||||

б) |

|

|

|

|

|

|

|

|

|

|

|

|

|

в) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.7.3.7. Таблица истинности (а), карта Карно для выхода Y1 (б), карта Карно для

выхода Yi (в), структурная схема (г) и условное обозначение (д) полусумматора. Структурная формула для выходной функции Y1 в соответствии с картой Карно

будет иметь вид Y1 = x1 Å x2 ,

а для выходной функции Yi

Yi = x1 × x2 .

б). Одноразрядный полный сумматор

Полным сумматором называется арифметическое устройство, имеющее три входа и два выхода, один из которых служит для вывода результата суммы значений

одного разряда слагаемых Y1, а второй – для переноса единицы в следующий разряд Yi.

На третий вход постыпает сигнал переноса с предыдущего разряда Yi-1 Таблица истинности полусумматора приведена на рис.7.3.8,а.

а) |

|

Yi-1 |

Yi- |

|

|

|

1x1x2Y1Yi0000000110 |

г) |

|

010100110110010101 |

x1 |

|

011 100111111 |

|

|

|

|

|

|

x2 |

01011010 00100111

б)

в)

|

Y1 |

pS |

Yi |

|

1 Yi |

pS |

Yi |

x1

S

S

Yi

Yi

xi |

Y1 |

Рис.7.3.7. Таблица истинности (а), карта Карно для выхода

выхода Yi (в), структурная схема (г) и условное обозначение (д) полусумматора.

Билет 72. Последовательностные цифровые устройства.

Последовательностными называются цифровые устройства, значения переменных которых в данный момено времени определяются как значениями входных переменных в этот момент времени, так и значениями выходных переменных в предшествующий, т.е. последовательностные цифровые устройства обладают “памятью”.

Обобщенная структурная схема последовательностного цифрового устройства приведена на рис.7.4.1

x

Комбинационное цифровое устройство

Комбинационное цифровое устройство

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ТТ |

|

|

|

ТТ |

|

|

|

|

|

|

ТТ |

|

|

ТТ |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y |

ТТ |

Триггеры

Рис.7.4.1. Обобщенная структурная схема последовательностного цифрового устройства.

Обобщенная структурная схема последовательностных цифровых устройств включает в себя комбинационное цифровое устройство и элементы памяти триггеры.

К основным типам последовательностным цифровым устройствам относятся триггеры, регистры сдвига, запоминающие устройства, генераторы двоичных чисел,

счетчики.

Билет 73.Асинхронный и синхронный RS – триггеры.

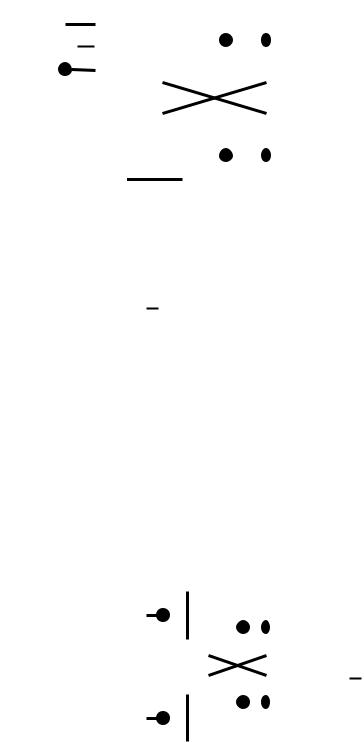

а). Асинхронный RS – триггер

Условное графическое обозначение RS-триггера приведено на рис.7.4.1,а, а его структурная схема на двух логических элемента “2ИЛИ - НЕ” на рис.7.4.1,б.

При подаче на оба входа уровня логического нуля на выходах триггера сохраняются предыдущее уровни выходных сигналов (режим хранения информации).

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

При подаче |

на |

вход |

R |

||||

|

|

|

|

Q R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

уровня логического нуля, |

||||||||

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

а |

на |

вход |

S |

уровня |

||||

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

логической |

единицы |

на |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

выходе |

|

|

|

|

Q |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

устанавливается |

уро- |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

вень |

логической еди- |

||||||

|

|

а) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ницы. При подаче на вход |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

уровня |

логической |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

единицы, |

а |

на |

вход |

S |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

уровня логического нуля |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

на выходе Q устанавли- |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

вается |

|

уровень |

логи- |

||||

Рис.7.4.1. Условное обозначение RS-триггера на логиче- |

ческого нуля. При подаче |

||||||||||||||||||||||||||||||||

на |

оба |

входа |

уровня |

||||||||||||||||||||||||||||||

ских элементах 2ИЛИ-НЕ (а) и его структурная схема (б). |

|||||||||||||||||||||||||||||||||

логической |

единицы |

на |

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

обоих |

выходах триггера |

||||||

|

|

|

|

|

|

Q |

|

устанавливается уровень логической единицы. |

|||||||||||||||||||||||||

Режимы работы |

|

|

|

|

Это запрещенное состояние |

триггера |

(не |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

используется). Таблица |

истинности |

для RS- |

||||||||||||||||||

|

RSQХранения |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

Q |

|

|

|

|

|

триггера приведена на рис.7.4.2. Из таблицы |

|||||||||||||||||||||||||

|

00QУстановка 1 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

видно, что |

перевод |

триггера |

в |

состояние 1 |

|||||||||||||||||

|

0110Установка 0 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

осуществляется уровнем логической 1 на входе |

|||||||||||||||||||||

|

1001Запрещенный |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

S, а в состояние 0 – уровнем логической 1 на |

|||||||||||||||||||||

|

|

|

1100 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

входе R. |

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RS-триггер может быть выполнен и на |

||||||||||||||

Рис.7.4.2. Таблица истинности RS-триггера. |

|

логических |

ячейках |

“2И-НЕ”. Структурная |

|||||||||||||||||||||||||||||

|

схема такого триггера приведена на рис.7.4.3. |

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В этой схеме для сохранения таблицы истин- |

|||||||||||||||||

ности введены два инверс-ных элемента. При отсутст-вии этих элементов таблица |

|||||||||||||||||||||||||||||||||

истинности приняла бы инверсный вид. |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

Эти триггеры иногда называют бистабильными ячейками. |

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

Рис.7.4.3. Структурная RS- |

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

триггера на логических |

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

элементах “2И-НЕ”. |

|

|

|

|

|

|

|

|||||||||||||||

б). Синхронный RS – триггер

Условное графическое обозначение синхронного RS-триггера (а) и его структурная схема с использованием логических элементов “2ИЛИ - НЕ” (б) приведены на рис.7.4.4.

Синхронный RS-триггер отличается от обычного RS-триггера наличием 3-его (синхронизирующего) входа, на который подаются тактовые (синхронизирующие) импульсы. При этом синхронизирующие импульсы не оказывают никакого влияния на состоянивыхода Q, когда на обоих входах установлен уровень логического нуля. При наличии тактовых (синхронизирующих) импульсов работа схемы не отличается от

|

|

|

Q |

|

|

|

|

|

|

|

|

|

R |

|

|

R |

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

С |

Т |

Q |

|

|

|

1 |

|

|

Q |

|

|

|

|

|

|

|||||||

|

S |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

а)

С

1

1

& |

|

Q |

S

б)

Рис.7.4.4. Условное обозначение синхронного RS-триггера (а) и его структурная схема (б).

работы обычного RS-триггера.

Таблица истинности синхронного RS-триггера приведена на рис.7.4.5. Из таблицы видно, что перевод триггера в состояние 1 осуществляется уровнем логической 1 на входе S, а в состояние 0 – уровнем логической 1 на входе R.

Q

Режимы работы

СRSQХранения Q 100QУстановка 1 10110Установка 0

11001Запрещенный

11100

Рис.7.4.5. Таблица истинности синхронного RS-триггера.

RS-триггер может быть |

выполнен и на логических ячейках “2И-НЕ”. |

|||||||||

Структурная схема такого триггера приведена на рис.7.4.6. |

|

|||||||||

R |

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

||

& |

|

|

Q |

|||||||

|

|

|

|

|

|

|

|

|||

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|||

|

|

& |

|

|

|

|

|

Q |

||

S |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

Рис.7.4.6 . Структурная синхронного RS-триггера |

||||||||||

на логических элементах “2И-НЕ”. |

||||||||||

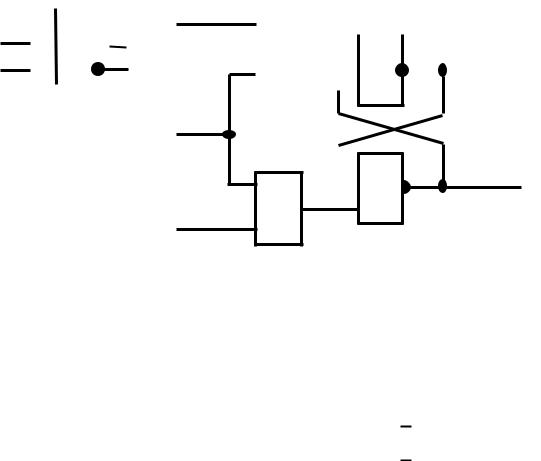

Билет 74. Синхронный D – триггер и JK – триггер.

Синхронный D – триггер

Структурная схема D-триггера (а) и его условное обозначение (б) приведены на рис.7.4.7.

D |

|

|

|

Q |

|

|

|

Q |

|||

|

|

S |

|

D |

|

||||||

|

|

|

|

||||||||

|

|

С |

|

|

С Т |

Q |

|

Т |

Q |

||

|

|

|

|

|

|

||||||

|

|

|

|

|

R |

|

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а) |

|

|

|

|

б) |

|

||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|||

Рис.7.4.7. Структурная схема синхронного D-триггера (а) и его условное обозначение (б).

Триггер управляется единственным сигналом, поступающим на его вход D. Благодаря инвертору запрещенное соотношение сигналов невозможно на входах R и S. Таблица истинности синхронного D-триггера приведена на рис.7.4.8. Стрелка направленная вверх показывает, что срабатывание D-триггера происходит по перепаду тактового импульса от низкого уровня к высокому, т.е. по положительному фронту тактового импульса.

D-триггер еще называют триггером с задержкой. Информационный сигнал, поступающий на вход триггера задерживается на один такт (период следования тактовых импульсов), прежде чем появиться на выходе.

Режим |

Qn+1 |

|

|

|

работыCDQn+1Установка1110Установка 0001

Рис.7.4.8. Таблица истинности синхронного D-триггера.

JK – триггер

В этом триггере устранена неопределенность, имеющая место в RS-триггере при подаче на входы R и S уровней логической единицы. JK-триггер можно получить из

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

с |

|

|

Q |

|

|

Q |

|

|

|

Q |

||||||

J |

|

|

|

|

|

|

|

|

|

J |

||||||||||||

|

|

|

S |

Т |

|

|

|

|

|

S |

Т |

|

|

|

|

|

||||||

С |

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

С ТТ |

|

|

|

|||

|

|

|

С |

|

|

Q |

|

|

|

С |

|

Q |

|

|

Q |

|||||||

|

|

|

|

|

|

|

|

|||||||||||||||

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K |

|

|

|

|||

|

|

& |

|

|

|

о |

|

|

|

|

|

|

R |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

в |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

к |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

б) |

|

|

|

|

|

|

|

|

|

|

0а) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

S

Рис.7.4.10.Структурная схема JK-триггера (а) и его условное изображение (б).

двухтактного RS-триггера.

Для этого на входе главного триггера нужно иметь два S и два R входа и связать дополнительные входы крест накрест с выходами вспомогательного триггера. Структурная схема JK-триггера (а) и его условное изображение (б) приведены на рис.4.7.10, а таблица истинности на рис.7.4.11.

Режим

работыСJKQХранения100QУстановк а 010101Установка 111010Переключения111Q

Рис.7.4.11. Таблица истинности JK-триггера.

В JK-триггерах имеются дополнительные входы: очистки и предустановки. Они позволяют устанавливать триггер в требуемое начальное состояние. В единичное начальное состояние триггер устанавливается подачей логической единицы в виде импульсного сигнала на вход предустановки и остается в этом состоянии после окончания действия импульса. В состояние нуля триггер устанавливается подачей логической единицы в виде импульса на вход очистки.

Билет 75. Последовательные регистры сдвига. Параллельный

кольцевой регистр сдвига.

Последовательные регистры сдвига.

Структурные схемы четырехразрядного последовательного регистра сдвига на JK-транзисторах (а) и D-транзисторах (б) приведены на рис.7.4.12.

Вх |

|

|

|

|

|

|

|

||||

|

|

J |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

||

Са) |

|

|

|

|

|

С |

ТТ |

||||

|

|

|

|

|

|||||||

|

|

|

|

|

K |

|

|

|

|||

С |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

Q3 |

|||||

|

|

|

|

|

|

||||||

|

|

|

|

||||||||

Вх |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|||||

б) |

D |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|||||

С |

С |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

Q0 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J |

|

|

|

|

|

|

|

|

|

|

J |

|

|

|

|

|

|

|

|

|

|

|

J |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

С |

ТТ |

|

|

|

|

С |

ТТ |

|

|

|

|

|

|

|

|

|

С |

ТТ |

|

|

|

|||||||||

Q |

|

|

Q |

|

|

|

Q |

|

|

Q |

|

||||||||||||||||||||||||

|

|

|

|

K |

|

|

|

|

|

|

|

K |

|

|

|

|

|

K |

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

Q0 |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

D |

|

|

|

|

|

|

|

|

|

|

D |

|

Т |

|

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

Т |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Т |

|

|

Q |

|

|

|

|||

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

С |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.7.4.12. Структурные схемы четырехразрядных последовательных регистров сдвига.

Параллельный кольцевой регистр сдвига.

Структурная схема параллельного кольцевого регистра приведена на рис.7.4.13