Лекция 34

21.2. Триггеры в интегральном исполнении

Интегральная технология и использование методов алгебры логики позволили создать большое чисто различных триггеров на базе логических элементов, различающихся структурой цепей управления и режимами работы. Триггер состоит из цепей управления и запоминающих устройств и имеет один, два (или более) входа и два выхода. Каждый из входов имеет определенное функциональное назначение, которое отражается в обозначении данного входа (R, S, К, D и т. д.). Цепи управления, в которые поступают входные (информационные) сигналы, преобразуют их в сигналы для запоминания и считывания.

Запоминающие

устройства

состоят из двух плеч, в каждом из которых

одновременно хранятся сколь угодно

долго два сигнала, один из которых

соответствует логической 1, другой —

логическому 0. Выход триггера Q, с которого

в исходном состоянии снимается высокий

потенциал, обычно называют прямым,

другой — инверсным

(обозначается

![]() ).

).

В зависимости от выполняемых функций различают триггеры с раздельным запуском (RС-триггер), со счетным запуском (T-триггер), с элементами задержки или логическими переключающими схемами в цепях управления (D-триггер), универсальные (JK-триггеры), на базе которых могут быть реализованы остальные типы триггеров.

По способу записи информации все триггеры подразделяют на асинхронные, в которых информация записывается непосредственно при поступлении входного сигнала, и тактируемые (синхронные), записывающие входную информацию только при поступлении разрешающего тактового импульса.

Названия триггеров составляют из типов входов. Синхронные триггеры бывают со статическими и динамическими входами. Динамическим называют такой вход, действие поданных уровней сигналов на который прекращается после соответствующего переключения триггера. Рассмотрим примеры построения некоторых типов триггеров на базе логических элементов либо ИЛИ — НЕ, либо И — НЕ.

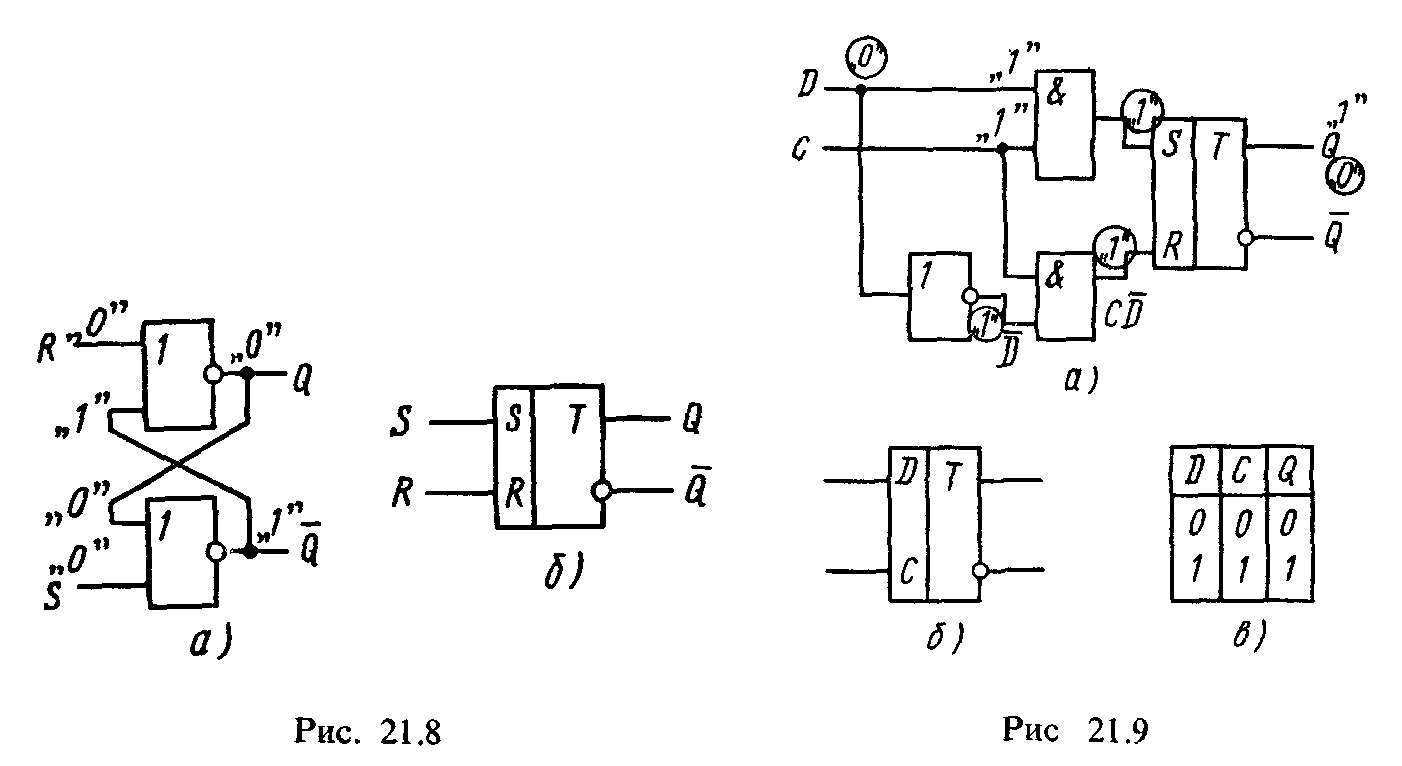

RS-триггер. Буквы R и S означают: R —раздельный вход установки в состояние 0, S — раздельный вход установки в состояние 1. Логические нули и единицы на рисунках обозначены цифрами в кавычках: «0», «1».

Схема асинхронного

RS-триггера

на двух логических элементах ИЛИ —

НЕ показана на рис. 21.8,а, на рис. 21.8,б дано

его условное обозначение в схемах.

Триггер имеет два прямых входа R и S и

два выхода: прямой Q и инверсный

![]() .

Перекрестная связь выхода каждого

элемента ИЛИ — НЕ со входом другого

обеспечивает схеме два устой- чивых

состояния. Предположим, что на входах

R и S действуют уровни логического 0,

не влияющие на состояние триггера.

Примем для опре- деленности, что на

прямом выходе триггера Q имеет место

уровень логического 0. Этот сигнал

совместно с нулевым уровнем на входе S

образуют на инверсном выходе

.

Перекрестная связь выхода каждого

элемента ИЛИ — НЕ со входом другого

обеспечивает схеме два устой- чивых

состояния. Предположим, что на входах

R и S действуют уровни логического 0,

не влияющие на состояние триггера.

Примем для опре- деленности, что на

прямом выходе триггера Q имеет место

уровень логического 0. Этот сигнал

совместно с нулевым уровнем на входе S

образуют на инверсном выходе![]() триггера уровень логической 1.

триггера уровень логической 1.

Уровень логической 1, в свою очередь, формирует совместно с 0 на входе R на прямом выходе Q уровень логического 0. Это устойчивое состояние триггера называют нулевым по уровню на прямом выходе.

Переключают триггер

подачей на один из входов сигнала

логической 1, при подаче на вход R

уровня 1, а на вход S уровня 0 на инверсном

выходе устанавливается сигнал

![]() = 0, который переводит триггер в состояние

1, соответствующее

= 0, который переводит триггер в состояние

1, соответствующее![]() Аналогично

происходит переключение триггера и при

подаче уровня логической единицы на

вход S.

Аналогично

происходит переключение триггера и при

подаче уровня логической единицы на

вход S.

Для RS-триггера существует запретная комбинация входных сигналов. Триггер теряет свойства (его состояние становится неопределенным) при одновременной подаче на входы R и S уровня логической 1. Если отпирающие импульсы действуют одновременно, то триггер оказывается временно в симметричном состоянии, из которого он может выйти равновероятно в любое из двух устойчивых состояний. Таким образом, результат неоднозначный, что недопустимо.

В схеме рис. 21.8, а элементы ИЛИ — НЕ могут быть заменены элементами И — НЕ. Свойства триггера при этом сохраняются, но управление им должно производиться уровнями логического 0. Такой триггер можно рассматривать как RS-триггер с инверсными входами. Более сложные триггеры D-, Т- и JK-типов выполняют на базе одного или двух RS-триггеров с использованием в цепях управления элементов задержки или логических переключающих схем. Наибольшее распространение получили триггеры с логическими переключающими схемами в цепях управления, поскольку интегральное исполнение элементов задержки затруднено.

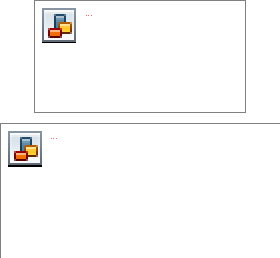

D-триггер.

Схема синхронного D-триггера приведена

на рис. 21.9, а, на рис. 21.9,б показано его

условное обозначение в схемах. D-триггер

имеет один информационный вход D,

устанавливающий триггер в состояние,

соответствующее логическому уровню на

этом входе. Вход С является исполнительным

управляющим, он служит для подачи на

вход синхронизирующего сигнала. Если

![]() триггер

сохраняет состояние, установленное

ранее. Триггер состоит из асинхронного

RS-триггера и логических переключающих

устройств на входах (одного элемента

НЕ и двух элементов И). На рис. 21.9,в дана

таблица истинности,

определяющая

функционирование триггера.

триггер

сохраняет состояние, установленное

ранее. Триггер состоит из асинхронного

RS-триггера и логических переключающих

устройств на входах (одного элемента

НЕ и двух элементов И). На рис. 21.9,в дана

таблица истинности,

определяющая

функционирование триггера.

______________

* Такая запись означает, что «на входе С логический нуль»; запись С = 1 означает, что «на входе С логическая единица».

Из нее видно, что при C=1 триггер устанавливается в состояние, определяемое логическим уровнем на входе D (при анализе состояний логических элементов схем на рис. 21.9 и 21.10 состояния входов и выходов для одного режима отмечены кружком, для другого режима — без кружка).

При

![]() на

выходах элементов И образуются уровни

0 для входов RS-триггеров. При

на

выходах элементов И образуются уровни

0 для входов RS-триггеров. При![]() и

на входе D = 1 уровень 1 будет на входе S

RS-триггера, а если на входе

и

на входе D = 1 уровень 1 будет на входе S

RS-триггера, а если на входе![]() то уровень 1 окажется на входе RRS-триггера.

Следовательно, D-триггер

принимает информацию с входа D, когда С

= 1, и может ее хранить до тех пор, пока

то уровень 1 окажется на входе RRS-триггера.

Следовательно, D-триггер

принимает информацию с входа D, когда С

= 1, и может ее хранить до тех пор, пока![]()

T-триггер. Буква Т означает, что триггер имеет счетный вход. Структура одной из схем T-триггера и его условное обозначение показаны на рис. 21.10,а,б соответственно. Триггер состоит из двух (А и Б) синхронных RS-триггеров, имеющих синхронизирующие входы С и один счетный вход Т, которым служит синхронизирующий вход С триггера А, а также содержит инвертор (НЕ), через который тактовый импульс подается на триггер Б. Триггер А называют ведущим, а триггер Б — ведомым.

В Т-триггере

осуществлена перекрестная обратная_связь:

с выхода Q триггера Б на вход R триггера

A

и с выхода

![]() триггера Б на вход S триггера А. Поступление

на вход Т уровня 1 обеспечивает перевод

триггера А в состояние, противоположное

предыдущему. Если Т = 0 и Q = 0, a

триггера Б на вход S триггера А. Поступление

на вход Т уровня 1 обеспечивает перевод

триггера А в состояние, противоположное

предыдущему. Если Т = 0 и Q = 0, a![]() = 1, то на выходах триггера А будут такие

же уровни, поскольку единичный уровень

сигнала на выходе инвертора обеспечивает

запись сигналов с выхода первого триггера

А во второй Б. При этом на входе S триггера

А будет 1, а на входе R — 0. Подача сигнала

1 наT

отключает триггер Б от А и обеспечивает

запись в него сигналов 1 на S и 0 на R.

= 1, то на выходах триггера А будут такие

же уровни, поскольку единичный уровень

сигнала на выходе инвертора обеспечивает

запись сигналов с выхода первого триггера

А во второй Б. При этом на входе S триггера

А будет 1, а на входе R — 0. Подача сигнала

1 наT

отключает триггер Б от А и обеспечивает

запись в него сигналов 1 на S и 0 на R.

И зменение

входного уровня на Т = 0 приводит к

отключению входов триггера А и запись

сигналов с его _выходов в триггер Б,

который переводится в состояние Q = l,

зменение

входного уровня на Т = 0 приводит к

отключению входов триггера А и запись

сигналов с его _выходов в триггер Б,

который переводится в состояние Q = l,![]() = 0, т. е. в состояние, противоположное

предыдущему.

= 0, т. е. в состояние, противоположное

предыдущему.

JК-тригтер. Это наиболее универсальный триггер. Структурная схема и условное обозначение одного из вариантов такого триггера показаны на рис. 21.11,a,б. Входы J и К задают состояния: J — триггер устанавливается в состояние 1, К — в состояние 0. Эти входы подобны входам R и S в триггере RS. JK - триггер имеет вход С (исполнительный синхронизирующий), поэтому триггер является синхронным, т. е. его выходные уровни устанавливаются только при поступлении тактовых импульсов С.

Входы R и S связаны с выходами перекрестными связями через две схемы И, на один из входов которых подаются управляющие уровни J и К. В JK-триггере допустимо подавать на входы J и К одинаковые сигналы (в отличие от RS-триггеров). Если на входы J и К поданы сигналы единицы (J = 1 и К = 1), схемы И превращаются в повторители для уровней, поданных на входы 1 и 2. В этом случае JK-триггер работает как T-триггер. При остальных наборах сигналов на входах J т К JK-триггер работает как RS-триггер, причем вход J соответствует входу S, а К — входу R.