Энциклопедия PC

.pdf736Глава12. Шинырасширения

тЗапросы вводятся по шине AD[31:0] и С/ВЕ[3:0] с помощью сигнала Р1РЕ#, по каждому фронту CLK мастер передает очередное двойное слово запроса вместе с кодом команды.

тЧерез внеполосные (sideband) линии адреса SBA[7:0]. «Внеполосность» означает, что эти сигналы используются независимо от занятости шины AD. Синхронизация подачи запросов зависит от режима (1х, 2х или 4х).

В ответ на полученные команды порт AGP выполняет передачи данных, причем фаза данных AGP явно не привязана к фазе команды/адреса. Фазы данных вводит порт AGP (системная логика), исходя из порядка ранее пришедших к нему команд от акселератора. Акселератор узнает лишь тип и приоритет команды, результаты которой последуют в данной транзакции. Какую именно команду из очереди отрабатывает порт, акселератор определяет сам, так как именно он ставил их в очередь (ему известен порядок). Никаких тегов транзакций (как, например, в системной шине процессоров Р6) в интерфейсе AGP нет. Имеются только четыре независимых очереди для каждого типа команд (чтение низкоприоритетное, чтение высокоприоритетное, запись низкоприоритетная, запись высокоприоритетная). Фазы исполнения команд разных очередей могут чередоваться произвольным образом; порт имеет право исполнять их в порядке, оптимальном с точки зрения производительности. Реальный порядок исполнения команд (чтения и записи памяти) тоже может изменяться. Однако для каждой очереди порядок выполнения всегда совпадает с порядком подачи команд (об этом знают и акселератор, и порт).

Запросы AGP с высоким приоритетом для арбитра системной логики являются более приоритетными, чем запросы от центрального процессора и мастеров шины PCI. Запросы AGP с низким приоритетом для арбитра имеют приоритет ниже, чем от процессора, но выше, чем от остальных мастеров. Хотя принятый протокол никак явно не ограничивает глубину очередей, спецификация AGP формально ее ограничивает до 256 запросов. На этапе конфигурирования устройства система РпР устанавливает реальное ограничение (в конфигурационном регистре акселератора) в соответствии с его возможностями и возможностями системной платы. Программы, работающие с акселератором (исполняемые и локальным, и центральным процессорами), не должны допускать превышения числа необслуженных команд в очереди (у них для этого имеется вся необходимая информация).

При передаче данных AGP управляющие сигналы, заимствованные от PCI, имеют почти такое же назначение, что и в PCI. Передача данных AGP в режиме 1х очень похожа на циклы PCI, но немного упрощена процедура квитирования (поскольку это выделенный порт и обмен выполняется только с быстрым контроллером системной памяти). В режимах 2х и 4х имеется специфика стробирования.

ж В режиме 1х данные (4 байта на AD[31:0]) фиксируются получателем по положительному перепаду каждого такта CLK, что обеспечивает пиковую пропускную способность 66,6 х 4 = 266 Мбайт/с.

т В режиме 2х используются стробы данных AD_STBO и AD_STB1 для линий AD[0:15] иAD[16:31] соответственно. Стробыформируютсяисточникомдан-

12.6. МагистральныйинтерфейсAGP 737

ных, приемник фиксирует данные и по спаду, и по фронту строба. Частота стробов совпадает с частотой CLK, что и обеспечивает пиковую пропускную способность 66,6 х 2 х 4 - 533 Мбайт/с.

•В режиме 4х используются еще и дополнительные (инверсные) стробы AD_STBO# иAD_STB1#. Данныефиксируютсяпоспадамипрямых, иинверсных стробов. Частота стробов в два раза выше, чем CLK, что и обеспечивает пиковую пропускную способность 66,6 х 2 х 2 х 4 = 1066 Мбайт/с.

Конфигурирование устройств с интерфейсом AGP выполняется так же, как и обычных устройств PCI, — через обращения к регистрам конфигурационного пространства (см. п. 12.5.10). В процессе инициализации процедура POST только распределяет системные ресурсы, но операции AGP оставляет запрещенными. Работу AGP разрешает загруженная ОС, предварительно установив требуемые параметры AGP: режим обмена, поддержку быстрой записи, адресации свыше 4 Гбайт, способ подачи и допустимое число запросов. Для этого возможности устройств считываются из регистра состояния AGP, а согласованные параметры записываются в регистр команд AGP, расположенный в конфигурационном пространстве. Параметрынастройкипортазадаютсячерезконфигурационныерегистры чипсетасистемнойплаты(главногомоста).

Регистр состояния AGP сообщает свойства порта: допустимое число запросов в очередях, поддержку внеполосной адресации, быстрой записи, адресации свыше 4 Гбайт, режимы 1х, 2х, 4х. Регистр команд AGP служит для разрешения этих свойств.

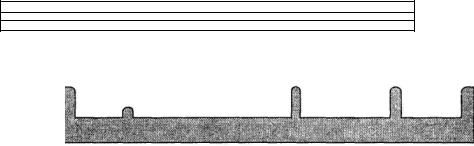

Графический адаптер с интерфейсом AGP может быть встроен в системную плату, а может располагаться и на карте расширения, установленной в слот AGP. Внешне карты с портом AGP похожи на PCI (рис. 2.7), но у них используется разъем повышенной плотности с «двухэтажным» (как у EISA) расположением ламелей. Сам разъем располагается дальше от задней кромки платы, чем разъем

PCI.

|

|

|

|

|

|

|

|

|

|

|

|

|

ш |

а1 |

*- «о |

сосоm |

|

|

|

||||

|

|

|

|||

|

2 3 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S 1

ш

Рис. 12.7. СлотыAGP: з— 3,3 В; б— 1,5 В; в— универсальные

Порт AGP может использовать два возможных номинала питания интерфейсных схем: 3,3 Ви 1,5 В(длясигналов RST# и CLK всегда используются

738 Глава12. Шинырасширения

уровни 3,3 В). Снижение напряжения питания буферных схем позволяет повысить достижимую частоту переключений. Для режимов 1х и 2х может использоваться любойизноминаловпитаниябуферов, длярежима4х— только1,5 В.

ПоуровнюпитаниябуферовкартыипортыAGP могутбытьтрехтипов: 3,3 В, 1,5

Ви универсальные, причем имеются механические ключи, предотвращающие ошибочные подключения. Слот и карта 3,3 В имеют ключи на месте контактов 2225 (перегородка в слоте, см. рис. 12.7, а, вырез на разъеме карты); слот и карта 1,5

В— на месте контактов 42-45. Универсальный слот не имеет перегородок, а универсальная карта имеет оба выреза. Универсальная системная плата узнает о номинале питания буферов установленной карты по сигналу TYPEDET* — на картах 3,3 В контакт свободен, на картах Г,5 В и универсальных — заземлен. Универсальная карта узнает о номинале питания буферов по уровню напряжения на контактах Vddq, который будет 3,3 или 1,5 В. Таким образом и обеспечивается согласование.

Назначение контактов слота AGP приведено в табл. 12.4, в позициях ключей через дробь указано назначение для карт 3,3/1,5 В. На универсальном слоте будут присутствовать все эти цепи, на универсальных картах все цепи, назначенные ключам, отсутствуют. Из-за двух ключей на универсальной карте теряется пара контактов для подачи питания VCC3.3, и их остается только четыре, что ограничивает потребляемый ток (допустимый ток для каждого контакта — 1А). На универсальной карте также нет дополнительного питания З.ЗУаих, используемого дляпитания цепей формирования сигнала РМЕ# в режиме «сна».

Таблица12.4. СигналыпортаAGP

РЯДА |

№ |

Ряд В |

РЯДА |

№ |

Ряд В |

|

OVRCNT* |

1 |

12V |

SBA4 |

20 |

SBA5 |

|

5.0V |

2 |

TYPEDET* |

SBA6 |

21 |

SBA7 |

|

5.0V |

3 |

Резерв |

Ключ 3,3 В/резерв |

22 |

Ключ3,3 |

В/резерв |

USB+ |

4 |

USB- |

Ключ3,3 B/GND |

23 |

Ключ3,3 |

B/GND |

GND |

5 |

GND |

Ключ 3,3 B/3.3Vaux |

24 |

Ключ3,3 |

В/резерв |

INTB# |

6 |

INTA# |

Ключ 3,3 B/3.3Vaux |

25 |

Ключ3,3 |

B/VCC3.3 |

CLK |

7 |

RST# |

AD31 |

26 |

AD30 |

|

REQ# |

8 |

GNT# |

AD29 |

27 |

AD28 |

|

VCC3.3 |

9 |

VCC3.3 |

VCC3.3 |

28 |

VCC3.3 |

|

STO |

10 |

ST1 |

AD27 |

29 |

AD26 |

|

ST2 |

11 |

Резерв |

AD25 |

30 |

AD24 |

|

RBF# |

12 |

PIPE* |

GND |

31 |

GND |

|

GND |

13 |

GND |

AD_STB1 |

32 |

AD_STBl#l |

|

Резерв |

14 |

Резерв |

AD23 |

33 |

С/ВЕЗ* |

|

SBAO |

15 |

SBA1 |

Vddq |

34 |

Vddq |

|

VCC3.3 |

16 |

VCC3.3 |

AD21 |

35 |

AD22 |

|

SBA2 |

17 |

SBA3 |

AD19 |

36 |

AD20 |

|

SB_STB |

18 |

SB_STB#' |

GND |

37 |

GND |

|

GND |

19 |

GND |

AD17 |

38 |

А018Ряд |

AN |

12.6. МагистральныйинтерфейсAGP 739

РЯДА |

№ |

Ряд В |

РЯДА |

№ |

Ряд В |

С/ВЕ2* |

39 |

AD 16 |

AD14 |

53 |

AD13 |

Vddq |

40 |

Vddq |

AD12 |

54 |

AD11 |

IRDY# |

41 |

FRAME* |

GND |

55 |

GND |

З.ЗУаих/Ключ1,5 В |

42 |

Резерв/Ключ1,5 В |

AD10 |

56 |

AD9 |

GND/Ключ 1,5 В |

43 |

GND/Ключ 1,5 В |

ADS |

57 |

C/BEO* |

Резерв/Ключ1,5 В |

44 |

Резерв/Ключ1,5 В |

Vddq |

58 |

Vddq |

УССЗ.З/Ключ1,5 В |

45 |

VCC3.3/Kjno4 1,5 В |

AD STBO |

59 |

AD STBO#' |

DEVSEL* |

46 |

TRDY# |

AD7 |

60 |

AD6 |

Vddq3.3 |

47 |

STOP* |

GND |

61 |

GND |

PERR# |

48 |

РМЕ# |

ADS |

62 |

AD4 |

GND |

49 |

GND |

AD3 |

63 |

AD2 |

SERR# |

50 |

PAR |

Vddq |

64 |

Vddq |

C/BE1* |

51 |

AD15 |

AD1 |

65 |

ADO |

Vddq |

52 |

Vddq |

Vrefcg2 |

66 |

Vrefgc2 |

1Инверсныестробыотсутствуютнакартахислотах3,3 В(тамнетрежима4х).

2Опорноенапряжениенетребуетсядляслотовикарт1х.

Кроме собственно AGP в порте AGP заложены сигналы шипы USB, которую предполагается заводить в монитор (линии USB+, USB- и сигнал OVRCNT#, которым сообщается о перегрузке по току линии питания +5 В, выводимой в монитор).

Сигнал РМЕ# относится к интерфейсу управления энергопотреблением (Power Management Interface). При наличии дополнительного питания S.SVaux, этим сигналомкартаможетинициировать«пробуждение».

Спецификация AGP Pro описывает более мощный коннектор, позволяющий в четыре раза повысить мощность, подводимую к графической карте. При этом сохраняется односторонняя совместимость: карты AGP могут устанавливаться в слот AGP Pro, но не наоборот. Коннектор AGP Pro имеет дополнительные контакты с обеих сторон обычного коннектора AGP (рис. 12.8) для линий GND и питания 3,3 и 12 В. Для правильной установки обычной карты со стороны задней кромки системной платы дополнительная часть слота AGP Pro закрывается съемной пластмассовой заглушкой. Карта AGP Pro может также использовать 1-2 соседних слота PCI: чисто механически (как точки опоры и место), как дополнительныеконнекторыдляподачипитания, какфункциональныеконнекторыPCI.

Всовокупности карта AGP Pro может потреблять до 110 Вт мощности, забирая

еепо шинам питания 3,3 В (до 7,6 А) и 12 В (до 9,2 А) с основного разъема AGP, дополнительного разъема питания AGP Pro и одного-двух разъемов PCI. Карты AGP Pro большой мощности (High Power, 50-110 Вт) занимают два слота PCI, малой (Low Power, 25-50 Вт) — один слот. Соответственно скобка крепления к задней панели ПК у них имеет утроенную или удвоенную ширину. Кроме того, карты имеют крепеж к передней стенке ПК. На дополнительном разъеме цепь PRSNT1# служит признаком наличия карты (контакт заземлен), a PRSNT2# — признаком потребляемой мощности (до 50 Вт — контакт свободен, до 110 Вт — заземлен).

12.8. УстаревшиешиныPC 741

ция портов обеспечивает доступ ко всему пространству 64К портов. Интерфейс синхронизирован с шиной PCI, но устройства могут вводить произвольное число тактов ожидания. Интерфейс программно прозрачен — как и для ISA/X-Bus, не требует каких-либо драйверов. Контроллер интерфейса LPC является устройствоммостом PCI. По пропускной способности интерфейс практически эквивалентен этим шинам. В спецификации LPC 1.0 приводится расчет пропускной способности интерфейса и устройств, его использующих. При наличии буферов FIFO интерфейс наиболее выгодно использовать в режиме DMA. В этом случае главным потребителем будет LPT-порт — при скорости передачи данных 2 Мбайт/с он займет 47 % полосы интерфейса. Следующим будет инфракрасный порт 4 Мбит/с (11,4 %). Остальным устройствам (контроллер НГМД, СОМ-порт, аудиокодек) требуются еще меньшие доли, в результате они занимают до 75 % полосы при одновременной работе. Таким образом, перевод этих устройств с ISA/X-Bus на LPC не должен вызывать проблем производительности, более острых, чем были на старых шинах.

Электрический интерфейс для сигналов LAD[3:0], LFRAME#, LDRQ# и SERIRQ соответствует спецификации PCI 2.1 для питания 3,3 В. Остальные сигналы, в зависимости от системной платы, могут быть суровнями как5 В, так и 3,3 В.

Конфигурирование устройств LPC не предусматривает использования протоколов PCI или ISA PnP, поскольку все устройства LPC известны системной BIOS. Для обращения к устройствам LPC хост должен декодировать их адреса и направлять обращения по ним на контроллер LPC.

12.8.УстаревшиешиныPC

Вэтом разделе «помянем» шины PC, оставшиеся в прошлом веке, — МСА и VLB. Несколько более подробная информация о них была в первом издании энциклопедии [1] и в справочнике [4]. Шину ISA списывать рано — даже изживаемая из настольных ПК, она еще послужит в простых инструментальных и промышленныхкомпьютерах.

12.8.1.ШинаМСА

MCA (MicroChannel Architecture) — микроканальная архитектура — была введена фирмой IBM для своих компьютеров PS/2, начиная с модели 50. Шина МСА абсолютно несовместима с ISA/EISA. Состав управляющих сигналов, протокол и архитектура ориентированы на асинхронное функционирование шины и процессора, что снимает проблемы согласования скоростей процессора и ПУ. Архитектура позволяет эффективно и автоматически конфигурировать все устройства программным путем (в картах МСА нет ни одного переключателя). При всей прогрессивности архитектуры МСА не пользовалась популярностью, в частности, из-за своей закрытости и полной несовместимости с открытой архитектурой ISA. MCA находила применение в мощных файл-серверах, где требуется высоконадежный производительный ввод-вывод. Однако сейчас ее практически вытеснила шина PCI.

742Глава12. Шинырасширения

2.8.2.ЛокальнаяшинаVLB

Шины ввода-вывода ISA, MCA, EISA имеют низкую производительность, обусловленную их ролью в структуре PC. Одним из решений проблемы повышения пропускной способности было применение локальной шины процессора 486 для подключения периферии (контроллера дисков и графического адаптера). VLB (VESA Local Bus) — стандартизованная 32-битная локальная шина, практически представляющая собой набор сигналов системной шины процессора 486, выведенных на дополнительные разъемы системной платы. Для процессоров Pentium была принята спецификация 2.0, в которой разрядность шины данных увеличена до 64, но она распространения не получила.

VLB-слот является расширением системного слота шины ISA-16, EISA или MCA, располагаясь позади него вблизи от процессора. Из-за ограниченной нагрузочной способности шины процессора больше трех слотов VLB на системной плате не устанавливают. Максимальная тактовая частота шины — 66 МГц, хотя шина работает надежнее на частоте 33 МГц. Декларируется пиковая пропускная способность 132 Мбайт/с (33 МГц х 4 байта), но она достигается только при пакетнойпередаче.

Жесткие требования к временным характеристикам процессорной шины при большой нагрузке (со стороны микросхем внешнего кэша) могут привести к неустойчивой работе: все три VLB-слота работоспособны только на частоте 40 МГц. При нагруженной системной плате на 50 МГц может работать только один слот. Шина теоретически допускает применение активных (Bus-Master) адаптеров, но арбитраж запросов возлагается на сами адаптеры. Разрешена установка не более двух адаптеров Bus-Master, один из которых устанавливается в «Masters'-слот.

Встречаются системные платы, которые имеют встроенный графический и дисковый адаптер с шиной VLB, но самих слотов VLB нет. Это означает, что на плате установлены микросхемы указанных адаптеров для шины VLB. Такая неявная шина по производительности не уступает обычной, а с точки зрения надежности и совместимости она даже лучше.

12.9. Шиныикартырасширения блокнотныхПК

Портативные и блокнотные ПК поначалу строились безо всяких попыток унификации и обеспечения взаимозаменяемости компонентов, но со временем ситуация изменилась. Сейчас существует несколько основных интерфейсов и конструктивов дляустройстврасширения, наиболеепопулярныеприведенывтабл. 12.5.

Первый стандарт накарты расширения назывался PCMCIA. Впоследствии он былпереименованвPC Card.

Для карт памяти (динамической, статической, постоянной и флэш-памяти) существуют стандарты Miniature Card и SmartMedia Card, поддерживаемые ас-

социацией PCMCIA, а также MultiMedia Card и CompactFlash (CFA — Compact Flash Association). Карта Miniature Card через переходный адаптер может устанавливатьсявслотPC Card типа2.

12.9. ШиныикартырасширенияблокнотныхПК 743

Таблица12.5. КонструктивыиинтерфейсыперифериипортативныхПК

|

PC Card |

Small PC |

Compact |

Smart |

Miniature |

Multi Media |

|

|

Card |

Flash |

MediaCard |

Card |

Card |

|

|

|

|

|

|

|

Длина, мм |

85,6 |

45,0 |

36,0 |

45,0 |

33,0 |

32,0 |

Ширина, мм |

54,0 |

42,8 |

43,0 |

37,0 |

38,0 |

24,0 |

Высота, мм |

3,3/5,0/ 10,5 |

3,3/5,0/ 10,5 |

3,3/5,0 |

0,76 |

3,5 |

1,4 |

|

|

|

|

|

|

|

Коннектор |

Штырьковый Штырьковый |

Штырь- |

Печатный |

Эластомер |

Печатный |

|

|

|

|

ковый |

|

|

|

Числоконтактов |

68 |

68 |

50 |

22 |

60 |

7 |

Интерфейсы |

Память, |

Память, ввод- |

Память, |

Память |

Память |

Память |

|

ввод-вывод, |

вывод |

ввод-вывод |

(Flash, |

(DRAM, |

(Flash, ROM) |

|

CardBus |

|

|

ROM) |

Flash, ROM) |

|

|

|

|

|

|

|

|

12.9.1.ИнтерфейсыPCMCIA, PC Card иCardBus

Вначале 90-х годов организация PCMCIA (Personal Computer Memory Card International Association — международная ассоциация производителей карт памяти для персональных компьютеров) начала работы по стандартизации шин расширения блокнотных компьютеров, в первую очередь предназначенных для расширения памяти. Первым появился стандарт PCMCIA Standard Release 1.0/ JEIDA 4.0 (июнь 1990 г.), в котором был описан 68-контактный интерфейс и два типоразмера карт: Туре I и Туре II PC Card. Поначалу стандарт касался электрических и физических требований только для карт памяти. Был введен метафор-мат информационной структуры карты CIS (Card Information Structure), в которой описываются характеристики и возможности карты — ключевой элемент - взаимозаменяемостикартиобеспечениявозможностейРпР.

Следующая версия PCMCIA 2.0 (1991 г.) для того же разъема определила интерфейс операций ввода-вывода, двойное питание для карт памяти, а также методики тестирования. В версии 2.01 была добавлена спецификация PC CardATA, новый типоразмер Туре III, спецификация автоиндексируемой массовой памяти AIMS (Auto-Indexing Mass Storage) и начальный вариант сервисной спецификации

(Card Services Specification). В версии 2.1 (1994 г.) расширили спецификации сервисов карт и сокетов (Card and Socket Services Specificaiton) и развили структуру CIS.

Стандарт PC Card (1995 г.) явился продолжением предыдущих, в нем введены дополнительные требования для улучшения совместимости и новые возможности: питание 3,3 В, поддержка DMA и 32-битного режима прямого управления шиной

CardBus.

В дальнейшем в стандарт были введены и другие дополнительные возможности.

Все карты PCMCIA и PC Card имеют 68-контактный разъем, назначение контактов у которого варьируется в зависимости от типа интерфейса карты. Тип интерфейса «заказывается» картой при установке ее в слот, который, естественно, должен поддерживать требуемый интерфейс. Интерфейс памяти обеспечи-

744 Глава12. Шинырасширения

вает 8- и 16-битные обращения с минимальным временем цикла 100 не, что обеспечивает максимальную производительность 10 и 20 Мбайт/с соответственно. Интерфейс ввода-вывода имеет минимальную длительность цикла 255 не, что соответствует 3,92/7,84 Мбайт/с для 8/16-битных обращений. Интерфейс CardBus поддерживает практически такой же протокол обмена, что и PCI, но с некоторыми упрощениями. Тактовая частота 33 МГц и разрядность 32 бита обеспечивают пиковую пропускную способность в пакетном цикле до 132 Мбайт/с, картам предоставляется возможность прямого управления шиной (bus mastering). Здесь используется та же система автоматического конфигурирования, что и в PCI (через регистры конфигурационного пространства). В интерфейс заложены дополнительные возможности для цифровой передачи аудиосигнала, причем как в традиционнойформеИКМ, такивновой(забытойстарой) формеШИМ(PWM).

Для дисковых устройств АТА в формате PC Card имеется специальная спецификацияинтерфейса(см. п. 13.1.1).

Различают четыре типа PC Card, у них у всех размер в плане 54 х 85,5 мм, но разная толщина (меньшие адаптеры встают в большие гнезда):

ж PC Card Type I — 3,3 мм— картыпамяти;

«к PC Card Type II — 5 мм— картыустройствввода-вывода, модемы, адаптерылокальныхсетей; » PC Card Type III — 10,5 мм— дисковыеустройства хранения;

*PC Card Type IV — 16 мм, правда, упоминания об этом типе на сайте www.pc-card.com найтинеудалось.

Есть еще и маленькие карты Small PC Card размером 45 х 42,8 мм с тем же коннекторомитемижетипамипотолщине.

Слоты PC Card могут предоставлять возможность прямого доступа к памяти (DMA). Реализация DMA — самый дешевый способ разгрузки процессора, но такая реализация имеется не на всех хостах, а только на простых, основанных на шине ISA. Для систем с шиной PCI более естественно прямое управление шиной CardBus, правда, длякартреализацияпрямогоуправленияобходитсянедешево.

Для мультимедийных карт имеется возможность переключения интерфейса в специальный режим ZV Port (Zoomed Video), в котором организуется отдельный двухточечный интерфейс передачи данных между картой и хост-системой. По смыслу интерфейс напоминает коннектор VFC графических карт — выделенная шина для передачи видеоданных, не связанная с остальными шинами (и не загружающая их), но имеет иной протокол. В режиме ZV Port адресные линии А[25:4], а также линии BVD2/SPKR#, INPACK* иIOIS16* получают иное назначение и по ним передаются видеоданные и четыре цифровых аудиоканала. Для обычного интерфейса остаются лишь четыре адресные линии, позволяющие адресоваться к 16 байтам общей памяти иатрибутов карты.

Интерфейс порта ZV соответствует временным диаграммам CCIR601, что позволяет декодеру NTS С в реальном времени доставлять видеоданные с карты в экранный буфер VGA. Видеоданные могут поступать на карту как с внешнего видеовхода, так ис декодера MPEG.

Карты имеют специальное выделенное пространство памяти атрибутов, в котором находятся конфигурационные и управляющие регистры карты, предна-

12.9. ШиныикартырасширенияблокнотныхПК 745

значенные для автоконфигурирования. Стандартом описан формат информационной структуры карты (CIS — Card Information Structure). Карты могут быть многофункциональными (например, комбинация модемаи сетевого адаптера). В спецификации MFPC (Multiple Function PC Cards) для каждой функции предусматриваются отдельные конфигурационные регистры и определяются правила разделяемогоиспользованиялиниизапросапрерывания.

Дляустройстввнешнейпамятистандартописываетформатыхраненияданных, совместимые с FAT MS-DOS, а также ориентированные на флэш-память как основнойносительинформации. ДлянепосредственногоисполнениямодулейПО, хранящихся в ПЗУ карты, имеется спецификация XIP (eXecute In Place), описывающая программный интерфейс вызова этих модулей (вместо загрузки ПОвОЗУ).

Стандарт описывает программный интерфейс сервисов карт (Card Services), обеспечивающий унификацию взаимодействия его клиентов (драйверов, прикладного ПО и утилит) с устройствами. Имеется также и интерфейс сервисов сокета (Socket Services), с помощью которого выполняются операции, связанные с обнаружением фактов подключения-отключения карт, их идентификации, конфигурированияпитанияиаппаратногоинтерфейса.

В стандарте имеются описания специфических особенностей, свойственных двуморганизациям, ведущимстандартPC Card.

жPCMCIA описывает автоиндексируемую массовую память (AIMS) для хранения больших массивов данных (изображений, мультимедийных данных) на блочно-ориентированных устройствах. Имеется также специфи- кация15-контактногоэкранированногоразъемадляподключениямодемов и адаптеров локальной сети (15-pin Shielded Modem I/O connector) и 7-

контактногодляподключениямодемов(7-pin Modem I/O connector).

жJEDIA длякартпамятипредлагаетформатфайловSmall Block Flash Format, упрощающий файловую систему. Формат SISRIF (Still Image, Sound and Related Information Format) предназначен для записи изображений и звука накартыпамяти. Имеетсяиспецификациядлякартдинамическойпамяти.

Большинство адаптеров выпускается с поддержкой РпР и предусматривает «горячее» подключение — интерфейсные карты могут вставляться и выниматься без выключения компьютера. Для этого контакты шин питания имеют большую длину, чем сигнальные, обеспечивая их упреждающее подключение и запаздывающее отключение. Два контакта обнаружения карты CD1# и CD2# (Card Detect) корочеостальных— ихзамыканиедляхостаозначает, чтокартаполностью вставлена в слот. Несмотря на возможность динамического конфигурирования, в некоторыхслучаяхприизмененииконфигурациитребуетсяперезагрузкасистемы.

Первоначально карты и хост-системы использовали напряжение питания логики +5 В. Для перехода на низковольтное питание (3,3 В) был введен механическийключ, недопускающийустановкикартына3,3 Ввслот, дающийтолько5 В. Крометого, былиопределеныконтактыдлявыборапитающегонапряжения. По этим линиям хост, допускающий и карты 3,3 В, определяет потребности установленнойкартыиподключаетсоответствующеенапряжениепитания. Если