Энциклопедия PC

.pdf726 Глава12. Шинырасширения

Шина PCI имеет и другие конструктивные исполнения, их спецификации доступны на сайте www.pcisig.org (правда, только для членов данной организации либо за деньги).

Small PCI (SPCI) — спецификация PCI в миниатюрном исполнении, прежде называвшаяся SFF PCI (Small Form-Factor). Эта спецификация, предназначенная в основном для портативных компьютеров логически совпадает с обычной шиной PCI. Шина 32-битная, 64-битное расширение не предусматривается, и при частоте 33 МГц обеспечивается пропускная способность 132 Мбайт/с. Как и на всех шинах PCI, здесь поддерживается прямое управление (bus mastering). В дополнение к обычному набору сигналов появился новый CLKRUN, с помощью которого хост и устройства могут управлять частотой синхронизации в интересах энергосбережения. По размерам карта SPCI совпадает с PC Card и Card Bus, но специальные ключи предотвращают ошибки подключения. Шина SPCI является внутренней (карты расширения находятся под крышкой корпуса и устанавливаются изготовителем при выключенном питании) и поэтому не нацелена на замену Card BUS (шина для внешних подключений с возможностью горячей замены). Карты SPCI могут быть трех видов: с питанием 5 В, 3,3 В и универсальные 5/3,3 В. Благодаря уменьшению размеров (длины проводников) понижены требования к мощности сигналов. Карты SPCI позволяют использовать преимущества модульных решений (можно разгрузить системную плату), обеспечивая высокую производительность обмена (чего не обеспечивает Card Bus).

Mini PCI Specification — вариант шины PCI, ориентированной лишь на 32битную часть (без сигналов JTAG), с меньшими габаритами карт расширения. Логически и электрически соответствует PCI, дополнительно используя сигнал CLKRUN для снижения энергопотребления. Имеет дополнительные сигналы для аудиоивидеоприменений.

PCI-X — спецификация шины с высокой пропускной способностью, достигающей 1 Гбайт/с. Разработана с учетом совместимости шины со старыми устройствами и новыми устройствами с обычной шиной PCI, для чего при наличии в системе хоть одного из «тихоходных» компонентов частота понижается до обычных 66 или 33 МГц.

Для устройств промышленного назначения в начале 1995 года был принят стандарт Compact PCI. Шина Compact PCI (cPCI) разрабатывалась на основе спецификации PCI 2.1. Этот стандарт принят организацией производителей про-

мышленных компьютеров PCIMG (PCI Industrial Computer Manufacturers Group).

Шина отличается большим количеством поддерживаемых слотов: 8 против 4. Конструктивно платы Compact PCI представляют собой еврокарты высотой 3U (100 х 160 мм) с одним коннектором (J1) или 6U (233 х 160 мм) с двумя коннекторами (J1 и J2). Коннекторы — 7-рядные штырьковые разъемы с шагом 2 мм между контактами, на кросс-плате — вилка, на модулях— розетки.

На базе шины Compact PCI фирмой National Instruments разработана спецификация PXI (PCI extensions for Instrumentation — расширение PCI для инстру-

ментальных систем) в тех же конструктивах. В шине PXI часть контактов, определенных в Compact PCI как свободные, предназначаются для дополнительных шин. Модули PXI совместимы с шиной Compact PCI, и модули Compact PCI — с шиной PXI. Однако все преимущества спецификации реализуются только при установке модулей PXI в шину PXI.

12.5. ШинаPCI 727

12.5.8. МостыPCI

Для соединения шины PCI с другими шинами и между собой применяются специальные аппаратные средства — мосты PCI (PCI Bridge). Главный мост (Host Bridge) используется дляподключенияPCI ксистемной шине(системной памяти и процессору), одноранговый мост (Peer-to-Peer Bridge) — для соединения двух шин PCI.

Соединения нескольких шин PCI характерно для серверов — таким образом увеличивают число подключаемых устройств. Мосты образуют иерархию шин, на вершине которой находится главная шина с нулевым номером. Главный мост чипсета системной платы может соединять центр (процессор и память) с несколькими равноранговыми шинами PCI, из которых условно главной будет шина с нулевым номером. Для подключения шин PCMCIA, CardBus, MCA, ISA/EISA, X- Bus и LPC используются специальные мосты, входящие в чипсеты системных плат или же являются отдельными устройствами PCI (микросхемами). Мосты выполняют преобразование интерфейсов соединяемых ими шин, синхронизацию и буферизацию обменов данных. Мосты (включая и мосты PCI-PCI) допускают различиечастотсинхронизациинасоединяемыхимишинах.

Каждый мост программируется — ему указываются диапазоны адресов в пространствах памяти и ввода-вывода, отведенные устройствам его шин. Если адрес ЦУ текущей транзакции на одной шине (стороне) моста относится к шине противоположной стороны, мост перенаправляет транзакцию на соответствующую шину и обеспечивает согласование протоколов шин. Таким образом, совокупность мостов PCI выполняет маршрутизацию (routing) обращений по связанным шинам. Считается, что устройство с конкретным адресом может присутствовать только на одной из шин, а на какой именно, «знают» запрограммированные мосты. Решать задачу маршрутизации призван также сигнал DEVSEL#. Обращения, не востребованные абонентами PCI, могут быть перенаправлены, например, на шину ISA/EISA.

С мостами связаны понятия позитивного и субтрактивного декодирования адресов. Рядовые агенты PCI (устройства и мосты) отзываются только на обращения по адресам, принадлежащим областям, описанным в их конфигурационном пространстве (через базовые адреса и диапазоны памяти или ввода-вывода). Такой способ декодирования называется позитивным (positive decoding). Мост с позитивным декодированием пропускает через себя только обращения, принадлежащие определенному списку, заданному в его конфигурационных регистрах.

Мост с субтрактивным декодированием (subtractive decoding) пропускает через себя обращения, не относящиеся к другим устройствам. Его области прозрачности формируются вычитанием (откуда и название) из общего пространства областей, описанных списком. Возможность субтрактивного декодирования имеется только у мостов определенного типа, и она является дополнением к позитивному декодированию.

Позитивное и субтрактивное декодирование относится только к обращениям, направленным в пространства памяти и ввода-вывода. Конфигурационные обращениямаршрутизируютсяспомощьюномерашины, передаваемоговциклахтипа1 (см. п. 12.5.2): каждыймост«знает» номеравсехшин, егоокружающих.

728 Глава12. Шинырасширения

На каждой шине PCI должно присутствовать центральное устройство, выполняющееследующиефункции:

и централизованныйарбитраж;

•«подтягивание» управляющихсигналовквысокомууровню; * субтрактивное декодирование адресов;

»генерацияконфигурационныхиспециальныхцикловпокомандампроцессора.

Эти функции, как правило, возлагаются на мост, соединяющий данную шину с более высокими уровнями иерархии шин PCI. Кроме выполнения этих функций, обслуживающих конкретную шину, мосты решают задачи оптимизации передачи данных между подсистемами компьютера, и от качества решения этих задач существеннозависитобщаяпроизводительность системы.

Одной из особенностей применения шины PCI с ее мостовыми соединениями является возможность действительно одновременного выполнения более одного обмена данными по непересекающимся путям — Concurrent PCI Transferring или PCI Concurrency. Например, во время взаимодействия процессора с памятью мастер шины PCI может обмениваться данными с другим устройством PCI. Этот пример одновременности обмена скорее теоретический, поскольку мастер шины PCI, как правило, обменивается данными с системной памятью. Более интересный случай — обмен графического адаптера, подключенного к порту AGP (родственнику PCI, см. п. 12.6), с памятью одновременно с обменом процессора с устройством PCI, или наоборот, загрузка данных процессором в графический адаптеродновременнособменоммеждумастеромшиныPCI исистемнойпамятью. Одновременность требует довольно сложной логики централизованного арбитража запросов всех агентов системы и различных ухищрений в буферизации данных. Одновременность реализуется не всеми чипсетами (в описаниях она всегда специальноподчеркивается) иможетбытьзапрещенанастройкамиCMOS Setup.

Для экономии полосы пропускания шины (уменьшения числа бесполезно занятых тактов) при обращениях к устройствам медленных шин (например, ISA) мост может выполнять отложенные транзакции (delayed transaction). Работает этот механизм следующим образом. Инициатор, расположенный на «быстрой» шине (это может быть и главный мост), обращается к ЦУ на медленной шине, выставляяадресикоманду, авкомандахзаписиещеиданные. Мостсохраняетэту информациювсвоихвнутреннихрегистрахи«отимениЦУ» отвечаетинициатору прекращениемтипа«повтор», чтовынуждаетинициаторбыстроосвободитьшину. Тем временем мост выполняет транзакцию с настоящим ЦУ и сохраняет у себя результат ее выполнения (для команд чтения это будут данные). Инициатор, получивший ответ «повтор», вынужден снова начать точно ту же транзакцию, и теперьнанеемостбыстроответитистиннымрезультатом, полученнымотЦУ. Вто время как мост выполняет длительную операцию обмена с медленным устройством, быстрая шина остается свободной для обслуживания других инициаторов.

Выделение специальных циклов чтения строк, множественного чтения и записисинвалидациейпозволяетконтроллерупамятипредпринятьопределенные

12.5. ШинаPCI 729

меры для оптимизации данных передач. Однако эти инструкции применяют только для обращений к памяти в «чистом виде» (имеющей свойство Prefetchable, см. п. 5.3.1). Когда инициатор обращается к источнику данных, отделенному мостом, командами чтения строки или множественного чтения, мост может считать из источника данных больше, чем инициатор заберет от него в данной транзакции. Однако в конце транзакции лишние данные в буфере моста проще всего аннулировать, поскольку до возможного последующего востребования в их реальном источнике они могут быть уже модифицированы. Более сложный мост может и отслеживать эти изменения, аннулируя лишь модифицированные данные. Обращения командами обычного чтения памяти разрешают мосту считать только точно затребованное количество данных. При этом возможности ускорения передач меньше, но не возникнет побочных эффектов от лишних чтений (чтение управляющих регистров, отображенных на память, может изменять их состояние).

Мосты могут выполнять задержку передачи записи в память (posted write),

инициированные на одной стороне и обращающиеся к целевому устройству на другой стороне. При этом данные принимаются в буферы моста, и для инициатора транзакция завершится раньше, чем данные дойдут до реального получателя. Мост начнет транзакцию их доставки в удобное для другой стороны время. Порядок и количество байт, переданных получателем, обязательно должны совпадать с соответствующими данными инициатора обмена. Кроме того, поддерживается сохранение порядка операций записи и чтения. Записи в порты ввода-вывода откладывать имеет право только главный мост, но только для транзакций, инициированных центральным процессором. Операции чтения, естественно, выполняютсясразу, посколькубезполученияданныхонибессмысленны.

Мосты могут преобразовывать транслируемые ими транзакции записи в память с целью оптимизации использования пропускной способности шины. Так, несколько последовательных транзакций записи могут объединяться в одну пакетную, в которой лишние записи могут блокироваться с помощью сигналов разрешения байтов. Так, например, последовательность одиночных записей двойных слов по адресам 0, 4, Ch может быть скомбинирована (write combining) в один пакет с начальным адресом 0, а во время третьей фазы данных (когда предполагается не требуемый адрес 8) все сигналы С/ВЕ[3:0]# пассивны. Записи отдельных байтов в определенных случаях могут быть объединены (byte merging) в одну транзакцию. Так, например, последовательность записей байтов по адресам 3, 1, 0 и 2 может быть объединена в одну запись двойного слова, поскольку эти байты принадлежат одному адресуемому двойному слову. Комбинирование и объединение могут работать независимо (объединенные транзакции могут комбинироваться), однако эти преобразования не изменяют порядок следования физических записей в устройства. Наличие этих возможностей не обязательно — оно зависит от «ловкости» мостов. Цель преобразований — сократить число отдельных транзакций (каждая имеет по крайней мере одну «лишнюю» фазу адреса) и, по возможности, фаз данных. Устройства PCI должны нормально отрабатывать комбинирование записей — если устройство не допускает комбинирования, оно неправильно спроектировано. Если устройство не допускает объединения байтов, тооновописании своей памяти должноиметь обнуленнымбитPrefetchable.

730Глава12. Шинырасширения

Смостами PCI связано понятие VGA Palette Snooping — слежение за записью в палитры VGA, являющееся исключением из правила однозначной маршрутизации обращений к памяти и вводу-выводу. Графическая карта в компьютере с шиной PCI обычно устанавливается в эту шину или в порт AGP, что логически эквивалентно установке в шину PCI. На VGA-карте имеются регистры палитр (Palette Registers), традиционно приписанные к пространству ввода-вывода. Если графическая система содержит еще и карту смешивания сигналов графического адаптера с сигналом «живого видео», перехватывая двоичную информацию о цвете текущего пиксела по шине VESA Feature Connector (снимаемую до регистра палитр), цветовая гамма будет определяться регистром палитр, размещенным на этой дополнительной карте. Возникает ситуация, когда операция записи в регистр палитр должна отрабатываться одновременно и в графическом адаптере (на шине PCI или AGP), и в карте видеорасширения, которая может размещаться даже на другой шине (в том числе и ISA). В CMOS Setup может присутствовать параметр PCI VGA Palette Snoop. При его включении запись в порты ввода-вывода по адресу регистра палитр будет вызывать транзакцию как на шине PCI, так и на шине ISA, чтение же по этим адресам будет выполняться только PCI. Реализация может возлагаться на графическую карту PCI. В других реализациях мосту явно указывают на данное исключение, и он сам распространяет запись в регистры палитр на шину ISA.

12.5.9.Программныйдоступ

кконфигурационномупространству игенерацияспециальныхциклов

Поскольку конфигурационное пространство PCI обособлено, в главный мост приходится вводить специальный механизм доступа к нему командами процессора, который «умеет» обращаться только к памяти или вводу-выводу. Для PCсовместимых компьютеров предусмотрены два механизма, из которых в спецификации 2.2 оставлен только первый (Configuration Mechanism #1). Номер механизма, которым пользуется конкретная системная плата, можно узнать путем вызова PCI BIOS.

Конфигурационные циклы адресуются к конкретному устройству (микросхеме PCI), для которого должен быть сформирован сигнал выборки IDSEL (единичное значение). Номер функции и адрес регистра декодируются самим устройством. Поскольку IDSEL воспринимается устройством только в фазе адреса, для него используют позиционное кодирование в линиях старших битов шины AD (конфигурационное пространство всех устройств занимает лишь малую часть пространства с 32-битной адресацией). На этих линиях в фазе адреса конфигурационного обращения может быть лишь один единичный бит, остальные — нулевые. Такимобразом, толькоодноустройствобудетвыбраносигналомIDSEL.

Для работы механизма № 1 в пространстве ввода-вывода зарезервированы 32-битные порты с адресами OCFSh и OCFCh, входящие в главный мост. Для обращения к конфигурационному пространству в порт CONFIG_ADDRESS (RW, адрес CF8h) заносят 32-разрядный адрес. После занесения адреса обращением к порту CONFIG_DATA (RW, адрес CFCh) можно прочитать или записать содержимое требуемогоконфигурационногорегистра.

12.5. ШинаPCI 731

Для работы механизма № 2 в пространстве ввода-вывода зарезервированы два 8-битных порта с адресами OCF8H и OCFAh, входящие в главный мост. Этот механизм использует отображение конфигурационного пространства устройств PCI на область COOO-CFFF пространства ввода-вывода. Поскольку этой области (4К портов) недостаточно для отображения конфигурационного пространства всех устройств всех шин PCI, формирование адреса выполняется весьма замысловатым образом.

Эти же механизмы используются для генерации специальных циклов PCI — дляэтогозадаетсяспецифическийадрес.

12.5.10.Конфигурированиеустройств

Встандартзаложенывозможностиавтоматическогоконфигурированиясистемных ресурсов (пространств памяти и ввода-вывода и линий запроса прерываний). Автоматическое конфигурирование устройств (выбор адресов и прерываний) поддерживается средствами BIOS и ориентировано на технологию Plug and Play. Стандарт PCI определяет для каждого слота конфигурационное пространство размером до 256 регистров (8-битных), не приписанных ни к пространству памяти, ни к пространству ввода-вывода. Доступ к ним осуществляется по спе-

циальнымцикламшиныConfiguration Read иConfiguration Write, вырабатываемым с помощью одного из вышеописанных механизмов. В этом пространстве есть области, обязательные для всех устройств, и специфические. После аппаратного сброса (или по включении питания) устройства PCI не отвечают на обращения к пространству памяти и ввода-вывода, они доступны только для операций конфигурационного считывания и записи. В этих операциях устройства выбираются по индивидуальным сигналам IDSEL и сообщают о потребностях в ресурсах и возможных вариантах конфигурирования. После распределения ресурсов, выполняемого программой конфигурирования (во время теста POST), в конфигурационные регистры устройства записываются параметры конфигурирования. Только после этого к устройствам становится возможным доступ по командам обращения к памяти и портам ввода-вывода. Для того чтобы всегда можно было найти работоспособную конфигурацию, все ресурсы, занимаемые картами, должны быть перемещаемыми в своих пространствах. Для многофункциональных карт каждая функция должна иметь свое конфигурационное пространство.

Конфигурационное пространство устройства начинается со стандартного заголовка, в котором содержатся идентификаторы производителя, устройства и его класса, а также описание требуемых и занимаемых системных ресурсов. После заголовкамогутрасполагатьсярегистры, специфичныедляустройства. .

12.5.11.КлассыустройствPCI

Важной частью спецификации PCI является классификация устройств и указание кода класса в его конфигурационном пространстве (3 байта Class Code). Старший байт определяет базовый класс, средний — подкласс, младший — программный интерфейс (если он стандартизован). Код класса позволяет определять наличие определенныхустройстввсистеме, этоможетбытьсделаноспомощью

732 Глава12. Шинырасширения

PCI BIOS. Для стандартизованных устройств (например, 01:01:80 — контроллер IDE или 07:00:01 — последовательный порт 16450) «заинтересованная» программа может найти требуемое устройство и выбрать подходящий вариант драйвера. Классификатор определяет организация PCI SIG, он регулярно обновляется на сайте www.pcisig.com. Нулевые значения полей, как правило, дают самые неопределенныеописания.

12.5.12. PCI BIOS

Для облегчения взаимодействия с устройствами PCI имеются дополнительные функции BIOS, доступные как из реального, так и защищенного режима работы процессора. Эти функции предназначены для работы с конфигурационным пространством и генерации специальных циклов PCI. Эти функции приходится поддерживать потому, что циклы конфигурационных обращений, как и специальный цикл, выполняются специфическим образом (см. выше). Остальные функции взаимодействия с устройствами через их пространства памяти и ввода-вывода, а также обработка прерываний в поддержке со стороны BIOS не нуждаются, поскольку выполняются непосредственно командами процессора. Функция проверки наличия PCI BIOS позволяет определить доступные механизмы генерации этих особых циклов, и, зная их работу, программа в дальнейшем может и не пользоваться вызовами PCI BIOS.

Программы с помощью функций PCI BIOS может искать интересующие их устройства по идентификаторами или кодам класса. Если стоит задача «переучета» установленных устройств, то она решается чтением конфигурационной информации по всем функциям всех устройств всех шин — это быстрее, чем перебирать все возможные сочетания идентификаторов или классов кодов. Для найденных устройств программы должны определять реальные настройки чтением регистров конфигурационного пространства, учитывая возможность перемещения ресурсов по всему пространству и даже между пространствами памяти и ввода-вывода.

Функции PCI BIOS для 16-битного интерфейса реального режима, V86 и 16битного реального режима, вызываются через прерывание Int lAh. Номер функции задается при вызове в регистре АХ. Возможна и программная имитация прерывания дальним вызовом по физическому адресу OOOFFE6Eh (стандартная точка входа в обработчик Int lAh) с предварительным занесением в стек регистра флагов.

Признаком нормального выполнения являются значения флагов CF-0 и АН-0; приCF-1 регистрАНсодержиткодошибки:

к81h — неподдерживаемаяфункция;

*83h — неправильныйидентификаторпроизводителя;

*86h — устройствоненайдено;

*87h — неправильныйномеррегистраPCI.

Вызовы требуют глубокого стека (до 1024 байт). Для 32-разрядных вызовов защищенного режима все эти же функции вызываются через точку входа, най- деннуючерезкаталог32-разрядныхсервисов(см. п. 15.5), приэтомназначение

12.6. МагистральныйинтерфейсAGP 733

входных и выходных регистров и флага CF сохраняется. До использования 32-разрядногоинтерфейсаследуетсначаланайтиегокаталогиубедитьсявна- личиисервисовPCI. ФункцииPCI BIOS:

» АХ= BlOlh — проверкаприсутствияPCI BIOS;

ш АХ= B102h — поискустройствапоидентификатору;

иАХ= ВЮЗЬ— поискустройствапокодукласса;

иАХ= B106h — генерацияспециальногоциклаPCI;

тАХ = В108, В109 и BlOAh — чтение байта, слова и двойного слова конфигурационногопространстваустройстваPCI;

тАХ - В10В, В10С, BlODh — запись байта, слова и двойного слова конфигурационногопространстваустройстваPCI.

12.6.МагистральныйинтерфейсAGP

Внастоящее время самой быстрой универсальной шиной расширения является PCI, имеющая при тактовой частоте 66 МГц и разрядности 32 бит пиковую пропускную способность 264 Мбайт/с. Одним из главных потребителей пропускной способности шины является графический адаптер. По мере увеличения разрешения и глубины цвета требования к пропускной способности шины, связывающей дисплейный адаптер с памятью и центральным процессором компьютера, повышаются. Одно из решений состоит в уменьшении потока графических данных, передаваемых по шине. Для этого графические платы снабжают акселераторами и увеличивают объем видеопамяти, которой пользуется акселератор при выполнении построений. В результате поток данных в основном циркулирует внутри графической карты, слабо нагружая внешнюю шину. Однако при трехмерных построениях акселератору становится тесно в ограниченном объеме локальной памяти графического адаптера, и его поток данных снова выплескивается на внешнюю шину.

Фирма Intel на базе шины PCI 2.1 разработала стандарт подключения графических адаптеров — AGP (Accelerated Graphic Port — ускоренный графический порт). Первая версия стандарта вышла в 1996 году, в настоящее время действует версия 2.0 (1998 г.), отличающаяся от первой в основном введением нового режима передачи 4х. В конце 2000 года Intel опубликовала черновик спецификации AGP8X, которая рассматривается как отдельная спецификация, а не просто развитие предыдущих. Ее особенности отметим в конце раздела.

Порт AGP представляет собой 32-разрядную шину с тактовой частотой 66 МГц, большая часть сигналов позаимствована из шины PCI. Однако в отличие от PCI порт AGP представляет собой двухточечный интерфейс, соединяющий графический адаптер с памятью и системной шиной процессора напрямую логикой и каналами данных чипсета системной платы, не пересекаясь с «узким местом» — шиной PCI. Поначалу планировался переход на тактовую частоту 100 МГц, но и в спецификации AGP 2.0, и в черновом варианте AGP8X фигурирует лишь одна частота — 66,6 МГц (нынешний предел и для шины PCI). «Ускоренность» порта обеспечивается следующими факторами:

734Глава12. Шинырасширения

«конвейеризациейобращенийкпамяти;

«удвоенной(2х) илиучетверенной(4х) частотойпередачиданных(относительнотактовойчастотыпорта); ж демультиплексированиемшинадресаи данных.

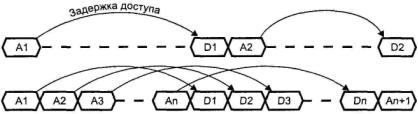

Идею конвейеризации обращений к памяти иллюстрирует рис. 12.6, где сравниваются обращения к памяти PCI и AGP. В PCI во время реакции памяти на запрос шина простаивает (но не свободна). Конвейерный доступ AGP позволяет в этовремяпередаватьследующиезапросы, апотомполучитьпотокответов.

PCI

AGP

Рис. 12.6. ЦиклыобращениякпамятиPCI иAGP

Удвоениеиучетверениечастотыпередачиданныхобеспечиваетпричастоте66 МГц пропускную способность до 533 (2х) и 1066 Мбайт/с (4х), что для 32битной шины несколько неожиданно. В этих режимах блоки данных передаются как по фронту, так и по спаду стробирующего сигнала (как в АТА Ultra DMA). Режимы 2х и 4х могут использоваться, лишь если их поддерживает и графическийадаптер, исистемнаяплата.

Демультиплексирование (разделение) шины адреса и данных сделано несколько необычным образом. С целью экономии числа интерфейсных линий шину адреса и команды в демультиплексированном режиме AGP представляет всего 8 линий SBA (SideBand Address), по которым команда, адрес и длина передачи передаются последовательно за несколько тактов. Поддержка демультиплексированной адресации не является обязательной для устройства AGP, поскольку имеетсяальтернативныйспособподачиадресапошинеAD.

Порт AGP предназначен только для интеллектуального графического адаптера, имеющего SD-акселератор (см. п. 8.3); для краткости здесь этот адаптер будем называть просто акселератором. Системная логика порта AGP отличается сложным контроллером памяти, который выполняет глубокую буферизацию и высокопроизводительное обслуживание запросов AGP (от адаптера) и других своих клиентов — центрального процессора (одного или нескольких) и шины PCI. AGP может реализовать всю пропускную способность 64-битной системы памяти компьютера напроцессорах Pentium ивыше. Приэтомвозможныконкурирующие обращения к памяти как со стороны процессора, так и со стороны мостов шин PCI. Фирма Intel ввела поддержку AGP в чипсеты для процессоров Pentium Pro иPentium II. Однаконет«противопоказаний» дляпримененияAGP сPentium.

Отметим, что многие преимущества AGP носят потенциальный характер и могутбытьреализованылишьприподдержкеаппаратныхсредствграфиче-

12.6. МагистральныйинтерфейсAGP 735

скогоадаптераиПО. ГрафическийадаптерсинтерфейсомAGP можетреально вестисебяпо-разному:

% не задействовать конвейеризацию, а использовать только быструю запись

PCI (Fast Write);

« не работать с текстурами, расположенными в системной памяти, но использовать более быстрый обмен данными между памятью и локальным буфером;

т использовать оптимальное распределение текстур между локальной и системной памятью, избегая конфликтов с обращениями к памяти от процессора.

Что касается большой пропускной способности AGP, то следует напомнить, что в графических адаптерах с памятью WRAM или RDRAM внутренняя скорость обмена данными акселератора с видеопамятью достигает 1,6 Гбайт/с, так чтоакселераторнаAGP имеетвыигрыштольковобъемедоступнойпамяти.

Порт AGP содержит практически полный набор сигналов шины PCI и дополнительные сигналы AGP. Устройство, подключаемое к порту AGP, может предназначаться как исключительно для операций AGP, так и быть комбинацией AGP+PCI. Устройство обязательно должно выполнять функции мастера AGP (иначе порт AGP для него теряет смысл) и функции ведомого устройства PCI со всеми его атрибутами (конфигурационными регистрами и т. п.); дополнительно оно может быть и мастером PCI. Для транзакций в режиме AGP ему доступно только системное ОЗУ. В режиме PCI обращения возможны как к пространству памяти, такикпространствуввода-выводаиконфигурационномупространству.

Транзакции в режиме PCI, инициируемые акселератором, выполняются обычным для PCI способом (см. п. 12.5). Заметим, что при этом на все время транзакции шина AD занята, причем транзакции чтения памяти занимают шину на большее число тактов, чем транзакции записи — после подачи адреса неизбежны такты ожидания на время доступа памяти. Запись на шине происходит быстрее — данные записи задатчик посылает сразу за адресом, а на время доступа памяти они «оседают» в буфере контроллера памяти. Контроллер памяти позволяет завершить транзакцию и освободить шину до физической записи в память. Обращения со стороны процессора (или задатчиков шины PCI) отрабатываются адаптеромтакже, какобычнымустройствомPCI.

Конвейерные транзакции AGP (команды AGP) инициируются только акселератором; логикой AGP они ставятся в очереди на обслуживание и исполняются в зависимости от приоритета, порядка поступления запросов и готовности данных. Эти транзакции могут быть адресованы акселератором только к системному ОЗУ. Транзакции, адресованные к устройству AGP, отрабатываются им как ведомым устройством PCI, однако имеется возможность быстрой записи в локальную память FW (Fast Write), в которой данные передаются на скорости AGP (2х или 4х) и управление потоком их передач ближе к протоколу AGP, нежели PCI. Транзакции FW обычно инициируются процессором и предназначены для принудительного«заталкивания» данныхвлокальнуюпамятьакселератора.

Возможны два способа подачи команд AGP (постановки запросов в очередь), из которых в текущей конфигурации выбирается один, причем изменение способа «на ходу» недопускается.