- •1. История развития архитектуры эвм

- •Нулевое поколение (1492 – 1945)

- •Первое поколение (1937-1953)

- •Второе поколение (1954 - 1962)

- •Третье поколение (1963-1972)

- •Четвертое поколение (1972-1984)

- •Пятое поколение (1984-1990)

- •Шестое поколение (1990-)

- •2.Процессор. Структурная схема процессора.Понятие о микропрограммном управлении.

- •Алгоритмы выполнения микроопераций.Микропрограммы.

- •Обратная структурная таблица

- •Управляющие автоматы с программируемой логикой.

- •1.Конвейеризация (конвейер операций).

- •2. Процессоры с risc – архитектурой.

- •3. Организация кэш-памяти.

- •3.1. Техническая идея кэш-памяти.

- •3.2. Архитектура кэш-памяти.

- •3.2.1. Кэш память с прямым отображением.

- •3.2.2. Полностью ассоциативная кэш память.

- •3.2.3. Частично ассоциативная кэш память.

- •3.3 Алгоритм замещения строк в кэш памяти.

- •3.4 Методы записи в кэш память.

- •Размещение байт и слов в памяти.

- •1. Концепции и компоненты защищенного режима.

- •2. Информационная основа работы механизма защиты.

- •3. Уровни привилегий

- •4.3 Защита программ.

- •Системы ввода/вывода

- •Адресное пространство системы ввода/вывода

- •Внешние устройства

- •Модули ввода/вывода

- •Методы управления вводом/выводом

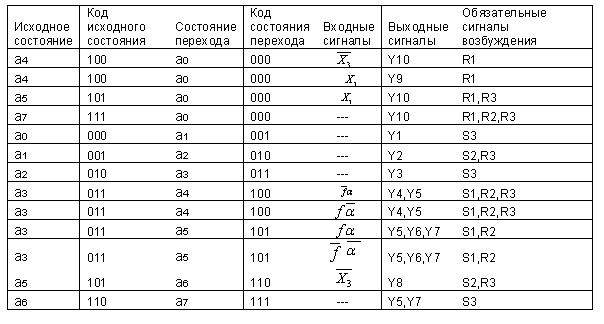

Обратная структурная таблица

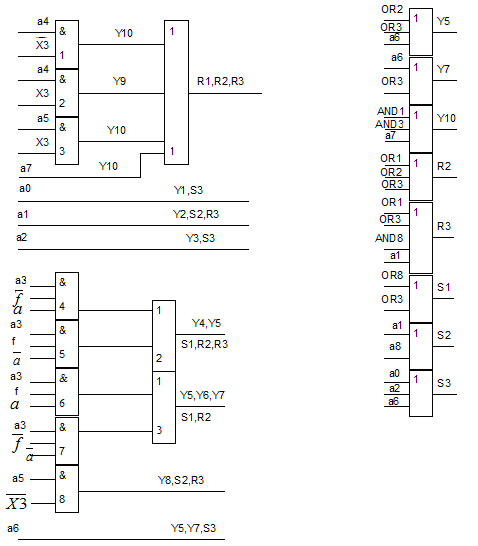

Схема КЧ синтезируется в соответствии со структурной таблицей. На первом этапе строятся схемы переходов в отдельные состояния. На этом этапе для каждого перехода в состояние с Ai вводится конъюнктор, на входы которого подаются сигналы исходного состояния и входные сигналы, от значений которых зависит данный переход. С выхода конъюнктора снимаются соответствующие данному переходу сигналы микроопераций и обязательные сигналы возбуждения триггеров. Далее выходы конъюнкторов объединяются с помощью дизъюнктора, с выхода которого снимаются сигналы микроопераций, общие для всех переходов в данное состояние и логическая сумма множеств обязательных сигналов возбуждения триггеров на рассматриваемых переходах. На втором этапе в схему КЧ вводятся дизъюнкторы для одних и тех же сигналов, которые формируются на переходах автомата в различные состояния. В результате получается следующая функциональная схема КЧ:

Управляющие автоматы с программируемой логикой.

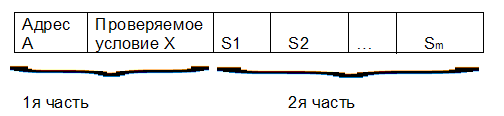

Существует несколько вариантов построения таких автоматов. В качестве примера рассмотрим управляющий автомат с принудительной адресацией одноадресных МК, использующих раздельно закодированные поля. Формат микрокоманды:

|

|

|

|

|

|

|

МК

состоит из двух частей: адресной и

операционной. В адресную часть входят:

поле адреса А следующей выполняемой МК

и поле проверяемого логического условия

Х. В операционную часть входят раздельно

кодируемые поля

![]() микроопераций. Количество таких полей

равно максимальному числу управляющих

сигналов

микроопераций. Количество таких полей

равно максимальному числу управляющих

сигналов![]() ,

формируемых одновременно, т е в одном

такте. Операционная часть МК как раз и

служит для записи одновременно формируемых

сигналов

,

формируемых одновременно, т е в одном

такте. Операционная часть МК как раз и

служит для записи одновременно формируемых

сигналов![]() ,

причем каждое поле

,

причем каждое поле![]() используется для записи множества

сигналов

используется для записи множества

сигналов![]() ,

которые одновременно не формируются.

В каждый момент времени может формироваться

только один сигнал

,

которые одновременно не формируются.

В каждый момент времени может формироваться

только один сигнал![]() из каждого множества

из каждого множества![]() .

Поскольку таких множеств в МКm

штук, то одновременно формируются до m

сигналов – по одному из каждого множества

.

Поскольку таких множеств в МКm

штук, то одновременно формируются до m

сигналов – по одному из каждого множества

![]() .

Если в данный момент времени ни один

сигнал изj-го

множества

.

Если в данный момент времени ни один

сигнал изj-го

множества

![]() не формируется, то поле

не формируется, то поле![]() =0.

=0.

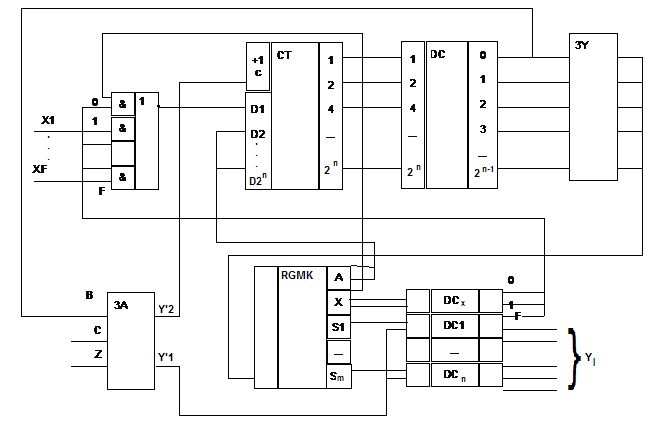

Структурная схема управляющего автомата с программируемой логикой имеет следующий вид:

В схеме приняты следующие обозначения: СТ – счетчик адреса МК, ДС – дешифратор адреса МК, ЗУ – запоминающее устройство (память МК), RGMK – регистр МК, ЗА – задающий автомат.

При

использовании данной схемы в качестве

управляющего автомата, выполнение

микропрограммы сводится к чтению

содержимого ячеек ЗУ в требуемой

последовательности. Этот процесс

осуществляется по управляющим сигналам

![]() ,

формируемых ЗА. ЗА – автомат с жесткой

логикой, имеющий следующую рабочую

микропрограмму:

,

формируемых ЗА. ЗА – автомат с жесткой

логикой, имеющий следующую рабочую

микропрограмму:

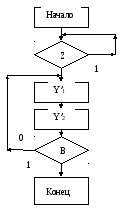

Здесь

Z

- сигнал запуска, В – логическое условие,

равное единице, если в счетчике микрокоманд

находится адрес первой выполняемой МК

в микропрограмме (как правило это 0й

адрес). По управляющему сигналу

![]() осуществляется формирование сигналов

микроопераций

осуществляется формирование сигналов

микроопераций![]() .

По управляющему сигналу

.

По управляющему сигналу![]() в счетчик адреса микрокоманд СТ

записывается адрес следующей выполняемой

МК. В целом управляющий автомат работает

следующим образом: в счетчик СТ

записывается нулевой начальный адрес

и из ЗУ в регистрRGMK

записывается первая МК. Подается сигнал

запуска Z

в ЗА. ЗА начинает формировать

последовательность сигналов

в счетчик адреса микрокоманд СТ

записывается адрес следующей выполняемой

МК. В целом управляющий автомат работает

следующим образом: в счетчик СТ

записывается нулевой начальный адрес

и из ЗУ в регистрRGMK

записывается первая МК. Подается сигнал

запуска Z

в ЗА. ЗА начинает формировать

последовательность сигналов

![]() .

По сигналу

.

По сигналу![]() формируются сигналы микроопераций

формируются сигналы микроопераций![]() для находящейся в регистреRGMK

микрокоманды. По сигналу

для находящейся в регистреRGMK

микрокоманды. По сигналу

![]() в счетчике СТ записывается адрес

следующей МК. По этому адресу из ЗУ

читается вторая МК и т д.

в счетчике СТ записывается адрес

следующей МК. По этому адресу из ЗУ

читается вторая МК и т д.

При

определении адреса следующей МК все

разряды адреса А, кроме младшего,

передаются в счетчик СТ непосредственно

из адресной части выполняемой МК. В поле

Х может быть записан либо 0, либо двоичный

код, присвоенный одному из логических

условий.

![]() ГдеF

– количество различных условий

ГдеF

– количество различных условий

![]() ,

которые проверяются в микропрограмме.

Если в поле Х записан 0, то младший разряд

адреса А из адресной части выполняемой

МК через верхний конъюнктор записывается

в младший разряд Д1 счетчика СТ. Таким

образом в этом случае адрес полностью

поступает в счетчик СТ, включая младший

разряд, и следующей будет выполняться

МК, хранящаяся в ЗУ по этому адресу. Если

нужно реализовать условный переход, то

в поле Х записывается номерf

проверяемого условия

,

которые проверяются в микропрограмме.

Если в поле Х записан 0, то младший разряд

адреса А из адресной части выполняемой

МК через верхний конъюнктор записывается

в младший разряд Д1 счетчика СТ. Таким

образом в этом случае адрес полностью

поступает в счетчик СТ, включая младший

разряд, и следующей будет выполняться

МК, хранящаяся в ЗУ по этому адресу. Если

нужно реализовать условный переход, то

в поле Х записывается номерf

проверяемого условия

![]() и в младший разряд Д1 счетчика СТ поступает

значение самого условия

и в младший разряд Д1 счетчика СТ поступает

значение самого условия![]() ,

т е либо 0, либо1. Проверяемое условие

,

т е либо 0, либо1. Проверяемое условие![]() проходит через выбранный с помощью

дешифратора ДСх соответствующий

конъюнктор и поступает в младший разряд

Д1 счетчика СТ. Таким образом реализуется

переход к одной из двух МК, записанных

в ЗУ по адресам: А1 0, А1 1. А1 – (n-1)

разрядный адрес из поля А, т е все разряды,

кроме младшего. В результате в зависимости

от значений проверяемого условия

проходит через выбранный с помощью

дешифратора ДСх соответствующий

конъюнктор и поступает в младший разряд

Д1 счетчика СТ. Таким образом реализуется

переход к одной из двух МК, записанных

в ЗУ по адресам: А1 0, А1 1. А1 – (n-1)

разрядный адрес из поля А, т е все разряды,

кроме младшего. В результате в зависимости

от значений проверяемого условия

![]() реализуется условный переход либо по

адресу А1 0, либо по адресу А1 1. В приведенной

структурной схеме управляющего автомата

с программируемой логикой признаком

окончания микропрограммы является

равенство единице условия В. Поэтому

последняя выполняемая МК в микропрограмме

должна передавать управление первой

МК. Тогда В становится равным единице

и ЗА выходит на конечную вершину графа

МП и останавливается.

реализуется условный переход либо по

адресу А1 0, либо по адресу А1 1. В приведенной

структурной схеме управляющего автомата

с программируемой логикой признаком

окончания микропрограммы является

равенство единице условия В. Поэтому

последняя выполняемая МК в микропрограмме

должна передавать управление первой

МК. Тогда В становится равным единице

и ЗА выходит на конечную вершину графа

МП и останавливается.

АДРЕСНАЯ СТРУКТУРА ПАМЯТИ

Оперативная память ЭВМ является адресной. Это значит, что каждая хранимая в ОЗУ единица информации (байт или слово) ставится в соответствии со специальным числом, называемым адресом, которое определяет месторасположение этой информации в памяти. Минимальной, адресуемой в памяти единицей информации является байт, т.е. восьмиразрядный код. Более крупные единицы информации (полуслово, слово, двойное слово) образуются из целого числа байт.

В мини- и микро-ЭВМ нумерация бит и байт в слове производится справа налево. В машинах общего назначения нумерация бит и байт в слове производится слева направо. Адресом слова является адрес его байта с наименьшим номером.

ПРИНЦИПЫ ПОСТОРОЕНИЯ УСТРОЙСТВ ПАМЯТИ

В ЭВМ используется несколько типов запоминающих устройств, отличающихся принципом действия, характеристиками и назначением.

Основными операциями в памяти являются запись и чтение. Обе эти операции называются «обращение к памяти». Важнейшими характеристиками ЗУ являются их емкость и быстродействие. Емкость памяти определяется максимальным количеством данных, которые в ней могут храниться. Быстродействие памяти определяется продолжительностью операции обращения, т.е. временем, затрачиваемым на поиск нужной единицы информации и ее чтение. В зависимости от реализуемых в памяти операций обращения различают:

А) память с произвольным обращением (RAM – Random Access Memory);

Б) память только для чтения информации (ROM – Read Only Memory), такая память носит название односторонней или постоянной.

По способу организации доступа различают ЗУ:

с непосредственным (произвольным) доступом;

с прямым (циклическим) доступом;

с последовательным доступом.

В памяти с непосредственным доступом время доступа не зависит от месторасположения информации. В таких ЗУ цикл обращения обычно составляет несколько наносекунд (1нс = 10-9 с).Число разрядов, читаемых или записываемых в память за одну операцию обращения, называется шириной выборки (1,2,3…байта). Типичный пример такой памяти – это адресное оперативное ЗУ.

В устройствах памяти с прямым доступом, благодаря непрерывному вращению носителя информации, возможность обращения к некоторому участку носителя циклически повторяется. Пример такой памяти – это память на различных дисках.

В памяти с последовательным доступом производится последовательный просмотр участков носителей. Обычно это магнитная лента. ЗУ, использующие запись на магнитную ленту, называются стриммерами.

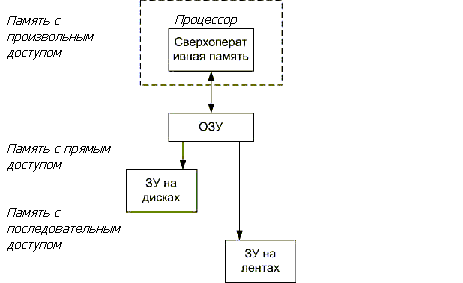

Обычно память организуется в виде иерархической структуры ЗУ, обладающих различным быстродействием и емкостью.

В ЭВМ используется сверхоперативная память, которая располагается в процессоре, оперативная память (ОЗУ), память с прямым доступом на дисках, память с последовательным доступом на лентах.

П орядок

перечисленных устройств соответствует

убыванию их быстродействия и возрастания

емкости. Иерархическая структура памяти

позволяет экономически эффективно

сочетать хранение больших объемов

информации с быстрым доступом в процессе

ее обработки.

орядок

перечисленных устройств соответствует

убыванию их быстродействия и возрастания

емкости. Иерархическая структура памяти

позволяет экономически эффективно

сочетать хранение больших объемов

информации с быстрым доступом в процессе

ее обработки.

Оперативной или основной памятью называется ЗУ, которая служит для хранения информации, непосредственно используемой в процессе выполнения программ в Процессоре. Процессор может выполнить только те программы, которые находятся в ОЗУ. Если быстродействие ОЗУ оказывается недостаточным, то в состав ЭВМ включают Сверхоперативную память (КЭШ). Быстродействие такой памяти обычно соответствует скорости работы самого Процессора.

Если емкость ОЗУ оказывается недостаточной, то в ЭВМ включают несколько ЗУ с прямым доступом на дисках или с последовательным доступом на лентах. Оперативная и Сверхоперативная память образуют внутреннюю память ЭВМ. Память на дисках и лентах – это внешняя память. Внешние ЗУ подключаются к Процессору и ОЗУ через специальное устройство – контроллер.

АДРЕСНАЯ, АССОЦИАТИВНАЯ И СТЕКОВАЯ ОРГАНИЗАЦИЯ ПАМЯТИ

ЗУ с произвольным обращением обычно содержит множество одинаковых запоминающих элементов, образующих запоминающий массив (ЗМ). ЗМ разделен на отдельные ячейки, число разрядов в которых равно ширине выборки памяти. Способ организации памяти зависит от метода размещения и поиска информации в ЗУ. По этому признаку различают адресную, ассоциативную и стековую память.

АДРЕСНАЯ ПАМЯТЬ

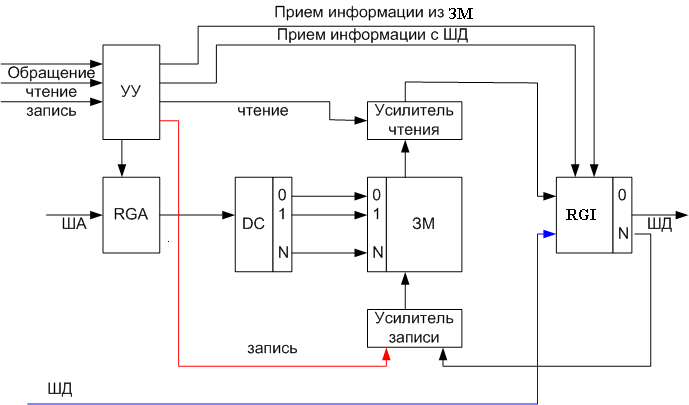

В такой памяти размещение и поиск информации в ЗУ основаны на использовании адреса байта или слова. Адресом служит порядковый номер ячейки ЗМ, в которой это слово размещается. Структурная схема адресной памяти объемом N n-разрядных слов имеет следующий вид

При каждом обращении к ЗУ необходимо указывать номер (адрес) ячейки памяти, в которой размещается нужная информация. Для приема адреса А служит регистр адреса RGA. Этот адрес дешифруется дешифратором адреса DC, который формирует сигнал на одном из своих выходов. При этом номер этого выхода равен самому адресу А. Таким образом, дешифратор DC указывает номер ячейки памяти, к которой происходит обращение. При чтении информации из ЗУ устройство управления формирует управляющий сигнал «чтение», под действием которого прочитанное из ЗУ слово поступает в усилители чтения, а оттуда в регистр информации RGI.

Занесение прочитанного слова в RGI происходит под действием управляющего сигнала “Прием информации из ЗМ”. Аналогично происходит запись информации в ЗМ. При этом записываемое слово поступает с ШD в регистр RGI, а оттуда через усилитель записи под действием сигнала «запись» в выбранную ячейку ЗМ. Любой цикл обращения к памяти инициируется поступлением сигнала «обращение». На УУ поступают также сигналы «чтение» и «запись», которые указывают вид выполняемой в ЗУ операции (запись или чтение).

Для построения адресной памяти используются микросхемы памяти, в состав которых кроме ЗМ входят также усилители чтения и записи, а также дешифратор памяти.

АССОЦИАТИВНАЯ ПАМЯТЬ

В памяти этого типа поиск нужной информации производится не по адресу, а по содержанию самой информации (т.е. по ассоциативному признаку). При этом поиск по ассоциативному признаку происходит параллельно во времени для всех ячеек памяти. Ассоциативный поиск позволяет существенно упростить и ускорить обработку данных. Это достигается за счет того, что в такой памяти операция чтения информации совмещена с выполнением ряда логических операций. Например, можно выполнять такие операции, как:

поиск максимального или минимального числа в ЗУ;

поиск слов, заключенных в определенные границы;

поиск слов, ближайших к ассоциативному признаку, как с большей, так и с меньшей стороны и т.д.

Простейшая ассоциативная память обычно выполняет единственную операцию по выборке слов, чей признак совпадает с ассоциативным признаком.

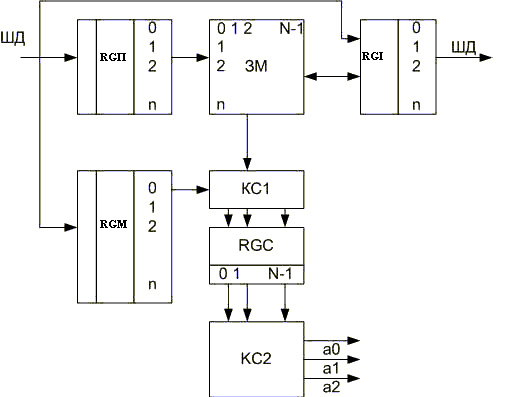

ЗМ содержит N ячеек, каждая ячейка n+1 разрядная. Для указания занятости ячейки используется служебный n-ый разряд. Если в n-ом разряде 0 – то ячейка свободна, если 1 – то занята.

По входной ШD в регистр ассоциативного признака RGП поступает n-разрядный признак, а в регистр маски RGМ – код маски поиска. При этом n-ый разряд регистра RGМ устанавливается в 0. Ассоциативный поиск производится лишь по тем разрядам признака, которым соответствует «1» в регистре маски, то есть по так называемым незамаскированным разрядам RGМ. Таким образом, задавая код маски М, можно произвольно выбирать те разряды признака, по которым ведется поиск.

Для слов из ЗМ, в которых все цифры совпали с незамаскированными разрядами RGП, комбинированная схема КС 1 устанавливает «1» в соответствующие разряды регистра совпадения RGC. Таким образом, если произошло совпадение цифры j-го слова с незамаскируемыми разрядами признака, то в j-ом разряде регистра RGC будет записана «1», в противном случае «0». Запись «1» в j-ом разряде RGC означает, что j-ое слово соответствует признаку, т.е. является тем словом, которое собственно и ищется в ЗМ. КС 1 реализует следующую систему М булевых уравнений:

n-1 ________ _________

RGC(j) = /\ [RGП(i)~ЗМ(j,i) V RGM(i)] j = 0,N-1

i=0

~ - операция равнозначности;

/\- знак конъюнкции.

RGП(i)~ЗМ(j,i) = 1, если i-ые разряды слов совпадают.

Выходы регистра RGC соединены со входами КС2, которая формирует выходы α0, α1, α2. Символ α0=1, если во всех разрядах RGC находятся «», что соответствует случаю отсутствия искомых слов в ЗМ.

Символ α1=1, если имеется одно слово в ЗМ, удовлетворяющее ассоциативному поиску. Символ α2=1, если таких слов больше одного. При α1=1 найденное слово из ЗМ записывается в RGI, а оттуда в выходную шину ШД. При α2=1 обычно читается слово из ячейки, имеющей наименьший номер среди ячеек, отмеченных «1»-цей в RGC.

При записи информации сначала находится свободная ячейка. Для этого выполняется операция ассоциативного поиска по признаку, имеющему во всех разрядах «0», а в регистре маски «0» записаны во всех разрядах, кроме младшего n-го разряда.

Таким образом, определяются те ячейки ЗМ, у которых в n-ом разряде записан «0», что означает незанятость ячейки. В свободную ячейку с наименьшим номером записывается слово из регистра информации RGI.

СТЕКОВАЯ ПАМЯТЬ

С тековая

память также как и ассоциативная,

является безадресной, она представляет

собой совокупность ячеек, образующих

одномерный массив, в котором соседние

ячейки связаны друг с другом разрядными

цепями передачи слов. Запись слов всегда

производится в верхнюю нулевую ячейку.

При этом все ранее записанные слова

сдвигаются вниз на одну ячейку.

тековая

память также как и ассоциативная,

является безадресной, она представляет

собой совокупность ячеек, образующих

одномерный массив, в котором соседние

ячейки связаны друг с другом разрядными

цепями передачи слов. Запись слов всегда

производится в верхнюю нулевую ячейку.

При этом все ранее записанные слова

сдвигаются вниз на одну ячейку.

ШД

-

0

1

2

:

Слово, находившееся ранее в 0-ой ячейке, переходит в 1-ую, из 1-ой во 2-ую и так далее.

Чтение также производится из верней ячейки. Если чтение производится с удалением слова из стека ячейки с меньшим номером. В такой последовательности порядок чтения слов соответствует правилу: «последним поступил – первым обслужен». Чтение производится в порядке обратном порядку записи.

На практике часто стековую память организуют, используя обычную адресную память. Архитектура большинства ЭВМ позволяет легко организовать стеки с так называемой скользящей вершиной.

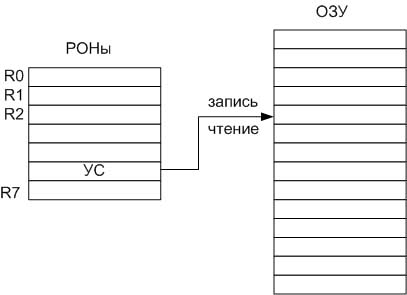

В процессоре PDP-11 имеется восемь регистров общего назначения (РОНов).

Любой из этих РОНов, кроме R7, программист может использовать в качестве указателя вершины стека. Область ОЗУ, в которой располагается стек, также выбирает программист. При организации стека программист должен установить в выбранном РОНе первоначальное значение адреса вершины стека (УС).

При записи в стек байта или слова используется команда с адресацией типа «автодекрементная прямая». Выполняя такую команду, процессор автоматически уменьшает УС на единицу и только после этого записывает байт или слово.

Таким образом, при записи слова указатель вершины стека УС будет смещаться вверх на 2 байта, указывая всегда на ячейку ОЗУ, в которой записано последнее слово.

При чтении информации из стека необходимо использовать команды с адресацией типа «автоинкрементная прямая». Выполняя такую команду, процессор вначале читает байт или слово из ОЗУ по адресу, содержащемуся в УС, и только после этого увеличивает содержимое УС на 1 и 2, указывая на ячейку, в которой находится следующий байт или слово. Таким образом, в свободной области памяти можно организовать стек со скользящей вершиной.

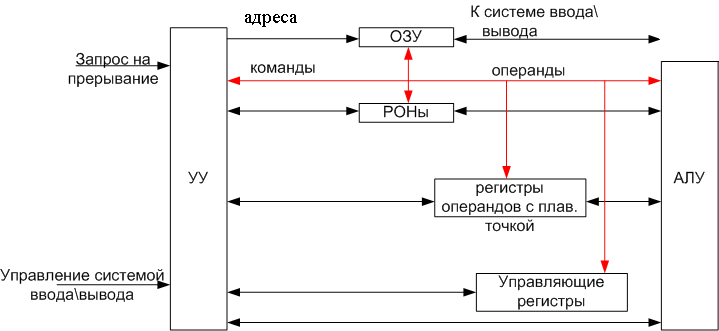

Логическая структура процессора

Р ассмотрим

логическую структуру процессора ЭВМ

общего назначения на примере ЭВМ типаIBM

370.

ассмотрим

логическую структуру процессора ЭВМ

общего назначения на примере ЭВМ типаIBM

370.

Обобщенная структурная схема процессора содержит АЛУ, УУ и регистры. Процессор может обрабатывать числа, представленные в двоичном коде; числа с плавающей точкой фиксируемой длины; десятичные числа.

Выполняемые процессором команды образуют 5 классов:

1-команды управления системой;

2-общие команды;

3-команды для выполнения действий над числами с плавающей точкой;

4-команды для выполнения действий над десятичными числами;

5-команды ввода/вывода.

Команды управления системой и команды ввода-вывода являются привилегированными командами и выполняются только операционной системой. Если такие команды встретятся в программе пользователя, то выполняться они не будут и произойдет прерывание программы.

Общие команды применяются для чисел с фиксированной точкой, а также для выполнения переходов в программе.

Процессор может обращаться за информацией к 16 регистрам общего назначения (РОН). РОНы могут быть использованы в качестве накапливающих регистров в арифметических операциях с фиксированной точкой и в логических операциях, а также как индексные регистры в операциях над адресами. Каждый РОН имеет 32 разряда и задается в командах с помощью 4-битового поля R.

При выполнении некоторых операций два смежных регистра используются совместно, позволяя работать с двойными словами. В этом случае адресуемый регистр содержит старшие биты операнда и должен иметь четный адрес, тогда как РОН, содержащий младшие биты операнда, имеет следующий по порядку нечетный адрес.

Для операций с плавающей точкой процессор имеет четыре 64-разрядных регистра. Они пронумерованы числами : 0,2,4,6. Эти регистры могут содержать как короткие 32-, так и длинные 64-битовые операнды с плавающей точкой. Короткие операнды занимают старшие биты регистра, а младшие биты не используются.

Процессор может также использовать 16 управляющих регистров по 32 бита в каждом. Отдельные биты этих регистров закреплены за конкретными средствами и содержат особую информацию для функционирования этих средств. Управляющие регистры нумеруются числами от 0 до 15, которые в командах управления системой задаются полем R.

Имеются 3 класса операндов:

1-регистровые операнды;

2-непосредственные операнды;

3-операнды в ОЗУ.

1-Регистровые операнды размещаются в регистрах процессора, причем тип регистра определяется кодом операции, а номер регистра задается полем R команды.

2-Непосредственные операнды располагаются в самой команде, занимают 1 байт, который обозначается буквой I в поле команды.

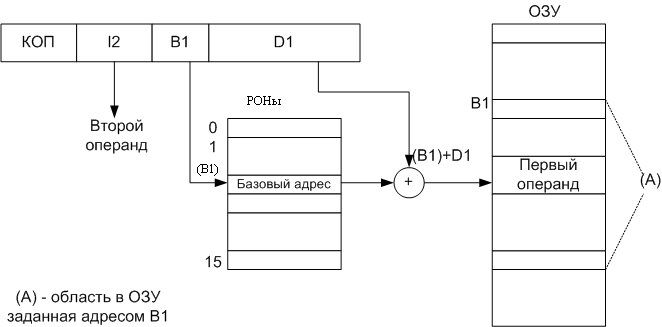

3-Для обращения за операндом, находящимся в ОЗУ, используется либо адрес находящийся в одном из РОНов, либо адрес, который вычисляется по базовому адресу, индексу и смещению, обозначаемые в команде полями В, Х и Д.

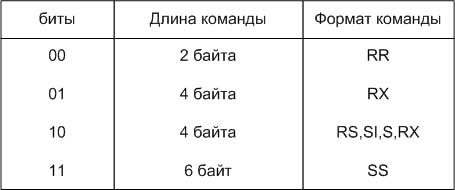

Команды процессора

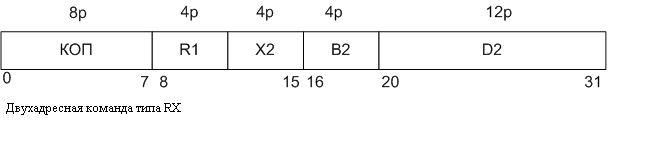

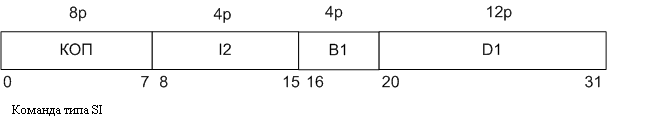

Команды имеют длину в 2, 4, 6 байт. Каждая команда имеет один из шести возможных форматов:

RR, RX, RS, SI, S, SS. В обозначениях форматов используются заглавные буквы, которые указывают, операнды каких классов участвуют в операциях.

RR – операция типа регистр-регистр.

RХ – операция регистр-память, в которой адрес памяти индексируется.

RS – операция регистр-память, но без индексации.

SI – операция память-непосредственный операнд.

SS – операция память-память.

S – один операнд находится в памяти, а другой операнд задан не явно.

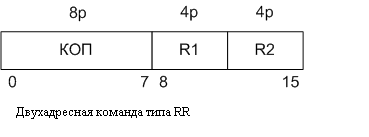

Первый байт команды, а в формате S – первые два байта, содержат код операции. Первые два бита кода операции определяют длину и формат команды.

В качестве примера приведем некоторые

форматы команд:

качестве примера приведем некоторые

форматы команд:

В форматеRX

первый адрес находится в РОНе, номер

которого задан полем R1

, а второй адрес задается полями В2,

Х2,

D2,

и указывает на ячейку ОЗУ.

форматеRX

первый адрес находится в РОНе, номер

которого задан полем R1

, а второй адрес задается полями В2,

Х2,

D2,

и указывает на ячейку ОЗУ.

В формате SI в качестве второго операнда непосредственно используется содержимое 8-разрядного поля I2. При этом поля В1 и D1 определяют 1-ый операнд, который находится в ОЗУ. Адрес обращения ОЗУ либо содержится в регистре, номер которого указывается в поле R команды, либо формируется из трех двоичных чисел; базового адреса, индекса и смещения.

Базовый адрес – это 24-разрядное число в РОНе, номер которого задан полем В команды. Базовый адрес используется как средство независимой адресации каждой области памяти и определяет положение этой области в ОЗУ, указывая адрес первого байта области.

Индекс – представляет собой 24-разрядное число в РОНе, номер которого задан в поле Х команды.

Смещение – представляет собой 12-разрядное число в поле D команды. Смещение позволяет выполнить относительную адресацию в пределах 4096 байт, следующих за ячейкой, адрес которой равен базовому адресу.

Рассмотрим формирование физического адреса на примере формата SI.

В общем случае для формирования адреса, базовый адрес и индекс рассматривается в качестве 24-разрядных положительных чисел. Аналогично, смещение рассматривается в качестве 12-разрядного положительного числа, старшие 12 разрядов которого равны 0. Все три компоненты адреса (база, индекс и смещение) суммируются как 24-разрядные двоичные числа. При этом, если возникает переполнение, то оно игнорируется (не учитывается). В результате получается 24-разрядный адрес ячейки в ОЗУ, в которой находится один из операндов. При отсутствии в команде поля Х физический адрес формируется путем сложения базового адреса, заданного полем В команды, и смещением D.

Методы повышения производительности работы процессора.