- •© Издательство «Высшая школа», 1982предисловие

- •Полупроводниковые компоненты электронных цепей

- •Электропроводность полупроводников

- •Основные свойства и характеристик» полупроводников

- •Электрические переходы

- •1.7. Несимметричный р-л-пере- ход:

- •1 10. Энергетическая зонная диаграм-

- •Особенности и получение реальных р-п-переходов

- •Ние тока при изменении полярности напряжения (б):

- •Полупроводниковые диоды

- •Выпрямительные диоды

- •Импульсные диоды

- •Полупроводниковые стабилитроны

- •Туннельные диоды

- •Варикапы

- •Биполярные транзисторы

- •Рнс. 1.26. Эквивалентная схема для постоянного тока транзистора типа р-п-р, включенного по схеме с об

- •Транзистора при эмиттерном управ- лении (схема с об) (а) и базовом управлении (б)

- •§1.8. Биполярные транзисторы с инжекционным питанием

- •Тиристоры

- •Полевые транзисторы

- •Особенности компонентов электронных цепей в микроминиатюрном исполнении

- •Глава вторая элементы оптоэлектроники

- •Общие сведения

- •Управляемые источники света в цепях оптоэлектроники

- •Фотоприемники

- •Фоторезисторы

- •Фотодиоды

- •(В) и частотные (г) характеристики

- •Фототранзисторы

- •Световоды и простейшие оптроны

- •Глава третья усилители электрических сигналов

- •Общие сведения об усилителях электрических сигналов, их основных параметрах и характеристиках

- •Основные положения теории обратной связи применительно к усилителям

- •Статический режим работы усилительных каскадов

- •Усилительные каскады на полевых транзисторах

- •§ 3.5. Усилительный каскад на биполярном транзисторе с общим эмиттером

- •Позволяет получить наиболее высокий коэффициент усиления по напряжению:

- •Имеет невысокое входное и относительно большое выходное сопротивление;

- •Вносит фазовый сдвиг 180° в диапазоне «средних; (рабочих) частот.

- •Усилительный каскад на биполярном транзисторе с общей базой

- •Усилительный каскад на биполярном транзисторе с общим коллектором

- •§ 3.8. Усилительный каскад с эмиттерной связью

- •Дифференциальные усилительные каскады

- •Усилительные каскады с каскодным включением транзисторов

- •Управляемые источники тока и усилительные каскады на их основе

- •Усилительные каскады с трансформаторной связью

- •Мощные усилительные каскады

- •Многокаскадные усилители в интегральном исполнении

- •§ 4.3. Операционные усилители

- •Усилители, управляемые внешними сигналами

- •11 UbIlRi, 1% л# uBllB/r2.

- •£Cjrt Yi

- •Рио. 4.24. Схема сложного активного фильтра (а) и его лачх при снятии сигналов с вЧвыхода (б); нч-выхода (в); полосового выхода (г)

- •Нелинейные преобразователи электрических сигналов

- •Усилители с уменьшенным дрейфом нуля

- •Магнитоэлектронные преобразователи электрических сигналов

- •Выходного каскада усилителя магнитоэлектронного преобразователя (в)

- •.Устойчивость многокаскадных усилителен и коррекция их характеристик

- •Рнс. 4.37. Лачх первого звена (а) 'и лачх второго звена (б) усилителя

- •4.39. Лачх усилительного каскада аппроксимация экспериментально определенной лачх усилителя (б)

- •Глава пятая генераторы синусоидальных колебании

- •Общие сведения о генераторах синусоидальных колебаний

- •Генераторы типа lc

- •Генераторы типа rc

- •Автогенераторы с кварцевой стабилизацией частоты колебаний

- •Глава шестая линейные преобразователи импульсных сигналов

- •Общие сведения об импульсных процессах и устройствах

- •Пассивные линейные интегрирующие цепи

- •Интеграторы на основе операционных усилителей

- •, Рис. 6.15. Схема дифференцирующего устройства, применяемого на практике (а), и его лачх (б):

- •Укорачивающие цепи

- •Передача импульсов через rc-ц'епи

- •Глава седьмая электронные ключи

- •Диодные ключи

- •Рнс. 7.2. Схема диодного ключа, включенного в прямом направлении (а); зависимость распределения зарядов на базе от времени (б); характеристика переходных процессов в диодном ключе (в)

- •Транзисторные ключи

- •Транзисторные прерыватели

- •Анализ переходных процессов в транзисторе методом заряда базы

- •Анализ переходных процессов в транзисторном ключе

- •4 _ Циала (ж)

- •Ненасыщенные ключи

- •Транзисторные ключи на полевых транзисторах с управляющим р-л-переходом

- •— К'вост/'в нач

- •Ключи на мдп-транзисторах

- •Переходные процессы в ключах на полевых транзисторах с управляющим р-л-переходом

- •Переходные процессы в ключах на мдп-транзисторах

- •Глава восьмая нелинейные формирователи импульсов

- •§ 8.1. Ограничители на пассивных элементах

- •Ограничители на операционных усилителях

- •Общие сведения о логических элементах

- •Рис, 8.13. Передаточные характеристики неинвертирующего (а) и инвертирующего (б) логических элементов

- •Активные логические элементы

- •Триггеры

- •Триггер с эмиттерной связью

- •Формирователи напряжения прямоугольной формы на основе оу

- •Компараторы напряжения

- •Генераторы импульсов

- •Одновибраторы на основе логических элементов

- •А * с повышенной длительностью выходного импульса; б — на основе rs-триггера; в — с повышенной длительностью выходного импульса и малой длительностью стадии восста* новления

- •Одновибраторы на основе операционных усилителен

- •Мультивибраторы на основе логических элементов

- •«Вх! —Uaep — £ /вх Ai Al „ ,d 6 их л1

- •Генераторы прямоугольного напряжения на основе операционных усилителей

- •Генераторы линейно н ступенчато изменяющихся напряжений а

- •Размахом выходного напряжения Umi

- •Длительностью рабочего хода т9;

- •Длительностью обратного хода или временем воовтановления Tj

- •Рве. 9.14. Структурная (а) в принципиальная (б) схемы глин с кон- денсаторной ос в его диаграмма вапряжений(в)

- •Рис, 9.17. Принципиальная (в) я эквивалентная (б) схемы блэ- иинг-генератора

- •§ 9.7. Блокииг-генератор с трансформатором на сердечнике с прямоугольной петлей гистерезиса

- •Заключение

- •Литература

- •*Алфавитный указатель

- •4Оглавление

Активные логические элементы

В последнее время в цифровой аппаратуре в основном исполь зуют транзисторно-транзисторные логические элементы (ТТЛ), эмиттерно-связанные транзисторные элементы (ЭСТЛ), а также логические элементы на МДП-транзисторах. Резисторно-транзисторные и диодно-транзисторные логические элементы считаются неперспективными и выпускаются промышленностью для применения в аппаратуре, освоенной ранее.

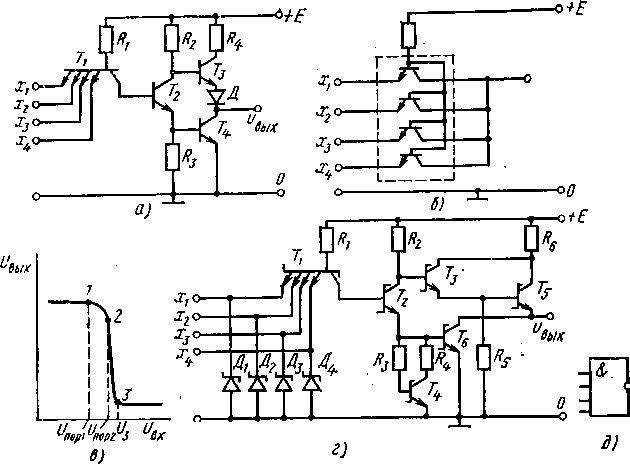

Рис. 8.15. Схема ТТЛ с четырьмя входами (а); эквивалентная схема многоэмит-» терного транзистора (б); передаточная характеристика логического элемента (в); схема логического элемента на транзисторах с барьером Шоттки (а); ус-, ловное обозначение четырехвходового логического элемента И—НЕ (б) . ‘

В интегральных транзисторно-транзисторных логических элемен* тах часто на входе включают многоэмиттерный транзистор (МЭТ), ко* торый одновременно выполняет функции диодного логического эле* мента и усилителя электрических сигналов.

Транзисторно-транзисторные логические элементы. Принципиальная схема четырехвходового элемента ТТЛ приведена на рис. 8.15, а. Транзистор 7\ отличается от обычного одноэмиттерного биполярного транзистора тем, что у него при изготовлении сделано несколько эмииу

теров. При этом эмиттеры расположены так, что их непосредственное взаимодействие через участок базы практически отсутствует, МЭТ является эквивалентом нескольких транзисторов, включенных так, как показано на схеме рис. 8.15, б.

Работу логического элемента можно рассматривать как в положительной, так и в отрицательной логике. При этом, как уже указывалось, логические элементы, выполняющие функцию И в положительной логике, в отрицательной логике выполняют функции ИЛИ, и наоборот.

Паспортное обозначение логических элементов, как правило, соответствует функции, реализуемой в положительной логике, поэтому в дальнейшем будем рассматривать только ее.

Многоэмиттерный транзистор ^ в ТТЛ в зависимости от уровней напряжений, поданных на его эмиттеры, может быть включен нормально или инверсно. Если на один или все эмиттеры МЭТ подано низкое напряжение, близкое к нулю (код «О» в положительной логике), то соответствующие эмиттерные переходы 7\ будут открыты, что характеризует нормальное включение транзистора. Через открытые эмиттерные переходы протекает базовый ток, определяемый сопротивлением резистора /?ь который в первом приближении (при U^3 И Я1 > Гэ.диф) равен

/б1 « E/Rt.

Источники входных сигналов х4 —х4 имеют внутренние сопротивления близкие к нулю.

К коллекторной цепи транзистора 7\ подключена база транзистора Т2, ток которой при запертом транзисторе Т2 равен /квог - Этот ток у кремниевых транзисторов достаточно мал, поэтому всегда выполняется условие / 61^213 ^ /кбо„ где й21э — коэффициент передачи базового тока транзистора 7\.

Следовательно, транзистор 7\ находится в состоянии глубокого насыщения и падение напряжения на нем близко к нулю. Это напряжение не может открыть транзистор Т2. Поэтому ток его эмиттера близок к нулю, а ток коллектора — к /кбо,. Напряжение U63i транзистора Tt близко к нулю, т. е. он заперт. Напряжение базы транзистора Т3 определяется из выражения

^бз= t/K2 = ^ —(^кво, + /оз) ^г ~ Е.

Транзистор Т3 открыт и в зависимости от параметров элементов схемы или насыщен, или находится на границе насыщения. Выходное напряжение отличается от +£ на величину, равную сумме падения напряжения на резисторе Rit падений напряжений на открытых транзисторах Тв и диоде Д:

Uзых ^ Е /кБО. Ri //кэз ^д>

где Ua — падение напряжения на открытом диоде.

Этот высокий уровень напряжения соответствует коду «1».

Внутренние сопротивления источников сигналов, подаваемых на входы х4—х4, настолько малы, что изменение напряжений на эмитте-

pax транзистора T, при различном количестве входов, имеющих низкий уровень напряжения, практически не отличается от напряжения, получаемого при нулевом сигнале на одном из эмиттеров. Поэтому при различном количестве входов, имеющих «О», UK3l остается малым и не может открыть транзистор Tt. Если на всех входах, кроме одного, имеется высокий уровень напряжения, то при увеличении напряжения на эмиттере, на котором ранее был низкий потенциал, до напряжения Uaopl (рис. 8.15, в) транзистор Тг из области насыщения выходит в активную инверсную область. При этом коллекторный переход смещен в прямом направлении, а все эмиттерные — в обратном.

В цепи резистор Яг — коллекторный переход транзистора Т\ — эмиттерный переход транзистора Т2 потечет ток, открывающий транзистор Тг и уменьшающий напряжение UK2 его коллектора. При этом транзистор Tt остается закрытым до тех пор, пока падение напряжения на резисторе /?, не достигнет значения, при котором эмиттерный переход транзистора 7^ отопрется. Это происходит при достижении входным напряжением значения (/пор8. При дальнейшем увеличении входного напряжения на участке UBPpi — и3 происходит увеличение тока транзистора Т2 и дальнейшее отпирание транзистора 7\. Снижение потенциала коллектора транзистора Т2, вызванное увеличением его тока, приводит к запиранию транзистора Т3, причем на участке 2—3 транзисторы Т3 и Tt открыты. Это вызывает увеличение тока и мощности потребляемых логическим элементом.

Для ограничения тока в переходных режимах включен ограничивающий резистор R^. При дальнейшем увеличении входного напряжения (выше U3) транзисторы Т2 и Т^ входят в насыщение, а транзистор Т3 запирается, так как напряжение UK2 в режиме насыщения не может открыть два последовательно соединенных р-п-перехода (переход база—эмиттер транзистора Т3 и диод Д). Диод Д вводят только для обеспечения надежного запирания транзистора Т3 и смещения уровня прй его открывании.

Если входное напряжение выше U3, то на выходе логического элемента будет малое напряжение, определяемое напряжением UK3i насыщенного транзистора Tt. Это соответствует коду «О» в положительной логике. Логический элемент выполняет функцию И—НЕ, так как код нуля появляется на выходе только тогда, когда на все входы поданы коды логической единицы. Непосредственно логическую функцию И выполняет Тъ а остальная часть схемы только обеспечивает нормальную работу этого транзистора. Причем, если, как в рассматриваемом случае, остальная часть схемы переворачивает фазу входного сигнала, т. е. выполняет операцию НЕ, она носит название инвертора. Условное обозначение элементов И—НЕ показано на рис. 8.15, д.

Основные схемотехнические отличия базовых элементов ТТЛ касаются выполнения инвертора. При этом обычно’ ставятся задачи улучшения переходных характеристик, повышения помехоустойчивости и нагрузочной способности, а также снижения потребляемой мощности. Для уменьшения входных токов транзистор 7\ выполня-

ют с малым инвереным коэффициентом передачи базового тока hzltJ ^ Ла1,.

Логические ТТЛ элементы имеют сравнительно высокое быстродействие, малые входные и большие выходные токи. Они хорошо работают на емкостную нагрузку, так как перезарядка конденсаторов осуществляется через низкоомную выходную цепь.

Недостатком их является кратковременное увеличение мощности, потребляемой в переходных режимах, что вызывает появление в цепях питания импульсов помех. Соответственно при увеличении рабочей частоты наблюдается повышение потребляемой мощности.

В быстродействующих логических элементах широко используют транзисторы и диоды с барьером Шоттки, в которых отсутствует накопление избыточных зарядов и не затрачивается время на их рассасывание.

Диоды Шоттки обычно вводят в схемы для предотвращения глубокого насыщения транзисторных ключей. Транзисторы с барьером Шоттки включают аналогично биполярным транзисторам о р-п-пере- ходами, а логические элементы, выполненные на их основе, не имеют принципиальных схемотехнических отличий. На рис. 8.15, а приведена схема логического элемента И—НЕ, выполненного на транзисторах с барьером Шоттки.

По принципу действия этот элемент аналогичен логическому элементу, показанному на рис. 8.15, а, и отличается от него только тем, что в выходном каскаде использован составной транзистор Та, Т6, обеспечивающий повышенный выходной ток, а в эмиттерную цепь включен каскад с ОЭ на транзисторе 7\, улучшающий форму переходной характеристики и приближающий ее к прямоугольной.

Для повышения помехоустойчивости логических элементов в эмиттерные цепи МЭТ часто вводят диоды (Д^—Д^ на рис. 8.15, г), включенные в обратном направлении для сигналов логического нуля или единицы. Они открываются только в том случае, если напряжения на входах логического элемента меняют свой знак на противоположный. Последнее связано с особенностями переходных процессов в различных электрических цепях. Из-за наличия паразитных индуктивностей и емкостей в цепях, к которым подключены входы логических элементов, при резких изменениях входных сигналов возникают затухающие колебания. Начальная амплитуда их может быть значительной, что вызывает ложное срабатывание логического элемента. Однако при наличии диодов на входе МЭТ этого н& происходит, так как первая же отрицательная полуволна открывает соответствующий диод при входном напряжении порядка 0,8 В. Следующие затухающие положительные и отрицательные полуволны будут иметь амплитуду, меньшую 0,8 В. Так как уровень кода логической единицы в ТТЛ значительно больше 0,8 В, эта помеха не вызовет его ложного срабатывания.

Для расширения функциональных возможностей одного «корпуса» микросхемы промышленность выпускает логические элементы, выполняющие все три логические функции: И—ИЛИ—НЕ. Принципиальная схема такого логического элемента приведена на рис. 8.16, а.

Функцию И здесь выполняют многоэмиттерные транзисторы Т^ Т2, а функцию ИЛИ — транзисторы Т8, Г,. Принцип работы каждой пары транзисторов практически не отличается от работы транзисторов 7\, Tt схемы, приведенной на рис. 8.15, а. Для появления кода «О» на выходе логического элемента безразлично, открыт только один из транзисторов Г8, Tt или они открыты оба. Это соответствует функции ИЛИ.

Один такой логический элемент позволяет реализовать и более сложную логическую функцию 2—2 И—ИЛИ—НЕ16.

Рис. 8.16. Схемы логического элемента 2—2 И—ИЛИ—НЕ (а) и и четырехвходового расширителя по ИЛИ (б)

В состав серий интегральных микросхем обычно входят функциональные узлы, выполняемые в отдельных корпусах, которые предназначены для расширения функциональных возможностей микросхем (расширители по входу, увеличивающие коэффициент объединения Коб» и буферные усилители, увеличивающие коэффициент разветвле- НИЯ Краз)-

Для серий ТТЛ характерно наличие только расширителей по входу. На рис. 8.16, б показан четырехвходовой расширитель по ИЛИ, в состав которого входят МЭТ Т, и транзистор Ts, который подключают к выводам /, 2 схемы (рис. 8.16, а) параллельно транзисторам Т3, Tt. Это приводит к тому, что количество входов по ИЛИ увеличивается до трех, так как для получения на выходе кода «О» безразлично, какой из транзисторов Ta, Tt, Ts будет открыт и насыщен, и добавляется элемент И, имеющий четыре входа. Логический элемент с подключенным расширителем по ИЛИ будет выполнять функцию 2—2—4 И—ИЛИ—НЕ.

Отдельные серии интегральных микросхем имеют напряжения питания и параметры, обеспечивающие непосредственное подключение

микросхем различного назначения, в том чиеле и логических элементов, без их дополнительного согласования. Это существенно упрощает и удешевляет проектирование устройств, выполненных на их основе. В то же время при применении в составе устройства микросхем разных серий может возникнуть необходимость во введении дополнительных источников питания и схем согласования уровней. В табл. 8.1 приведены параметры, характеризующие ТТЛ некоторых серий, выпускаемых промышленностью,.

Таблица 8.1

Параметры |

#ерии |

||||

общего применения |

высокого быстродействия |

микро* мощные |

с диодами Шоттки |

||

133 |

К165 |

130 |

134 |

530 |

|

Входной ток «0» /вх, мА |

—1,6 |

— 1,6 |

—2,3 |

—0,18 |

2 |

Входной ток «1»/вх , мА |

0,04 |

0,04 |

0,07 |

0,012 |

0,06 |

Выходное напряжение «0» (/вых, В |

0,4 |

0,4 |

0,35 |

0,3 |

0,5 |

Выходное напряжение «1» (/вых, В |

2,4 |

2,4 |

2,4 |

2,3 |

2,7 |

Коэффициент разветвления по выходу /Срез |

10 |

10 |

10 |

10 |

10 |

Коэффициент объединения по входу ИЛИ Коб Время задержки распространения, нс: |

8 |

8 |

8 |

2 |

|

р.о з. р |

15 |

15 |

юА |

100 |

5 |

/0,1 *3. р |

22 |

22 |

10 |

100 |

4,5 |

Частота переключения, мГц |

10 |

10 |

30 |

3 |

50 |

Допустимый уровень помехи Дип, В |

0,4 |

0,4 |

0,4 |

0,35 |

0,5 |

Напряжение питания, В |

5 |

5 |

5 |

5 |

5 |

Средняя статическая потребляемая мощность, мВт |

22 |

22 |

44 |

2 |

19 |

При использовании логических элементов ТТЛ для повышения помехоустойчивости свободные входы рекомендуется подключать к источнику питания +5 В через резистор 1 кОм, причем к каждому резистору допускается подключение 20 входов. Для уменьшения помех по цепи питания к точке подключения группы логических элементов к напряжению питания дополнительно подсоединяют развязывающий конденсатор (один на группу не более чем из 10 элементов с емкостью не менее 0,1 мкФ на одну ИС).Транзисторно-транзисторные логические элементы благодаря простоте, технологичности, высокому быстродействию и удовлетворительной помехозащищенности в настоящее время являются наиболее распространенными.

Транзисторные логические элементы с эмиттерной связью (ЭСТЛ, ЭСЛ). Эти элементы иногда называют элементами на переключателях тока (ТПТЛ). Они имеют высокое быстродействие, высокое входное и низкое выходное сопротивления. Мощность, потребляемая ими отисточника питания, мало зависит от состояния элемента. Этим обеспечивается уменьшение уровня помех, проходящих по цепи питания. Высокое быстродействие обусловлено тем, что в ЭСТ Л. транзисторные ключи работают на границе насыщения. Низкое выходное сопротивление получают за счет введения в схему эмиттерных повторителей. Одна из схем подобного логического элемента показана на рио. 8.17, а.

Элемент имеет три входа: хи х2, х9. Если транзисторы Тъ Тг, Т9 закрыты (на входах — сигнал логического нуля), то ток протекает

Рис. 8.17. Схема логического элемента ЭСТЛ (а); схема преобразователя уровня для согласования ТТЛ и ЭСТЛ (6) и его обозначение (в)

только через транзистор Tt, создавая на эмиттерном сопротивлении R9 падение напряжения близкое к потенциалу базы.

Если на один из входов, например х1г подать положительный сигнал UBX, удовлетворяющий условию UBI > l^Ra, то транзистор 7\ закроется, а весь ток будет протекать через транзистор 7\. Напряжение «вых1 станет низким, а иВЫ1! — высоким.

В зависимости от того, с какой точки снимается выходной сигнал («вых1 или ивыхз) реализуются функции ИЛИ—НЕ или ИЛИ (ЗИЛИ—HE/ИЛИ). Транзисторы Т9, Тв, к эмиттерным цепям которых подключается нагрузка, выполняют роль эмиттерных повторителей, обеспечивающих малое выходное сопротивление логического элемента.

Характерной особенностью ЭСТЛ является то, что у них заземляют коллекторную цепь. Этим обеспечивают повышение помехоустой- 412чивости и меньшую зависимость уровней выходного напряжения от наводок по цепи питания. Для получения достаточно малых выходных сопротивлений и согласования с кабелем, имеющим волновое сопротивление 50 Ом, эмиттеры транзисторов- Т6 и Т9 подключают к дополнительному источнику напряжения — (/см = 2 В через внешние резисторы /?н = 50 Ом. Введение дополнительного источника позволяет снизить мощность, рассеиваемую в резисторах RH, и повысить экономичность вхемы.

Все входы логического элемента через резисторы /?5 —R-, соединены с источником питания —Е. Это позволяет оставлять свободными выводы, которые не используются в конкретной схеме.

В сериях ЭСТЛ, выпускаемых промышленностью, например 100, К500, напряжение питания Е = 5,2 В; (/вых — —0,98 В; Дмп = = —1,63 В, максимально допустимое напряжение помех Дмп = = 125 мВ; /‘х = 100 4-500 мкА; /в\ = 0,5 мкА; КРа3 > 15; t^1 « « 3 нс; Й.'р « 3 нс; потребляемая мощность Рпот & 354-130 мВт на вентиль.

Из приведенных усредненных параметров ИС ЭСТЛ видно, что по быстродействию, входному току и предельно достижимому коэффициенту разветвления по выходу они превосходят ИС ТТЛ, уступая им по помехоустойчивости и потребляемой мощности. Кроме того, низкое выходное сопротивление позволяет подключить к их выходу сравнительно большую емкостную нагрузку.

Для совместного использования логических элементов различного типа приходится применять дополнительные преобразователи уровня.

Принципиальная схема преобразователя уровня для перехода от ТТЛ к ЭСТЛ элементам приведена на рис. 8.17, б. Напряжение питания ИС ТТЛ Ei подключено к коллектору транзистора 7\, а напряжение питания ИС ЭСТЛ Ег подано на транзисторы Тг—Т3.

Преобразователь уровня (ПУ) состоит из эмиттерного повторителя на транзисторе 7\ с входными диодами Дх—Д3, дифференциального усилителя на транзисторах Т2, Т3, работающего Bi режиме переключения тока, и эмиттерных повторителей на транзисторах Т9, Тй. При этом эмиттерный повторитель Т9 поддерживает на базе транзистора Т3 потенциал, заданный делителем из резисторов й9, R9.

Если хотя бы на один из диодов Дх—Д3 подан код логического нуля ТТЛ-элемента (порядка 0,4В) , то соответствующий диод будет открыт и потенциал базы транзистора 7\ будет близок к потенциалу Е2 общего вывода:

где (/д — падение напряжения на открытом диоде.

Потенциал эмиттера эмиттерного повторителя на транзисторе Тй меньше потенциала базы на Uв3 m Ua, поэтому U9 = 0.

К базе транзистора Т9 приложено напряжение

к

(/б2 ^2

■Kg

+^3оторое меньше напряжения базы транзистора Ts

Т

1^63 й ^2

«»+«.

^бэЗ"

ранзистор Та открыт и насыщен, а транзистор Т* заперт. В итоге выходное напряжение

//О Р ^4 -

-^бэ4.

При подаче на все диоды кода «1», который для ТТЛ соответствует напряжению 2,4 В, потенциал базы и эмиттера транзистора Tt увеличивается на 2,4 В. Это, в свою очередь, вызывает увеличение потенциала базы транзистора Т2, который открывается и его ток создает на сопротивлении Rs падение напряжения

и&Ь ^/к2 ^5 = (— £г+ иэъ

Это напряжение больше потенциала базы транзистора Т3, U^ ^ ^ t/бз, что приводит к запиранию последнего. Выходное напряжение становится равным

^вых = —^бо, Л<— ^бМ«

Выбором режимов работы транзистора ПУ добиваются, чтобы на' пряжения t/вых и t/вых соответствовали требованиям к входным на" пряжениям кодов «1» и «О» для серий ЭСТЛ.

Аналогично строят ПУ для перехода от ЭСТЛ к ТТЛ. Условное графическое изображение преобразователя уровней приведено на рис. 8.17, в.

Так как в настоящее время выпуск интегральных логических элементов хорошо освоен промышленностью, подробно останавливаться на методах их расчета нет необходимости. Все интересующие зависимости могут быть получены самостоятельно на основе сведений о диодных и транзисторных ключах.

Логические элементы на МДП-транзисторах. Существенными преимуществами логических элементов на МДП-транзисторах перед логическими элементами на биполярных транзисторах являются: малая мощность, потребляемая входной цепью, в результате чего соответственно возрастает коэффициент разветвления по выходу ^pИ > » 10 4-20; простота технологического процесса изготовления; сравнительно низкая стоимость и малая потребляемая мощность.

Однако по быстродействию даже лучшие логические элементы на МДП-транзисторах уступают схемам на биполярных транзисторах. Это обусловлено тем, что у МДП-транзисторов имеются сравнительно большие входные емкости, на перезарядку которых затрачивается определенное время. Кроме того, выходное сопротивление у открытого МДП-транзистора значительно выше, чем у биполярного, что увеличивает время зарядки конденсаторов нагрузки и ограничивает нагрузочную способность логического элемента.

В известных технических решениях логических элементов широко используют последовательное (ярусное) включение МДП-транзисторов, когда в цепь между нагрузкой и землей включено несколько транзисторов. Это несколько усложняет технологию изготовления элементов, однако позволяет создать логические схемы, удобные для построения сложных функциональных узлов.

На рис. 8.18,0, в показаны простейшие схемы логических элементов на МДП-транзисторах с каналом p-типа, а на рис. 8.18, б, г — соответственно их условные графические обозначения.

В обеих схемах транзистор Та выполняет роль нелинейного нагрузочного сопротивления. Если в схеме на рис. 8.18, а на оба входа Xj и х2 поданы малые напряжения, что соответствует коду «О»

Рис. 8.18. Схемы простейших логических элементов на МДП-транзисторах (а, в) и их условные обозначения (б, г)

в отрицательной логике, транзисторы 7\ и Т2 закрыты и на выходе F будет потенциал логической единицы, близкий к —Е. При подаче на любой из входов отрицательного потенциала (кода «1») соответствующий транзистор (Ti или Т2) открывается и появляется положительный перепад напряжения. На выходе устанавливается потенциал логического нуля. Цепь реализует функцию ИЛИ—НЕ в отрицательной логике.

В схеме на рис. 8.18, в для получения на выходе логического нуля необходимо одновременно на оба входа X! и х2 подать потенциал логической единицы.

Более сложные логические элементы на МДП-транзисторах представляет собой различные комбинации этих двух основных схем.

Существенное улучшение параметров логических элементов можно получить за счет введения дополняющих МДП-транзисторов с каналом другого типа электропроводности (МДПДТ)17.

Логические элементы на дополняющих МДП-транзисторах представляют собой систему МДП-транзисторов с п- и p-каналами, затворы которых включены параллельно, а сами транзисторы — последовательно. Когда один из транзисторов открыт приложенным напряжением, второй оказывается закрытым и результирующий ток через систему в статическом режиме определяется только током утечки за-

крытого транзистора. Он равен нескольким десятым—сотым долям микроампер.

Логические элементы, выполненные на основе КМДП-приборов, в статическом режиме потребляют микроваттные мощности. Кроме того, они имеют хорошую помехоустойчивость и высокую нагрузочную способность. Работоспособность их сохраняется при изменениях напряжений питания от 3 до 15 В.

На рис. 8.19, а, б показаны двухвходовые схемы на МДПДТ, выполняющие логические операции ИЛИ—НЕ и И—НЕ в положительной логике.

Рассмотрим работу первой схемы (рис. 8.19, а). При подаче на вход Xi кода «1» (положительное напряжение порядка 4-Е) транзис-

Рис. 8.19. Схемы базовых логических элементов МДПДТ-ИС

тор 7\, имеющий канал n-типа, откроется а транзистор 7^ с каналом p-типа закроется. На выходе появится потенциал, близкий к нулевому, соответствующий коду «О» в положительной логике. Аналогично, при подаче кода «1» на вход х2 на выходе появится код «О».

В ряде случаев МДПДТ усложняют, включая последовательно дополнительный нагрузочный транзистор. Такой класс МДП-схем иногда условно обозначают как МДПДТН-ИМО. Они позволяют реализовать сложные логические функции при минимуме необходимых компонентов.

Здесь МДП-транзистор выполняет роль нагрузочного транзистора. Остальная часть схемы по принципу действия аналогична рассмотренной выше.

Наиболее перспективные элементы серии МДПДТ (КМДП) характеризуются следующими электрическими параметрами.

Входные токи /2Х = —0,054-0,1 мкА; /вХ = 0,054-0,1 мкА.

Выходные напряжения (/?ых = 0,34-0,5 В; U^ = 7,74-8,2 В.

Время задержки распространения t^ = 2004-250 нс; й/р = 2004 250 нс.

Допустимое напряжение помехи Д«п = 0,9 В.

Коэффициент разветвления по выходу /<раз = 50.

Мощность, потребляемая одним элементом в статическом режиме, РПОт = 1 мкВт

.Из приведенных количественных характеристик видно, что логические элементы МДПДТ имеют наиболее высокую помехоустойчивость, наибольший перепад уровней логического нуля и единицы и рассеивают наименьшую мощность. Последнее позволяет повысить степень интеграции создать на их основе схемы, содержащие более 104

элементов на одном кристалле.

Интегральная технология позволяет объединить МДП- и биполярные транзисторы и тем самым устранить недостатки тех и других групп логических ИМС.

Д

большим запасом помехоустойчиво-

Рис. 8.20. Схемы логических элементов на биполярных МДП-транзисторах

ействительно, как было показано выше, логические элементы наМДП-транзистор ах отли чаются сти, но имеют низкое быстродействие при работе на емкостную нагрузку. ТТЛ и ЭСТЛ, построенные на биполярных транзисторах, имеют малый запас помехоустойчивости, но хорошо работают на емкостную нагрузку. Объединен и е положи тел ьных

свойств этих схем позволяет создать логические элементы с высокой помехоустойчивостью и достаточно высоким

быстродействием при работе

на емкостную нагрузку. При этом мощность, потребляемая в стати

ческом режиме, изменяется незначительно.

На рис. 8.20, а представлена одна из схем логических элементов на МДП- и биполярных транзисторах. В ней на выходе логического элемента на МДП-транзисторах включен эмиттерный повторитель на биполярных транзисторах по схеме с дополнительной симметрией. В схеме на рис. 8.20, б показан другой возможный вариант таких схем, где каждая пара МДП-и биполярного транзисторов образуют комбинированную схему составного транзистора, в которой ток стока полевого транзистора является базовым током соответствующего биполярного транзистора. В итоге ток стока усиливается в 1 + й21э раз и нагрузочная емкость заряжается приблизительно в I + Л21э раз быстрее. При использовании логических МДП-элементов совместно с ТТЛ и ЭСТЛ в схему необходимо вводить преобразователи уровня.