- •2. Основные понятия алгебры логики

- •3. Цифровые интегральные микросхемы

- •4. Логические элементы на кмоп-транзисторах

- •5. Схемотехника интегральных схем инжекционной логики и эсл

- •6. Триггеры

- •7. Счетчики

- •8. Регистры

- •9. Мультиплексоры и демультиплексоры

- •10. Шифраторы и дешифраторы

- •11. Арифметические устройства

- •12. Импульсные устройства на имс

- •13. Запоминающие устройства

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

9. Мультиплексоры и демультиплексоры

Рис. 9.1. Мультиплексор 2:1

Рис. 9.2. Структура мультиплексора 4:1 (а) и условное графическое обозначение мультиплексора 8:1 (б)

Рис. 9.3.Пирамидальный двухступенчатый мультиплексор 32:1

Рис. 9.4. Мультиплексор с использованием разрешающих входов

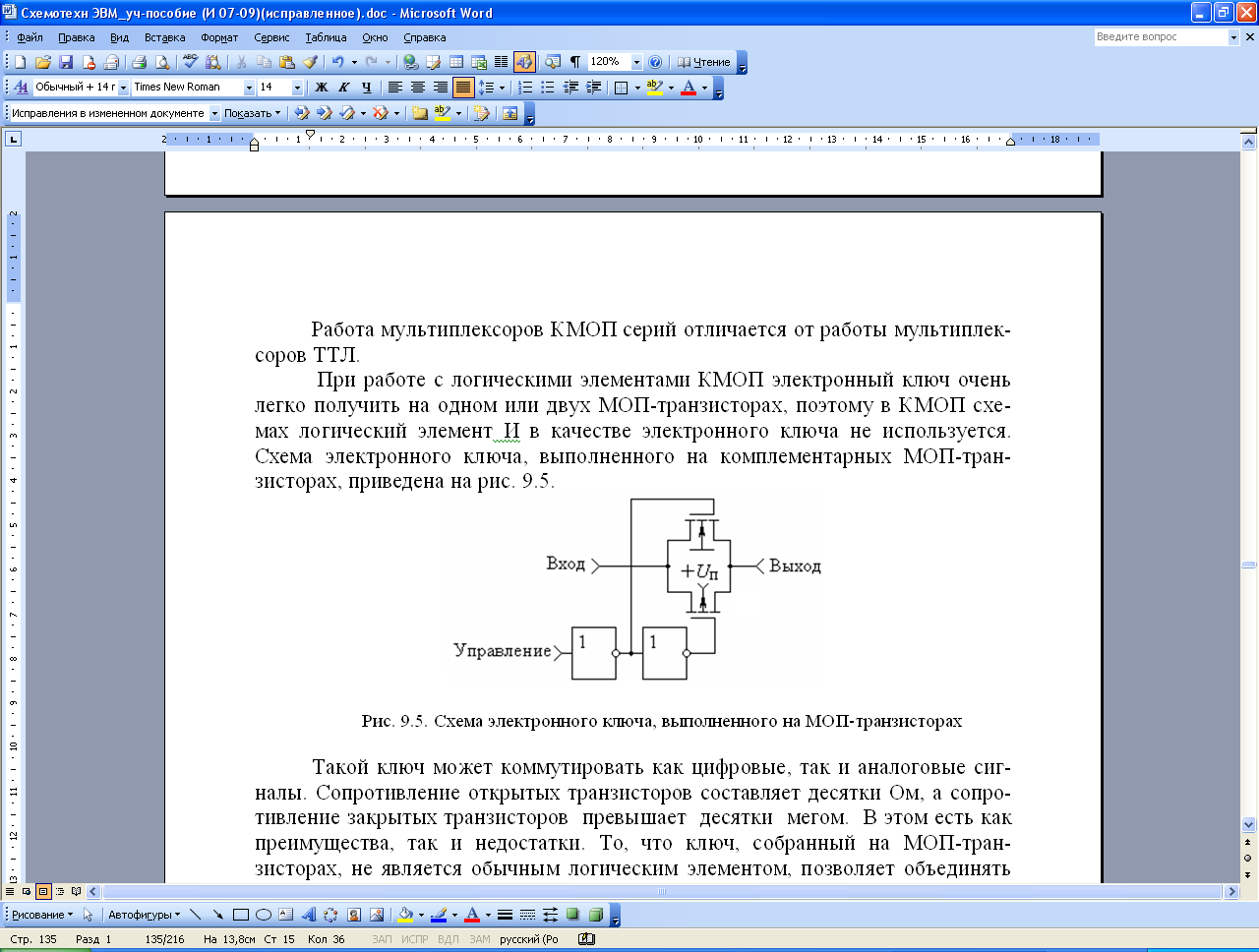

Рис.9.5. Схема электронного ключа выполненного на МОП транзисторах

Рис. 9.6. Мультиплексор, управляемый двоичным кодом

а б

Рис. 9.7. Мультиплексоры К561КП1 и К156КП1: а – структурная схема; б – условное обозначение

Рис. 9.8. Демультиплексоры 1:2 (а) и 1:4 с разрешающим входом (б и в)

Рис. 9.9. Демультиплексирование шины на четыре приемника

Рис. 9.10 Совместное применение мультиплексора и демультиплексора

10. Шифраторы и дешифраторы

Таблица 10.1

-

Унитарный код

Двоичный код

SB1

SB2

SB3

SB4

SB5

SB6

SB7

SB8

Q4

Q3

Q2

Q1

1

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

1

0

0

0

1

0

0

0

0

0

1

0

0

0

0

0

0

1

0

0

0

0

1

0

1

0

0

0

0

0

1

0

0

0

1

1

0

0

0

0

0

0

0

1

0

0

1

1

1

0

0

0

0

0

0

0

1

1

0

0

0

Рис. 10.1. Шифратор на диодах

Рис. 10.2. Функциональная схема шифратора

Рис. 10.3. Схема выделения старшей единицы

Рис. 10.4. Упрощенная структура приоритетного шифратора и его обозначение

Таблица10.2

|

ВХОД |

ВЫХОД | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

X |

X |

X |

X |

X |

X |

X |

X |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

0 |

X |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

X |

X |

X |

X |

X |

X |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

|

0 |

X |

X |

X |

X |

X |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

|

0 |

X |

X |

X |

X |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0 |

X |

X |

X |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

|

0 |

X |

X |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

0 |

X |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

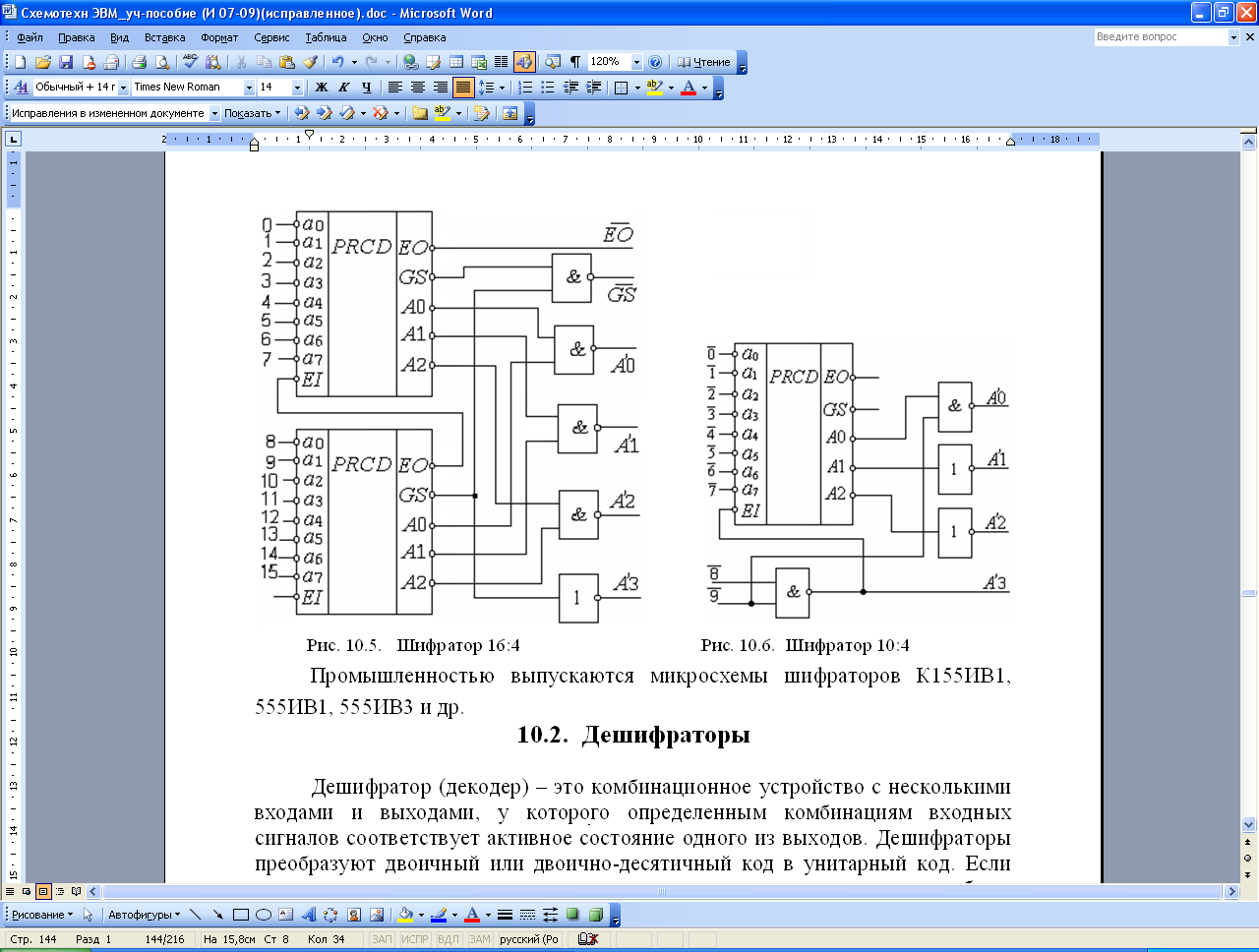

Рис. 10.5. Шифратор 16:4

Рис. 10.6. Шифратор 10:4

Рис. 10.7. Дешифратор 3-8: а – условное обозначение; б – структура

Рис. 10.8. Разрешение через прямой и инверсный входы одного из разрядов

Рис. 10.9. Разрешение через дополнительные входы элементов И

Рис. 10.10. Двухкаскадный дешифратор 5 – 32

Рис. 10.11. Матричный дешифратор

Рис. 10.12. Дешифратор с использованием в первом каскаде разрешающих

входов

Рис. 10.13. Схема дешифратора 155ИД4

Рис. 10.14. Варианты подключения дешифратора 155ИД1