Встроенная блочная память

Состоит из столбцов блоков памяти M4K, каждый из которых имеет объем 4608 бит. Блоки M4K включают входной регистр, который синхронизирует запись и выходной регистр для конвееризации и повышения производительности микросхемы. Выходной регистр может быть не задействован, так что сигналы будут проходить в обход него, но входной используется всегда. Каждый блок M4K может реализовывать различные типы памяти с проверкой четности или без нее: двухпортовая память, однопортовая память RAM или ROM, FIFO-буфер. При реализации двухпортовой памяти возможны два варианта – true dual-port и simple dual-port режимы. В режиме simple dual-port возможно одновременное выполнение операции чтения и записи, в true dual-port режиме возможна любая комбинация одновременных операций – две записи, два чтения, одна запись и одно чтение, причем операции могут происходить на двух различных тактовых частотах. В однопортовом режиме одновременное выполнение операций записи и чтения невозможно. Также блоки M4K поддерживают различную конфигурацию по ширине слов данных и, соответственно, их количеству. Доступны конфигурации 4K1, 2K2, 1K4, 5128, 5129, 25616, 25618, 12832, 12836, приче последние две не оддерживаются в true dual-port режиме. При записи в блоки M4K имеется возможность перезаписать только часть байт с помощью порта Byte enable, позволяющего наложить маску. Замаскированные байты не изменять своих значений. Также блоки M4K имеют линию Address clock enable, используемую для удержанию адреса в течение всего времени, пока сигнал на линии принимает единичное сосояние. В таблице риведены все возможные режимы тактирования памяти на основе блоков M4K.

|

Режим |

Описание |

|

Independent |

Для каждого порта A и B используется своя тактовая частота. |

|

Input/Output |

На каждом из двух портов A и B одна тактовая частота используется для входных регистров, а другая для выходных |

|

Read/Write |

Одна тактовая частота используется для записи, а другая для для чтения |

|

Single |

Единственная тактовая частота и единственный сигнал разрешения тактирования используются для всех операций на обоих портах. Сигнал асинхронная очистка для регистров памяти в этом режиме не может использоваться |

Микросхемы семейства Cyclone II содержат от 26-ти до 250-ти блоков памяти; в микросхеме EP2C20 содержатся 2-е колонки с общим числом 52-а блока M4K.

Рисунок 9

Встроенные умнодители

Встроенные умножители ПЛИС семейства Cyclone II отимизированы для интенсивного использования в алгоритмах цифровой обработки. Встроенные умножители можно исользовать в одном из двух основных режимах выполнения операций, либо как один 18-ти битный умножитель, либо как два независимых 9-ти битных умножителя. Максимальная тактовая частота работы умножителей составляет 250 Мгц, когда используются его входные и выходные регистры. Микросхемы семейства Cyclone II имеют от одной до трех колонок умножителей.

На рисунке 10 представлена архитектура встроенного умножителя.

Рисунок 10

Он состоит из блока умножения, входных и выходного регистров, входного и выходного интерфейсов. Каждый операнд может иметь знаковый или беззнаковый формат, что задается с помощью сигналов signa и signb. Логическая единица на этих портах показывает, что число на соответствующем порте имеет знаковый формат, логический ноль – беззнаковый. Результат умножения будет иметь знаковый формат, если хотя бы один операнд имеет знаковый формат и беззнаковый в противоположном случае. Сигналы signa и signb являются общими для всех умножителей. Сигналы signa и signb могут динамически изменяться в процессе работы микросхемы. Результат умножения на выходе имеет полную точность вне зависимости от формата и может быть помещен в выходной регистр умножителя.

Структура портов ввода/вывода

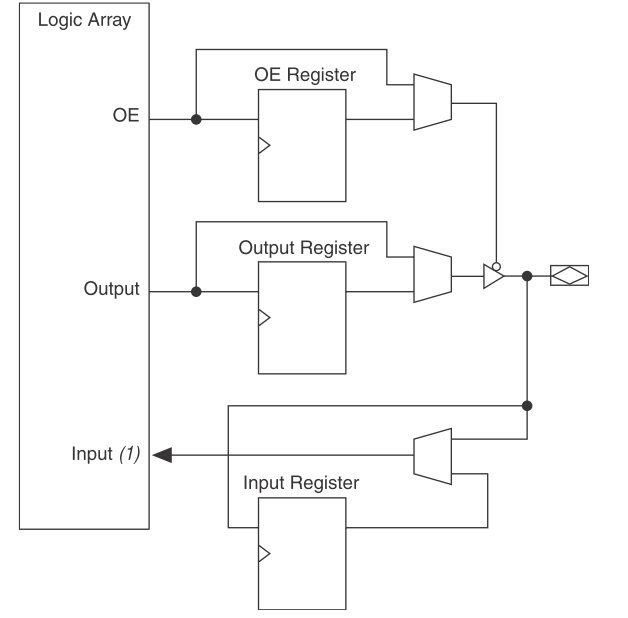

Элементы ввода/вывода (ЭВВ) состят из I/O-буфера и трех регистров – входного, выходного и выходного разрешающего регистра. Соответственно, ЭВВ может использоваться как входной порт, выходной, либо двунаправленный. Структурная схема ЭВВ приведена на рисунке 11.

Рисунок 11

ЭВВ расположены в I/O-блоках по всей периферии микросхемы. В горизонтальных I/O-блоках сгруппировано до пяти ЭВВ, в вертикальных – до четырех. Первые имеют связь с горизонтальными, вертикальными (только C4) и прямыми межсоединениями, вторые – только с вертикальными межсоединениями.

Рисунок 12

На рисунках 12, 13 показано, как, соответственно, горизонтальный и вертикальный I/O-блоки соединяются с логическим массивом.

Рисунок 13

К горизонтальным и вертикальным I/O-блокам подходит 7 шин контрольных сигналов и сигналов данных шириной 5 и 4 в соответствии с числом ЭВВ в этих блоках. Это сигналы:

-

линии выходных данных io_dataout,

-

выходные линии разрешения io_coe,

-

входные линии разрешения тактирования io_cce_in,

-

выходные линии разрешения тактирования io_cce_out,

-

тактовые линии io_cclk,

-

линии асинхронного сброса io_caclkr

-

линии синхронного сброса io_csclkr.

Каждый ЭВВ имеет два входа данных io_datain, один – комбинационный, другой – триггерный. Шесть тактовых линий io_clk рапределяют тактовые импульсы от глобальной тактовой сети к каждому ЭВВ. Каждый контрольный сигнал может использоваться либо напрямую, либо инвертироваться, выбор происходит с помощью мультиплексоров, как оказано на рисунке 14.

Рисунок 14

Выходные буферы I/O-выводов поддерживают программирование силы тока для ряда стандартов, таких как LVTTL, LVCMOS, а также SSTL-2, SSTL-18 HSTL-18, HSTL-1.5 классов I и II. Верхнее и нижнее значения силы тока для этих стандартов различно, но наименьшее значение составляет 2 мА, наибольшее – 24 мА. Использование наименьших значений обеспечивает увеличение времени нарастания сигнала на приемном конце, что приводит к уменьшению шумов и искажений сигналов.

Также I/O-выводовы поддерживают удержание состояния шины (bus-hold feature) с помощью специальной цепи. В этом случае ее применения нет необходимости использовать подтягивающие резисторы, т.к. цепь удержания сохраняет предыдущее состояние ни шине. Цепи удержания не используются на тактовых выводах ПЛИС.

При необходимости на I/O-выводах можно использовать встроенные подтягивающие резисторы номинальным сопротивлением 25 кОм, которые подтягивают выходное напряжение на выводах к напряжению питания соответствующего банка ПЛИС. Использование поддтягивающих резисторов возможно только при отключенной цепи удержания состояния.