- •Руководство по ghdl и gtKwave для начинающих Вступление

- •Введение

- •Часть 1. Установка по

- •Часть 2. Анализ 1-го теста. Определение алгоритма построения программной модели.

- •Часть 3. Анализ 1-го теста. Запуск компилятора и обработка полученного файла.

- •Часть 4. Анализ 1-го теста. Разработка тестового файла.

- •Часть 5. Анализ 1-го теста. Компиляция тестового файла. Верификация.

- •Часть 6. Анализ 2-го теста.

- •Часть 7. Анализ 3-го теста.

- •Часть 8. Общие замечания.

- •Список литературы

Руководство по ghdl и gtKwave для начинающих Вступление

Вначале хотелось бы отметить, что представленное руководство не является полным описанием языка VHDLили тестовой средыGTKwave. Для ознакомления с полным перечнем возможностей можно воспользоваться литературой указанной в ссылках. Данная работа предназначена для ознакомления пользователя, впервые столкнувшегося с языкомпрограммированияПЛИС.

Поэтому в представленном руководстве внимание уделяется лишь базовым понятиям, которые необходимы в первую очередь. К ряду таких понятий будут отнесены вопросы синтаксиса, алгоритм написания действующейпрограммной модели, необходимые команды и перечень действий для успешного тестирования разработанного продукта.

Введение

ПЛИС – программируемые логические интегральные схемы, в общих чертах это устройства, имеющие возможность для их программирования (то есть реализации функций другого цифрового устройства на основе логических вентилей). К основным языкам программирования относятся: Verilog,VHDL,AHDL(этот язык является уникальным и предназначен для программирования лишь в средах фирмыALTERA).

В предложенном руководстве для описания тестовых примеров выбран язык VHDL. Этот выбор обусловлен его широким кругом использования и большим функциональным уровнем.

Часть 1. Установка по

ПО, предлагаемое для использования, вместе с инструкциями по установке расположено в папке “FORinstall”.

Часть 2. Анализ 1-го теста. Определение алгоритма построения программной модели.

Прежде чем производить компиляцию и верификацию (анализ тестовых сигналов), требуется сначала разработать программную модель устройства.

Для этого создаем файл с расширением “.vhdl”. Затем этот файл открываем текстовым редактором (Блокнот).

Примечание: забегая вперед, следует отметить, что имя файла лучше выбирать так, как будет назван программируемый объект. (func.vhdlдолжен реализовывать объектfunc). Это условие не является обязательным, но заметно упрощаетработуразработчика.

Для создания в открытом файле программного объекта требуется выполнить следующую группу действий:

подключить соответствующие библиотеки и и используемые пакеты данных.

описать «входы и выходы» разрабатываемого устройства

описать архитектуру (логику действий, выполняемых устройством) объекта.

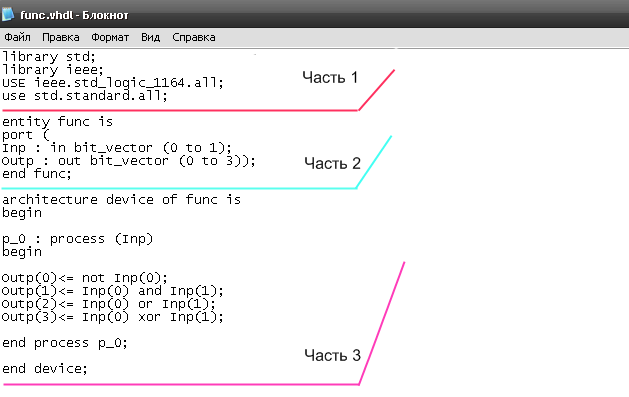

Рассмотрим расположение этих составных частей на первом тестовом примере (файл func.vhdl)

Примечание: все рассматриваемые примеры расположены в папке testи распределены по папкам с соответствующими названиями.

Рассматриваемый пример имеет следующий

вид:

На представленном изображении отображено деление программного объекта на основные части.Рассмотрим каждую из них отдельно:

Как отмечалось ранее, в первой части производится перечисление используемых библиотек и пакетов. Объявление библиотек производится с помощью ключевого слова library, после него указывается имя выбранной библиотеки. Для объявления пакетов используется ключевое словоuse. Наиболее часто используемыми библиотеками являютсяstdиieee, а пакетами -ieee.std_logic_1164, std.standard.

Вторая часть программной модели представляет описание «внешнего вида» устройства, то есть присвоение объекту названия (идентификатора) и перечисление его портов ввода–вывода. Для создания объекта используется следующая запись:

entityидентификатор объектаis

endидентификатор объекта;

Представленная запись верна для случая, когда не требуется перечислять порты ввода-вывода устройства. Однако на практике это требуется не так часто, поэтому используют ключевое слово port:

entityидентификатор объектаis

port (порты ввода и вывода, указанные через запятую);

endидентификатор объекта;

В представленном примере для сокращения перечисления используется понятия битового вектора (несколько сигналов, собранных в одну шину данных). Рассмотрим синтаксис представления портов ввода и вывода подробнее:

В тестовом примере Inp– идентификатор шины данных,in– спецификатор, указывающий входной или выходной это порт,bit_vector (0 to 1)– тип данных, обозначающий битовый вектор разрядности от 0 до 1, то есть разрядности два.

Примечание: в языке VHDLимеется множество типов данных, позволяющих подробно описать модель устройство на разных уровнях его проектирования. Среди типов данных имеются числовые, составные, битовые, булевые, физические типы (одним из встроенных таких типов является тип, описывающий время) и многие другие.

Третья часть описывает архитектуру объекта и имеет следующий синтаксис объявления:

architectureидентификатор архитектуры of идентификатор объекта is

begin

endидентификатор архитектуры;

Заметим, что идентификатор объекта должен соответствовать идентификатору, используемому во второй части (название объекта).

В тестовом примере используется следующая запись процесса:

p_0 : process (Inp)

begin

end process p_0;

Выделенные жирным курсивом слова – ключевые слова, курсивом – идентификаторы.

P_0– идентификатор, указывающий имя процесса. Inp– ранее описанный входной битовый вектор. Процесс представляет собой структуру, код внутри которой выполняется параллельно с кодами других процессов. Входной порт (или сигнал), указанный в круглых скобках после словаprocess– представляет собой «флаг»начала выполнения процесса. То есть при изменениизначения указанного сигнала, процесс начинает выполняться.

Примечание: в случае, когда сигнал не указывается или не изменяется, процесс начинает выполняться в соответствующий момент реализации кода, заключенного в нем. Также следует обратить внимание на то, что хоть процессы это параллельно реализуемые структуры, это не значит, что их отсутствие в программной модели приведет к последовательной реализации кода. В отличии от языка C, где код исполняется последовательно, строка за строкой, вVHDLвесь код реализуется в параллельном представлении. Таким образом языкVHDLможно назвать «языком параллельно реализуемого кода».

В представленном примере остается неописанным лишь код внутри процесса:

Outp(0)<= not Inp(0);

Outp(1)<= Inp(0) and Inp(1);

Outp(2)<= Inp(0) or Inp(1);

Outp(3)<= Inp(0) xor Inp(1);

Представленная часть кода описывает обычные логические функции, так на выход

Outp(0)–cпомощью оператора<=подается инвертированное значение входного сигналаInp(0).

Outp(1)– подается логическое сложение сигналовInp(0) и Inp(1).

Outp(2)– подается логическое умножение сигналовInp(0) и Inp(1).

Outp(3)– подается значение операции «Исключающее ИЛИ» для сигналовInp(0) и Inp(1).

По окончанию описания всех трех частей файл необходимо сохранить.