Миргородская 7сессия / Операционные системы / %D0%9E%D0%A1_%D0%A1%D0%93%D0%A2%D0%A3%20v5

.pdfпроцессор и память – здесь данные пересылаются из процессора в память и обратно;

процессор и устройства ввода/вывода – данные из процессора посту-

пают на ПУ через устройства (контроллер) ввода/вывода и наоборот;

обработка данных – процессор выполняет над данными арифметиче-

ские и логические операции;

управление–операцияможетзадатьпоследовательностьвыполнениякоманд.

Для выполнения команды может потребоваться последовательность, состоя-

щая из комбинации вышеперечисленных действий.

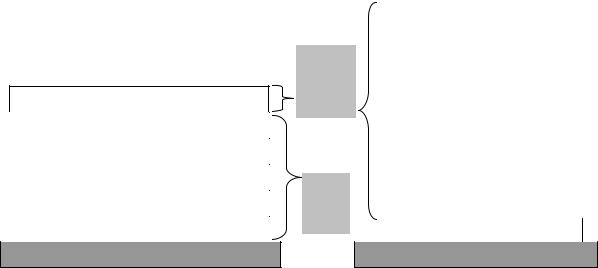

Рассмотрим гипотетический (упрощённый) компьютер (рис.7). В его процессоре есть один регистр данных, называемый аккумулятором (accumulator – AC), регистр команды (IR) и программный счетчик (PC) [3]. Каждая команда и данное имеет длину 16 бит (одно слово). При такой структуре дан-

ных удобно организовать память (адресовать) как в виде 16-битных ячеек.

Формат команды предусматривает выделение 4 бит для кода операции и 12

бит для адреса ячейки памяти, со значением которой выполняется операция.

Таким образом, всего может быть 24 = 16 различных кодов операций (каж-

дый из которых можно представить одной шестнадцатеричной цифрой). Ад-

ресоваться можно к 212 = 4096 слов памяти (8 Кбайт) (которые можно пред-

ставить трехзначным шестнадцатеричным числом).

Формат команды

Код |

операции (команды) |

Адрес |

|

0 |

3 |

4 |

15 |

|

|

Формат данных (целого числа) |

|

Знак |

|

Число |

|

0 |

1 |

|

15 |

Рис. 7. Характеристики гипотетического компьютера Пусть процессор поддерживает следующие команды (операции): 00012 (116) – загрузить значение из памяти в аккумулятор (AC); 00102 (216) – сохранить содержимое аккумулятора (AC) в памяти; 01012 (516) – добавить к аккумулятору (AC) значение ячейки памяти;

21

01102 (616) – вычесть из аккумулятора (AC) значение ячейки памяти; 10102 (A16) – инвертировать значение ячейки памяти.

На рис. 8 показаны шесть шагов необходимых для выполнения трех команд (116, 516, 216). Каждый шаг описывают три регистра (PC, AC, IR,) и два фрагмента памяти, где в ячейках с адреса 300 записаны команды программы,

с адреса 940 данные программы. Каждый нечетный шаг это цикл считывания команды, а каждый четный – цикл исполнения выбранной команды.

Память |

Регистры процессора |

Память |

|

Регистры процессора |

|||||||

300 |

|

|

|

PC |

300 |

|

|

|

|

|

PC |

1940 |

|

300 |

1940 |

|

|

301 |

|

||||

301 |

5941 |

|

|

AC |

301 |

5941 |

|

|

0003 |

|

AC |

302 |

2941… |

|

1940 |

IR |

302 |

2941… |

|

|

1 940 |

|

IR |

|

|

|

|

|

|

|

|

|

|

|

|

… |

|

|

|

|

… |

|

|

|

|

|

|

940 |

0003 |

|

|

|

940 |

0003 |

|

|

|

|

|

941 |

0002 |

|

|

Шаг 1 |

941 |

0002 |

|

|

|

|

Шаг 2 |

|

|

|

|

|

|

|

|

|

|

||

Память |

Регистры процессора |

Память |

|

Регистры процессора |

|||||||

300 |

|

|

PC |

300 |

|

|

|

|

PC |

||

1940 |

|

|

1940 |

|

|

|

|

||||

|

301 |

|

|

302 |

|

||||||

301 |

5941 |

|

0003 |

AC |

301 |

5941 |

|

|

0005 |

|

AC |

302 |

2941… |

|

5941 |

IR |

302 |

2941… |

|

|

5 941 |

|

IR |

|

|

|

|

|

|

|

|

|

|

|

|

… |

|

|

|

|

… |

|

|

|

|

|

|

|

|

|

|

|

|

3+2=5 |

|

|

|||

940 |

0003 |

|

|

|

940 |

0003 |

|

|

|

||

|

|

|

|

|

|

|

|

||||

941 |

0002 |

|

|

Шаг 3 |

941 |

0002 |

|

|

|

|

Шаг 4 |

|

|

|

|

|

|

|

|

|

|

||

Память |

Регистры процессора |

Память |

|

Регистры процессора |

|||||||

300 |

|

|

PC |

300 |

|

|

|

PC |

|||

1940 |

|

|

1940 |

|

|

|

|

||||

|

302 |

|

303 |

|

|||||||

301 |

5941 |

|

0005 |

AC |

301 |

5941 |

|

0005 |

|

AC |

|

302 |

2941… |

|

2941 |

IR |

302 |

2941… |

|

2 941 |

|

IR |

|

|

|

|

|

|

|

|

|

|

|

|

|

… |

|

|

|

|

… |

|

|

|

|

|

|

940 |

0003 |

|

|

|

940 |

0003 |

|

|

|

|

|

941 |

0002 |

|

|

Шаг 5 |

941 |

0005 |

|

|

|

|

Шаг 6 |

|

|

|

|

|

|

|

|

|

|

||

Рис.8. Пример выполнения трех двухбайтных одноадресных команд

Выполнение программы на рис.8 осуществляется следующим образом: 1. Адрес первой команды (300) хранится в программном счетчике PC.

Эта команда (она представлена шестнадцатеричным числом 1940) загружает-

ся в регистр команд (IR), а показание программного счетчика увеличивается

22

на 1. Следует отметить, что в этом процессе участвуют регистры адреса и буфера памяти, однако для упрощения они игнорируются.

2. Значние первых 4 бит (первая шестнадцатеричная цифра) регистра команд указывают на то, что нужно загрузить значение в аккумулятор. Ос-

тальные 12 бит ( три шестнадцатеричные цифры) указывают адрес 940 отку-

да загрузить данные.

3.Из ячейки 301 извлекается следующая команда (5941), после чего значение программного счетчика увеличивается на 1.

4.К содержимому аккумулятора прибавляется содержимое ячейки 941,

ирезультат снова заносится в аккумулятор.

5.Из ячейки 302 извлекается следующая команда (2941), затем значе-

ние программного счетчика увеличивается на 1.

6. Содержимое аккумулятора заносится в ячейку 941.

Этот пример показывает, что для сложения содержимого ячеек 940 и 941 необходимы три цикла команд. При более сложном наборе команд цик-

лов понадобилось бы меньше. Современные процессоры выполняют коман-

ды, в состав которых может входить несколько адресов. При этом во время цикла исполнения некоторых команд иногда выполняется несколько обраще-

ний к памяти. Вместо обращений к памяти в команде может быть задана опе-

рация ввода-вывода.

1.3. Прерывания

Прерывание представляет собой механизм, позволяющий координиро-

вать параллельное функционирование отдельных устройств ВС и реагировать на особые состояния, возникающие при работе процессора, таким образом,

прерывание – это принудительная передача управления от выполняемой про-

граммы к системе, происходящее при возникновении определённого события.

Механизм прерывания реализуется аппаратно-программными средст-

вами и включает в себя следующие этапы:

23

1.установка факта прерывания и идентификации прерывания;

2.запоминание контекста прерванного процесса; состояние процес-

са определяют: счетчик команд (PС), содержимое регистров процессора

(АС), а также может включать спецификацию режима (пользовательский или привилегированный) и др. информацию хранящуюся в регистре флага;

3.управление аппаратно передаётся подпрограмме обработки иден-

тифицированного прерывания, в простейшем случае в регистр счетчика команд заносится начальный адрес обработки, а в соответствующие регистры - инфор-

мация словосостояния;

4.сохраняется информация о прерванной программе, если это не было сделано аппаратно;

5.обработка прерывания может быть выполнена обработчиком ап-

паратного прерывания, но чаще используется обработчик ОС;

6.восстанавливаетсяинформация,относящаясякпрерванномупроцессу;

7.возврат управления прерванной программы.

При этом этапы 1-3 реализуются аппаратно, а 4-7 программно.

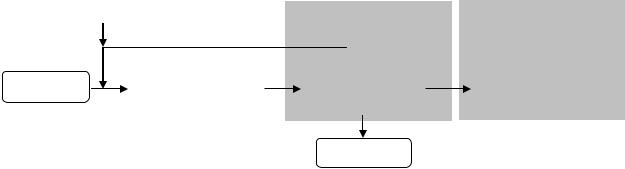

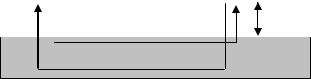

При возникновении запроса на прерывание естественный ход вычисле-

ний нарушается и управление передаётся программе обработчика возникше-

го прерывания, при этом средствами аппаратуры (с помощью механизмов стековой памяти) сохраняется адрес той команды с которой следует продол-

жить выполнение прерванной программы. После выполнения программы об-

работки прерывания управление возвращается прерванной ранее программе посредством занесения в указатель команд сохранённого адреса команды из стека (рис.9). Такая схема используется для простейших ОС, для более слож-

ных ОС при обработке прерываний используется супервизор прерываний [3].

В данном случае нет непосредственного возврата в прерванную ранее программу, прямо из подпрограммы обработки прерываний. Такая схема ис-

пользуется для многозадачных и многопользовательских ОС. Таким образом,

главными функциями механизма прерываний являются:

распознавание или классификация прерываний;

24

передача управления соответствующему обработчику прерываний;

корректное возвращение к прерванной программе.

|

|

|

Цикл выборки |

|

Цикл исполнения |

Цикл прерывания |

|||||

|

|

|

|

|

|

|

|

Запрет |

|

|

|

|

|

|

|

|

|

|

прерываний |

|

|||

|

|

|

|

|

|

|

|||||

Запуск |

|

Выборка следую- |

|

|

Исполнение |

|

Проверка наличия |

|

|||

|

щей команды |

|

|

команды |

|

прерываний |

|

||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

и их обработка |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Остановка

Рис.9 . Исполнение процессором команд с прерыванием

Прерывание, возникающее при работе ВС можно разделить: на внеш-

нее (асинхронное) и внутреннее (синхронное) и программное.

Внешние прерывания вызываются асинхронными событиями, которые происходят вне прерываемого процесса (программы) (например, прерывание таймера, внешних устройств, по нарушению питания, с пульта оператора ВС,

от другого процессора или ВС).

Внутренние прерывания вызываются событиями, которые связаны с работой процессора и являются синхронными с его операциями (например,

при нарушении адресации (в адресной части выполняемой команды указан запрещённый или несуществующий адрес, обращение к отсутствующей странице или сегменту при организации механизма внутренней памяти), при наличии в поле кода операции не используемой двоичной комбинации, при делении на 0, при переполнении или исчезновении порядка, при обнаруже-

нии ошибки чётности и ошибок в работе различных устройств аппаратуры средствами контроля (рис.10).

Существуют программные прерывания, которые возникают при вы-

полнении процессором соответствующей команды (INT), по такой команде процессор осуществляет те же действия, что и при обработке внутренних прерываний. Этот механизм введён для переключения на системные про-

граммные модули по правилам прерываний, а не подпрограмм, это обеспечи-

25

вает автоматическое переключение процессора в привилегированный режим с возможностью выполнения любых команд [3].

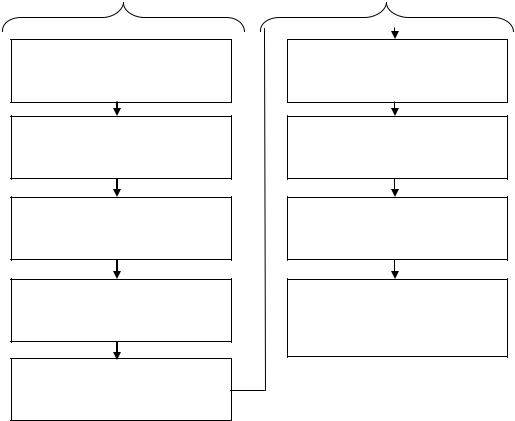

Аппаратное обеспечение |

Программное обеспечение |

|

|

|

|

|

|

|

Контроллер устройства или другой элемент АО генерирует запрос на прерывание

Процессор прекращает исполнение текущей программы

Процессор сигнализирует о получении прерывания

Процессор заносит слово состояния и программный счетчик в стек управления

В программный счетчик загружается новое значение, определяемое прерыванием

Сохранение остальной информации о состоянии процессора

Обработка прерывания

Восстановление информации о состоянии процессора

Восстановление старого слова состояния программы и содержимого программного счетчика

Рис.10. Схема обработки прерывания

В многопользовательских и многозадачных ОС применяется концепция реентерабельности. Реентерабельной называется процедура, последователь-

ность команд которой может одновременно использоваться несколькими приложениями. Для обеспечения этой концепции необходимо, чтобы про-

граммный код не был самомодифицирующимся, а локальные данные каждо-

го пользователя должны храниться отдельно друг от друга. Исполнение ре-

ентерабельной процедуры может быть приостановлено с помощью прерыва-

ния, а после возврата из него корректно продолжиться. В многопользова-

тельских и многозадачных ОС реентерабельность позволяет более эффектив-

но использовать ОП. В ней хранится только одна копия программного кода процедуры, даже если к ней обращаются несколько различных приложений.

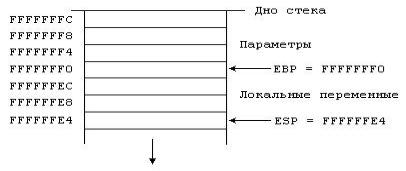

Стек — это специальным образом организованный участок памяти, ис-

пользуемый для временного хранения переменных, для передачи параметров

26

вызываемым подпрограммам и для сохранения адреса возврата при вызове процедур и прерываний. Легче всего представить стек в виде стопки листов бумаги (это одно из значений слова «stack» в английском языке) — вы може-

те класть и забирать листы бумаги только с вершины стопки. Таким образом,

если записать в стек числа 1, 2, 3, то при чтении они будут получаться в об-

ратном порядке — 3, 2, 1.

Для процессоров Intel x86 стек располагается в сегменте памяти, опи-

сываемом регистром SS, а текущее смещение вершины стека записано в ре-

гистре ESP, причем при записи в стек значение этого смещения уменьшается,

то есть стек растет вниз от максимально возможного адреса.

Такое расположение стека «вверх ногами» может быть необходимо,

например в бессегментной модели памяти, когда все сегменты, включая сег-

мент стека и сегмент кода, занимают одну и ту же область — всю память. То-

гда программа исполняется в нижней области памяти, в области малых адре-

сов, и EIP растет, а стек располагается в верхней области памяти, и ESP

уменьшается.

1.4 Архитектуры операционных систем

Архитектуру первых ОС принято называть монолитной. В вычисли-

тельных системах того времени количество оперативной памяти исчислялось килобайтами и монолитные ОС загрузившись, оставляли еще и часть свобод-

ной оперативной памяти для работы прикладных программ, написанных в

27

машинных кодах. Однако модификация таких ОС была затруднительна из-за сильного взаимного влияния (иногда не предсказуемого) функций ОС.

На принципе модульного программирования в 1970-80-х годах были разработаны слоистые ОС с иерархической организацией функций, взаимо-

действие которых возможно только между функциями находящимися на со-

седних уровнях. Управление этими функциями выполнялось в режиме ядра.

Позднее появилась микроядерная архитектура. Основа идеологии мик-

роядра, что в ядре должно быть самым главным функции ОС. Работа служб и приложений (не являющиеся критическими) хотя и основана на работе мик-

роядра, но выполняются они в пользовательском режиме. К таким приложе-

ниям относятся драйверы устройств, ФС, менеджер виртуальной памяти,

система управления безопасностью.

В архитектуре с микроядром уровни расположены вертикально, а в слоистой горизонтально (рис.11). Внешние по отношению к ядру компонен-

ты реализуются как обслуживаемые процессы. Между собой они взаимодей-

ствуют как равноправные партнёры. Обычно взаимодействие реализуется с помощью обмена сообщениями, которые передаются через микроядро. Та-

ким образом, ядро вступает в роль посредника. Оно подтверждает правиль-

ность сообщений, передаёт их от одного компонента к другому и предостав-

ляет доступ к аппаратному обеспечению [4]. Микроядро выполняет защит-

ные функции, оно не пропускает сообщения, если такой обмен не разрешён.

Например, если приложению нужно открыть файл, то оно отправляет сооб-

щение администратору ФС, если ему нужно создать новый поток в процессе,

то оно отправляет сообщение администратору процессов. Каждый из адми-

нистраторов может отправлять сообщения другим администраторам (серве-

рам, супервизорам, менеджерам) и обращаться к элементарным функциям микроядра и т.о.в одном компьютере реализуется архитектура клиент-сервер.

Достоинством архитектуры микроядра является [3]:

единообразный интерфейс;

расширяемость;

28

гибкость;

переносимость;

надёжность;

поддержка распределённых вычислительных систем;

поддержка объектно-ориентированных систем на основе исполь-

зования компонентов.

Приложения пользователей

ФС

Обмен информацией между процессами

Управление I/O и устройствами

Виртуальная память

Управление элементарными процессами

Аппаратное обеспечение

Многослойное ядро

Пользовательский режим

Режим ядра

пользователейПриложения |

.. |

устройствДрайверыI/O |

АдминистраторФС |

Администраторпроцессов |

виртуальнойр-Админпамяти |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Микроядро

Аппаратное обеспечение

Микроядро

Рис. 11.Структуры многослойного ядра и микроядра

Основными функциями микроядра, которые непосредственно зависят от аппаратного обеспечения, являются:

низкоуровневое управление памятью;

взаимодействие между процессами;

управление вводом/выводом и прерываниями.

Вначале ядро определяет свою физическую память как единое адресное пространство, которым управляет основной системный процесс. При созда-

нии новых процессов страницы первоначального адресного пространства мо-

гут передаваться или отображаться в эти новые процессы. Такая технология позволяет одновременно поддерживать несколько схем организации вирту-

альной памяти. Основной формой взаимодействия между процессами и по-

токами в ОС с микроядром являются сообщения. Сообщение включает в себя заголовок, в котором указаны идентификаторы процесса отправителя и про-

29

цесса адресата, а также тело с представленными данными. Взаимодействия между процессами основано на относящихся к этим процессам портам. Порт

– это очередь сообщений, предназначенных для определённого процесса, с

которым связан список возможностей, в котором указано, с какими процес-

сами данный процесс может обмениваться информацией. Так микроядро мо-

жет распознавать прерывания, но не обрабатывать их, вместо этого оно гене-

рирует сообщения процессу, функционирующему на пользовательском уров-

не, связанному с данным прерыванием.

В микроядре можно вынести за его пределы системы страничной орга-

низации памяти и управления виртуальной памятью.

Когда поток приложения обращается к странице, которая отсутствует в основной памяти, возникает прерывание из-за отсутствия страницы, и управ-

ление перехватывается ядром (рис.12). После этого ядро отправляет системе страничной организации памяти сообщение, в котором указывается запраши-

ваемая страница. ССОП и ядро должны взаимодействовать между собой, что-

бы выполнять действия по переносу требуемой страницы в основную память.

Страница станет доступна, ССОП отправляет приложению сообщение о том,

что оно может продолжить работу. Такая стратегия позволяет внешнему по отношению к ядру процессу отображать файлы БД в пользовательском ад-

ресном пространстве без участия ядра [3].

Приложение |

|

Система страничной |

|

|||

|

|

|

1. Ошибка из-за |

организации памяти |

|

|

3. Возобновление |

|

отсутствия страницы |

|

2. Вызов |

функции для работы |

|

|

|

|

с адресным пространством |

|||

работы |

|

|

|

|

||

|

|

|

|

|

|

|

Микроядро

Рис. 12 Принцип работы структуры с микроядром Для поддержания внешних ССОП и системы управления виртуальной

памятью микроядру достаточно трех операций.

1) Предоставление. Владелец адресного пространства может предоста-

вить некоторые свои страницы другим процессам.

30