текст лаб / lab_6

.docxЛабораторная работа № 6.

Исследование счетчиков.

Цель работы: изучение функционирования схем синхронных счетчиков. Сравнительный анализ синхронных счетчиков.

Краткие сведения об исследуемых устройствах.

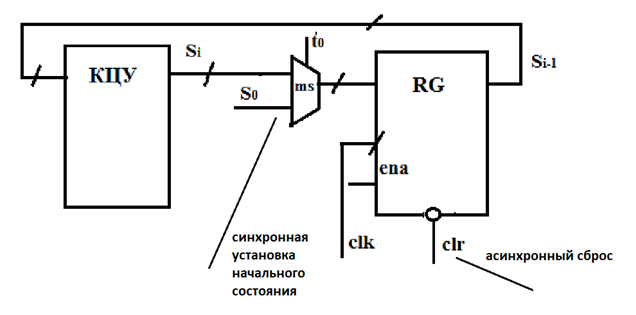

Счетчики являются простейшими конечными автоматами. К конечным автоматам относятся устройства класса ПЦУ, имеющие дополнительную петлю обратной связи, в которую включается устройство класса КЦУ. Таким образом информация, сохраняющаяся в выходном регистре в течение периода синхроимпульса (такта), преобразуется в КЦУ, и новый синхроимпульс позволяет записать преобразованную информацию. На рисунке представлена блок-схема синхронного счетчика.

Счетчики служат для подсчета поступающих синхроимпульсов или для деления частоты.

По порядку счета (смены состояний) счетчики могут быть суммирующие, вычитающие и реверсивные. В реверсивных счетчиках дополнительный сигнал реверс позволяет менять порядок счета.

По способу подачи импульсов синхронизации на разрядные триггеры счетчики могут быть синхронными или асинхронными. Основное применение в настоящее время получили синхронные счетчики.

По количеству состояний в цикле счета (коэффициенту счета) счетчики могут быть двоичными – полный цикл счета, Kсч =2n и недвоичными – неполный цикл счета, Kсч < 2n , где n – количество разрядов счетчика.

Постановка задачи. В работе предлагаются для изучения Verilog HDL – программы описания функционирования синхронных счетчиков: два варианта четырехразрядного счетчика-делителя частоты и двоичного четырехразрядного реверсивного счетчика. По функциональным диаграммам делаются выводы о работе счетчиков.

Порядок выполнения работы.

1. Создать проект, открыть Verilog HDL - файл и записать программу 6.1, отражающую функционирование 4-разрядного счетчика-делителя частоты. Откомпилировать файл.

2. Построить функциональные диаграммы работы счетчика, задав интервал синхроимпульсов 20нс, а reset сформировать коротким «0» на интервале от 0нс до 10нс при базовом уровне «1». По диаграммам сделать вывод о коэффициенте деления частоты и форме полученного сигнала синхронизации на выходе.

3. Открыть новый Verilog HDL - файл и записать программу 6.2, отражающую функционирование счетчика - делителя. Откомпилировать файл.

4. Построить функциональные диаграммы работы счетчика с такими же входными параметрами, сделать выводы о коэффициенте деления и форме полученного сигнала на выходе.

Программа 6.1

module count_div

# (parameter N=3,M=3’d4 )

(input wire clk, reset,

output reg sync=0,

output wire [N-1:0]q);

reg [N-1:0] cnt=0;

wire [N-1:0] cnt_next;

assign q=cnt;

assign cnt_next=cnt + 1;

always@(posedge clk, negedge reset)

begin

if(!reset)

cnt<=0;

else

begin

cnt<=cnt_next;

sync<=sync;

if(cnt==M-1)

begin

cnt<=0;

sync<=~sync;

end

end

end

endmodule

Программа 6.2

module count_div1

# (parameter N=4, M=10)

(input wire clk, reset,

output wire sync,

output wire [N-1:0]q);

reg [N-1:0] cnt;

wire [N-1:0] cnt_next;

assign q=cnt;

always@(posedge clk, negedge reset)

if(!reset)

cnt<=0;

else

cnt<=cnt_next;

assign cnt_next = (cnt==(M-1)) ? 0 : (cnt+1);

assign sync = (cnt==(M-1)) ? 1'b1 : 1'b0;

endmodule

5. Открыть новый Verilog HDL - файл и записать программу 6.3, отражающую функционирование 4-разрядного реверсивного счетчика с возможностями асинхронного и синхронного сброса и остановки счета. Откомпилировать файл.

6. Построить функциональные диаграммы работы счетчика, задав

интервал изменения синхроимпульсов 20нс;

интервал изменения реверса – 500нс;

асинхронный сброс - reset сформировать коротким «0» на интервале от 0нс до 10нс при базовом уровне «1»;

сигнал синхронного сброса установить короткой «1» в интервале от 80 до 110нс;

сигнал разрешения установить в «1» и вывести короткий «0» на интервале от 170 до 190нс.

Программа 6.3

module count

# (parameter N=4)

(input wire clk, reset, res, ena, rev,

output wire [N-1:0] q);

reg [N-1:0] cnt;

reg [N-1:0] cnt_next;

assign q=cnt;

always@ (posedge clk, negedge reset)

if(!reset)

cnt<=0;

else

cnt<=cnt_next;

always@*

if(res)

cnt_next=0;

else if(ena&!rev)

cnt_next=cnt + 1;

else if(ena&rev)

cnt_next=cnt-1;

else

cnt_next=cnt;

endmodule

Отчет должен содержать названия и программы работы исследованных устройств, подкрепленные проверкой на временных диаграммах.