текст лаб / lab_4

.docxЛабораторная работа № 4.

Исследование четырехразрядного сумматора.

Цель работы. Изучение функционирования комбинационного цифрового устройства, позволяющего получить арифметическую сумму двух 4-разрядных двоичных чисел. Макетирование блока сумматора АЛУ на базе FPGA CycloneV.

Краткие сведения об исследуемых устройствах.

В настоящей работе изучаются принципы построения и функционирования сумматора. Так как представление результата будет на семисегментном индикаторе, то в процессе работы будет рассмотрен кодопреобразователь, позволяющий получить из 4-разрядного двоичного кода, содержащегося в регистре результата, 7-разрядный двоичный код его отображения на индикаторах.

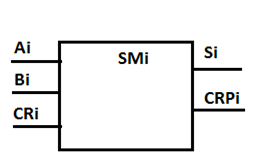

Известно, что сумматор – комбинационное цифровое устройство, предназначенное для получения арифметической суммы двух чисел, представленных в двоичном коде. Из правила сложения чисел, представляемых в позиционных системах счисления следует, что многоразрядный сумматор всегда будет состоять из одноразрядных блоков, которые будут получать сведения о разрядных значениях слагаемых и наличии (или отсутствии) переноса из предыдущего разряда. На выходах таких блоков будет получаться значение разрядной суммы в пределах основания позиционной системы и значение образовавшегося переноса в следующий разряд.

Связь между блоками всегда производится через выводы переноса, но не напрямую, а с использованием цепи быстрого переноса для минимизации задержек.

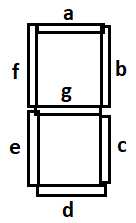

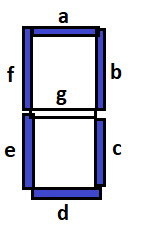

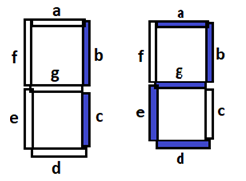

Теперь рассмотрим моделирование схемы кодопреобразователя, позволяющего выводить формируемое на 4-разрядной шине 2-ное число на семисегментный индикатор. Число при этом представляется в 16-ном кодировании. При формировании кода следует учесть, что сегменты индикатора загораются при подаче на них уровня «0». Сегменты поименуем буквами латинского алфавита a,b,c,d,e,f,g. Соответственно, a – младший разряд кода, g – старший разряд кода.

Тогда «0» нужно записать кодом «1000000»;

«1» - кодом «1111001»; «2» - кодом «0100100» и так далее.

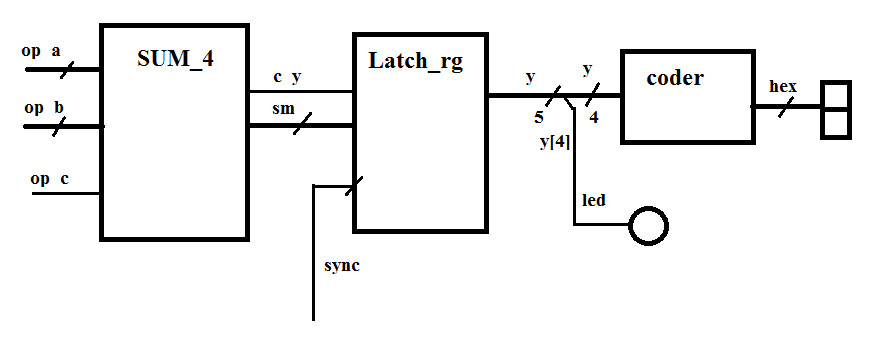

Постановка задачи. Устройство должно содержать блок 4-разрядного сумматора, блок 5-разрядного регистра результата, старший разряд которого копируется в триггер переноса и блок кодопреобразователя, позволяющего получить вывод числа на сегментный индикатор.

Структура программы рассмотрена на упражнении, предшествующем лабораторной работе.

Задание на работу в лаборатории.

Создать проект под названием summ4. При создании проекта добавить в него файл latch_rgstr из работы, заменив параметр N=4 на N=5 соответственно разрядности применяемого здесь регистра результата.

Сохранить измененный файл а проекте.

Открыть новый Verilog файл и записать в него текст кода программы 4.1 для одноразрядного сумматора.

Программа 4.1.

module sum

(input wire a,b,cr,

output wire s,crp);

assign s=(a^b)^cr;

assign crp=(a&b) | ((a^b)&cr);

endmodule

Пользуясь «Приложением 2», получить диаграммы при интервалах импульса на входе a – 20нс, на входе b – 30нс, на входе cr – 50нс.

Открыть новый Verilog-файл и записать в него Программу 4.2 для 4-разрядного сумматора. Сохранить файл, установить его старшим в иерархии и откомпилировать.

Программа 4.2

module sum_4

(input wire [3:0]a_in,b_in,

input wire cr_in,

output wire [3:0]s_out,

output wire crp_out);

wire [2:0]crp_n;

sum sum0(.a (a_in[0]),.b (b_in[0]),.cr(cr_in),.s(s_out[0]),.crp(crp_n[0]));

sum sum1(.a (a_in[1]),.b (b_in[1]),.cr(crp_n[0]),.s(s_out[1]),.crp(crp_n[1]));

sum sum2(.a (a_in[2]),.b (b_in[2]),.cr(crp_n[1]),.s(s_out[2]),.crp(crp_n[2]));

sum sum3(.a (a_in[3]),.b (b_in[3]),.cr(crp_n[2]),.s(s_out[3]),.crp(crp_out));

endmodule

Пользуясь «Приложением 2», получить диаграммы 4-разрядного сумматора. Число a установить равным 10 на интервале 30ns и, затем, на интервале 50ns равным 3. Число b установить равным 7 на интервале 50ns и, затем на интервале 50ns равным 13. Проанализируйте результат симуляции.

Открыть новый Verilog-файл и записать в него Программу 4.3 для кодопреобразователя.

Программа 4.3

module coder

(input wire [3:0] data,

output wire [6:0] seg);

reg [6:0]code;

assign seg=code;

always @*

case(data)

4'b0000: code = 7'b1000000;

4'b0001: code = 7'b1111001;

4'b0010: code = 7'b0100100;

4'b0011: code = 7'b0110000;

4'b0100: code = 7'b0011001;

4'b0101: code = 7'b0010010;

4'b0110: code = 7'b0000010;

4'b0111: code = 7'b1111000;

4'b1000: code = 7'b0000000;

4'b1001: code = 7'b0010000;

4'b1010: code = 7'b0001000;

4'b1011: code = 7'b0000011;

4'b1100: code = 7'b1000110;

4'b1101: code = 7'b0100001;

4'b1110: code = 7'b0000110;

4'b1111: code = 7'b0001110;

endcase

endmodule

Пользуясь «Приложением 2», получить диаграммы при интервалах импульса на входе data – 20нс. Проверить соответствие входных и выходных кодов на графике записанным в программе!

Открыть новый Verilog-файл и записать в него Программу 4.4 для 4-разрядного сумматора с сохранением результата в регистре, сохранением флага переноса в триггере, входящем в состав такого регистра и выводом результата на индикаторы. Сохранить файл под именем проекта, установить его старшим в иерархии и откомпилировать. Это файл верхнего уровня.

Программа 4.4

module summ_4

(input wire [3:0]op_a,op_b,

input wire op_c, sync,

output wire led,

output wire [6:0]hex);

wire [3:0]sm;

wire c_y;

wire [4:0]y;

assign led=y[4];

sum_4 block1(.a_in(op_a), .b_in(op_b), .cr_in(op_c), .s_out(sm), .crp_out(c_y));

latch_rgstr block2(.d_in({c_y,sm[3:0]}), .clk(sync), .d_out(y));

coder block3(.data(y[3:0]), .seg(hex));

endmodule

Пользуясь «Приложением 3» произвести разводку выводов схемы для работы в макете таким образом, чтобы ввод числа “a” осуществлялся с тумблеров SW9,SW8,SW7,SW6(SW9 – старший разряд), ввод числа“b” – с тумблеров SW5,SW4,SW3,SW2(SW5 – старший разряд), ввод синхронизации - с кнопки KEY(0). Вывод результата производить на сегментный индикатор 0-й, вывод значения флага переноса на светодиод – LEDR 9. После компиляции файла планировщика еще раз откомпилируйте файл верхнего уровня!

Пользуясь «Приложением 4» произвести программирование кристалла FPGA макета. На крайнем правом индикаторе должен высветиться «0». Проверить работоспособность схемы. Для этого набирать различные значения чисел “a” и “b” и нажимать крайнюю правую кнопку, имитируя подачу импульса синхронизации.

Продемонстрировать работу преподавателю.

Отчет по работе должен содержать тексты программ и диаграммы работы основных блоков устройства.