текст лаб / lab_3

.docxЛабораторная работа № 3.

Ассемблер ARM (Cortex A9)

Команды прямой и обратной загрузки.

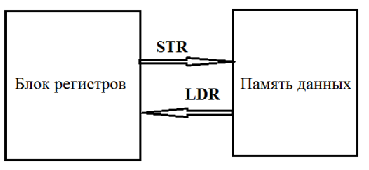

Эти команды позволяют производить обмен данными между ячейками памяти и внутренними регистрами процессора. Используемая память может содержать как массивы данных, так и быть памятью устройств, то есть быть представленной адресами внутренних портов, подключенных к простым внешним интерфейсам. Мнемоника операции прямой загрузки: LDR – Load Register, мнемоника операции обратной загрузки: STR – Store Register. Формат данных может быть: слово, полуслово или байт. Соответствующие мнемоники:

LDRB (Load Register Byte)

LDRSB (Load Register Signed Byte)

LDRH (Load Register Halfword)

LDRSH (Load Register Signed Halfword)

Отличие загрузки знакового операнда от загрузки беззнакового операнда, формат которого меньше, чем слово, в расширении (знаком или нулем).

Соответственно, для обратной загрузки

STRB (Store Register Byte)

STRH (Store Register Halfword)

Операнды:

Регистр процессора (Rd). Регистр со стороны процессора всегда следует в тесте сразу после аббревиатуры команды. Этот регистр может использоваться как приемник (в случае прямой загрузки, LDR), так и источник, STR (для обратной загрузки, STR). Использовать возможно любые свободные регистры.

Ячейка памяти. Адрес ячейки формируется на основе базового, содержащегося в регистре (Rn). Смещение (offset), прибавляемое к базовому адресу, может записываться или непосредственно, или как содержимое индексного регистра (Rm). Причем содержимое индексного регистра может задаваться со сдвигом вправо или влево на указанное число позиций (разрядов).

Надо понимать, что в качестве Rd , Rn и Rm могут использоваться любые регистры общего назначения.

Примеры:

LDR R2, [R6, # -20] – загрузка в R2 по адресу, записанному в R6, минус 20

LDR R3, [R6, R7]

LDR R5, [R6, R8, LSL# 2]

(LSL – Logic Shift Left, LSR – Logic Shift Right)

LDR R5, MEMLOC === LDR R5, [R15, # offset] – загрузка в R5 по адресу метки

LDR R5, =MEMLOC – загрузка в R5 адреса метки. (При этом компилятор помещает этот адрес в ячейку памяти данных, следующую за последней задействованной программой в этой области).

STR R5, [R2]

Относительно формирования адреса ячейки в регистрах различают три основных способа адресации.

В первом случае, как в приведенных выше примерах формируемый на шине адрес состоит из содержимого регистров, которое не изменяется. База остается и смещение остается.

Во втором случае содержимое регистров складывается, выводится на шину и копируется в базу.

Пример

LDR R2, [R6, R8, LSL#2]!

R6 <- [R6] + [R8 x 4] до получения содержимого в R2

В третьем случае базовый адрес выводится на шину, а затем заменяется на новый, с добавленным смещением.

Пример

LDR R5, [R6], #0x20

R6 <- [R6] + 32 – после получения содержимого в R2.

Команды прямой и обратной загрузки могут работать с цепочками регистров. В этом случае состояние базы изменяется с последующим или предыдущим инкрементом (декрементом). Регистр базы записывается первым, в фигурных скобках перечисляются используемые регистры процессора.

Пример

LDMIA R3!, {R4, R6-R8, R10}

Загрузка в перечисленную цепочку регистров с начального адреса, записанного в R3. После загрузки содержимое R3 увеличивается на 20.

STMDB SP!, {R1, R3-R5} === PUSH {R1, R3-R5}

Занесение в стек по адресу указателя с предыдущим декрементом.

LDMIA SP!, {R1, R3-R5} === POP {R1, R3-R5}

Работа № 1, ассемблер.

Ознакомиться с текстом программы – Прогр. 1.

На рабочем столе открыть редактор GVim: Меню приложений – Инструменты – Gvim.

Создать новый файл (Файл – Новый), войти в режим вставки (Insert).

Набрать текст Прогр.1. (номера команд и комментарии не набирать!)

Сохранить файл, создав любую папку проекта в своем каталоге, присвоив ему расширение s. Например: part1_1.s

Подключить макет. Открыть Altera Monitor Program (Файловая система – opt – altera15.0 – University Program – Monitor Program – bin – altera monitor program.)

Выбрать File > New Project.

Далее выбрать имя папки, определить имя проекта в соответствии с тем, как Вы его назвали. Выбрать архитектуру ARM Cortex-A9. Клик Next.

Выбрать DE1-SoC Computer, Next.

Выбираем Assembly Program. Окно вставок не инициализируем! Next.

В следующем окне добавляем созданный файл. Next.

Specify system parameters. Убеждаемся, что подключение макета произведено (надпись в верхнем окне), если надпись отсутствует, просим помощи преподавателя. Обращаем внимание, что в строке Terminal device должно быть выбрано <none>. Next.

Диапазоны используемой памяти оставляем без изменения. Finish.

Осуществить загрузку кодов в макет, дав положительный ответ на запрос “Download System”.

Произвести компиляцию файла и загрузку (Actions> Compile&Load).

Перед началом выполнения программы просмотреть содержимое ячеек памяти, заявленных под адресом ARR, используя опцию Memory (под окном программы). Вернуться на Disassembly.

Выполнять программу пошагово, нажимая на верхнюю иконку с дугообразной желтой стрелкой. Перед выполнением команды считывания с тумблеров в каждом цикле устанавливать новое число на тумблерах макета. На каждом шаге просматривать содержимое основных регистров исполненной команды прямой загрузки (LDR). Для команд обратной загрузки (STR) - адреса и содержимое ячеек памяти. Изменение состояния регистра подсвечивается в отладчике красным цветом (режим disassembly). Перед выполнением каждой команды STR переходить к просмотру памяти (режим memory) Результаты заносить в таблицу 1.

Прогр. 1.

.text

.global _start

1._start: LDR R0, ADR1 // базовый адрес порта тумблеров в R0

2. LDR R1, =ARR // базовый адрес пространства под массив

3. MOV R2, #5 // счетчик элементов массива

4. M1: LDR R3, [R0] // считывание числа с тумблеров в R3

5. STR R3, [R1], #4 // копирование числа в массив

6. SUBS R2, #1 // уменьшение состояния счетчика массива

7. BNE M1 // продолжение считывания, счетчик не «0»

8. LDMDB R1!, {R4-R8} // копирование массива в регистры

9.stop: B stop // останов, бесконечный цикл

ADR1: .word 0xFF200040

ARR: .space 20

.end

Таблица 1.

№ команды |

Состояние используемого регистра |

Адрес используемой ячейки памяти |

Содержимое ячейки памяти |

1. |

R0 =……….. |

|

|

|

|

|

|

Отчет должен содержать текст программы, таблицу состояний регистров и ячеек памяти и выводы о возможности обмена исследуемого процессора с памятью (обмен с ячейками, с регистрами порта, обмен одиночными данными, загрузка цепочек данных)